UNIVERSITÉ DU QUÉBEC

MÉMOIRE

PRÉSENTÉ À

L'UNIVERSITÉ DU QUÉBEC À CHICOUTIMI

COMME EXIGENCE PARTIELLE

DE LA MAÎTRISE EN SCIENCE APPLIQUÉES

PAR

MICHEL LANGLAIS, ING.

INTÉGRATION D'INSTRUCTIONS DATA-PARALLÈLES DANS LE LANGAGE PSC ET

COMPILEATION POUR PROCESSEUR SIMD (INTEL SSE)

AVRIL 2013

## RÉSUMÉ

Il existe des instructions data-parallèles dans les processeurs modernes. Ces instructions permettent d'effectuer la même opération sur plusieurs données différentes en parallèle. Présentement, il est difficile de programmer des logiciels qui utilisent ces instructions data-parallèles avec les solutions existantes. Nous avons donc exploré l'utilisation d'un langage destiné à la programmation des circuits parallèles comme les FPGA (Field Programmable Gate Array) pour fabriqué un logiciel qui permet d'utiliser ces instructions data-parallèles de manière simple et efficace. Un langage de haut niveau pour la programmation des FPGA, le langage psC- Parallel and Synchronous C- a été choisi. Sa syntaxe proche du C, son paradigme entièrement parallèle et la disponibilité du code source ont justifié ce choix.

Il y a plusieurs années, les gens pensaient qu'aujourd'hui l'optimisation ne serait plus aussi importante qu'elle l'était pour eux. Ils disaient que la quantité de mémoire et la puissance de calculs des processeurs ferait en sorte que le gain en temps ne vaudrait pas l'effort de programmation nécessaire pour programmer du code optimisé. Maintenant, nous savons que ce n'est pas le cas. Les processeurs ont certes eu un gain de performance important, mais les tâches qu'ils accomplissent nécessitent de plus en plus de puissance de calculs et de mémoire. Aujourd'hui, une bonne partie de la puissance de calculs s'obtient par l'utilisation des instructions data-parallèles disponibles dans les processeurs modernes. Pour inclure ces instructions data-parallèles dans un logiciel, il n'y a pas beaucoup d'alternatives disponibles.

Ce travail a consisté à réaliser un compilateur complet pour machine SIMD. Une nouvelle syntaxe permettant de supporter les instructions data-parallèles a été définie et intégrée à celle du langage psC. L'algorithme de génération de code assembleur pour les instructions data-parallèles de type SSE d'Intel a été implémenté et testé. Finalement, trois applications ont été programmées et les performances de rapidité d'exécution comparées à diverses méthodes classiques de programmation.

Les résultats montrent que les performances obtenu par le langage psC est toujours situé entre celui obtenu par un expert codant en langage assembleur et celui obtenu par les compilateurs C et C++. Ceci correspond à ce qui était désiré.

En conclusion, ce travail de recherche a démontré qu'il était possible d'utiliser un langage HL-HDL (High Level Hardware Description Language) pour générer du code qui bénéficie des instructions data-parallèles. Le gain en performance de l'implémentation psC est présenté pour tous les cas étudié, et se rapproche de l'implémentation assembleur qui est le maximum atteignable.

## REMERCIEMENTS

Je tiens à remercier tout particulièrement ma conjointe qui a été présente pour moi tout au long de cette grande aventure. Elle n'a jamais cessé de m'encourager et de croire en moi.

Je remercie également mes enfants qui ont été compréhensifs quand je devais me concentrer pour travailler au lieu d'être avec eux.

Enfin, je remercie mon directeur de maîtrise pour ses bons conseils et sa patience.

## TABLE DES MATIÈRES

|                                                             |    |

|-------------------------------------------------------------|----|

| 1 INTRODUCTION .....                                        | 1  |

| 1.1 Parallélisme .....                                      | 1  |

| 1.1.1 Parallélisme de bit .....                             | 2  |

| 1.1.2 Le parallélisme d'instructions .....                  | 4  |

| 1.1.3 Le parallélisme de données .....                      | 5  |

| 1.1.4 Le parallélisme de tâches .....                       | 6  |

| 1.2 Architectures parallèles .....                          | 7  |

| 1.2.1 Instruction unique donnée unique .....                | 7  |

| 1.2.2 Instructions multiples donnée unique .....            | 8  |

| 1.2.3 Instruction unique données multiples .....            | 9  |

| 1.2.4 Instructions multiples données multiples [IMDM] ..... | 10 |

| 1.3 Architecture des ordinateurs personnels .....           | 11 |

| 1.3.1 Jeu d'instruction MMX .....                           | 11 |

| 1.3.2 Jeu d'instruction 3DNow! .....                        | 13 |

| 1.3.3 Jeux d'instructions SSE et successeurs .....          | 13 |

| 1.4 Programmation .....                                     | 14 |

| 1.4.1 Paradigme impératif .....                             | 15 |

| 1.4.2 Paradigme évènementiel .....                          | 15 |

| 1.4.3 Paradigme data-parallèles .....                       | 16 |

| 1.4.4 Paradigme fonctionnel .....                           | 17 |

| 1.5 Problématique .....                                     | 17 |

| 1.5.1 Le langage assembleur .....                           | 17 |

| 1.5.2 Les fonctions intrinsèques .....                      | 21 |

| 1.5.3 Optimisation par le compilateur .....                 | 24 |

| 1.5.4 Besoin .....                                          | 25 |

| 2 ALGORITHMES .....                                         | 27 |

| 2.1 Classification des algorithmes .....                    | 27 |

| 2.1.1 Algorithmes synchrones .....                          | 28 |

| 2.1.2 Algorithmes légèrement synchrones .....               | 29 |

|       |                                            |    |

|-------|--------------------------------------------|----|

| 2.1.3 | Algorithmes asynchrones.....               | 34 |

| 2.2   | Instructions souhaitables .....            | 35 |

| 2.2.1 | Le type « index » .....                    | 35 |

| 2.2.2 | Instructions d'affectations.....           | 36 |

| 2.2.3 | Instructions de sectionnement.....         | 37 |

| 2.2.4 | Instructions conditionnelles .....         | 37 |

| 2.2.5 | Instructions de réductions .....           | 38 |

| 2.2.6 | Instructions vectorielles .....            | 39 |

| 2.3   | Solution selon valarray.....               | 39 |

| 2.3.1 | Construction.....                          | 40 |

| 2.3.2 | Instructions d'affectation .....           | 40 |

| 2.3.3 | Instructions de sectionnement.....         | 41 |

| 2.3.4 | Instructions conditionnelles .....         | 42 |

| 2.3.5 | Instructions de réductions .....           | 43 |

| 2.3.6 | Instructions vectorielles.....             | 43 |

| 2.4   | Solution selon Blitz++ .....               | 46 |

| 2.4.1 | Construction.....                          | 46 |

| 2.4.2 | Affectation et extraction de valeurs ..... | 46 |

| 2.4.3 | Instructions d'affectations.....           | 48 |

| 2.4.4 | Instructions de sectionnement.....         | 48 |

| 2.4.5 | Instructions conditionnelles .....         | 49 |

| 2.4.6 | Instructions de réductions .....           | 49 |

| 2.4.7 | Instructions vectorielles .....            | 50 |

| 2.5   | Solution proposé.....                      | 52 |

| 2.5.1 | Construction.....                          | 52 |

| 2.5.2 | Affectation et extraction de valeurs ..... | 54 |

| 2.5.3 | Instructions de sectionnement.....         | 56 |

| 2.5.4 | Instructions conditionnelles .....         | 57 |

| 2.5.5 | Instructions de réduction.....             | 58 |

|                     |                                                                              |    |

|---------------------|------------------------------------------------------------------------------|----|

| 2.5.6               | Instructions vectorielles .....                                              | 58 |

| 3 RÉALISATION ..... | 63                                                                           |    |

| 3.1                 | Choix du langage .....                                                       | 63 |

| 3.2                 | Historique du langage psC .....                                              | 64 |

| 3.3                 | Description de la syntaxe du psC .....                                       | 65 |

| 3.3.1               | Composant .....                                                              | 65 |

| 3.3.2               | Ports et signaux .....                                                       | 66 |

| 3.3.3               | Type .....                                                                   | 68 |

| 3.3.4               | Fonctions .....                                                              | 68 |

| 3.3.5               | Fonctions intrinsèques .....                                                 | 69 |

| 3.3.6               | Opérateur .....                                                              | 69 |

| 3.3.7               | Transtypage .....                                                            | 71 |

| 3.4                 | Ajout des instructions data-parallèles .....                                 | 71 |

| 3.4.1               | Ajout de la grammaire data-parallèles sur les tableaux .....                 | 71 |

| 3.4.2               | Ajout du type index .....                                                    | 72 |

| 3.4.3               | Ajout de fonctions spécialisées data-parallèles .....                        | 72 |

| 3.5                 | Compilation .....                                                            | 73 |

| 3.5.1               | Validation .....                                                             | 75 |

| 3.6                 | Génération de code assembleur .....                                          | 75 |

| 3.6.1               | Architecture MMX et SSE .....                                                | 75 |

| 3.6.2               | Principe .....                                                               | 77 |

| 3.6.3               | Patron : index .....                                                         | 78 |

| 3.6.4               | Patron : chargement d'une donnée .....                                       | 79 |

| 3.6.5               | Patron : chargement de données non-alignées .....                            | 81 |

| 3.6.6               | Patron : sauvegarde d'une donnée .....                                       | 81 |

| 3.6.7               | Patron : minimum d'entiers de huit bits non signés .....                     | 81 |

| 3.6.8               | Patron : multiplication de points flottants à trente-deux bits .....         | 81 |

| 3.6.9               | Patron : multiplication de points flottants à soixante-quatre bits .....     | 82 |

| 3.6.10              | Patron : addition de points flottants à soixante-quatre bits .....           | 82 |

| 3.6.11              | Patron : somme de points flottant trente-deux bits, résultats scalaire ..... | 83 |

|                     |                                                                                  |            |

|---------------------|----------------------------------------------------------------------------------|------------|

| 3.6.12              | Patron : multiplication matricielle de points flottant soixante-quatre bits..... | 84         |

| 3.6.13              | Patron : transformation d'un scalaire de huit bits non signé en un vecteur ....  | 85         |

| <b>4 RÉSULTAT</b>   | .....                                                                            | <b>87</b>  |

| 4.1                 | Présentation des tests.....                                                      | 87         |

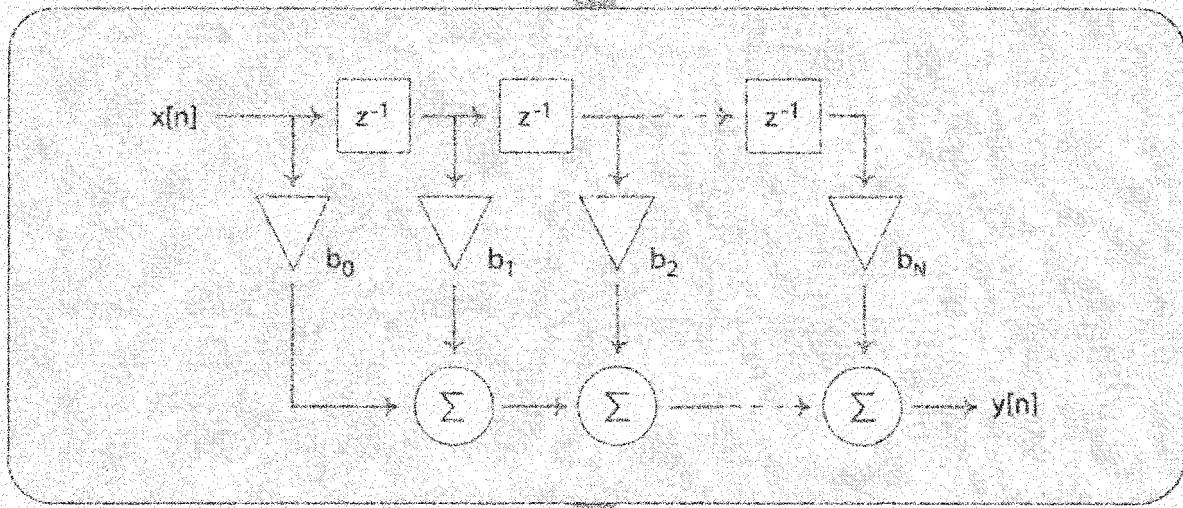

| 4.2                 | Filtre à réponse impulsionale finie.....                                         | 88         |

| 4.2.1               | Implantation C .....                                                             | 90         |

| 4.2.2               | Implantation Assembleur.....                                                     | 90         |

| 4.2.3               | Implantation psC.....                                                            | 95         |

| 4.2.4               | Résultats.....                                                                   | 96         |

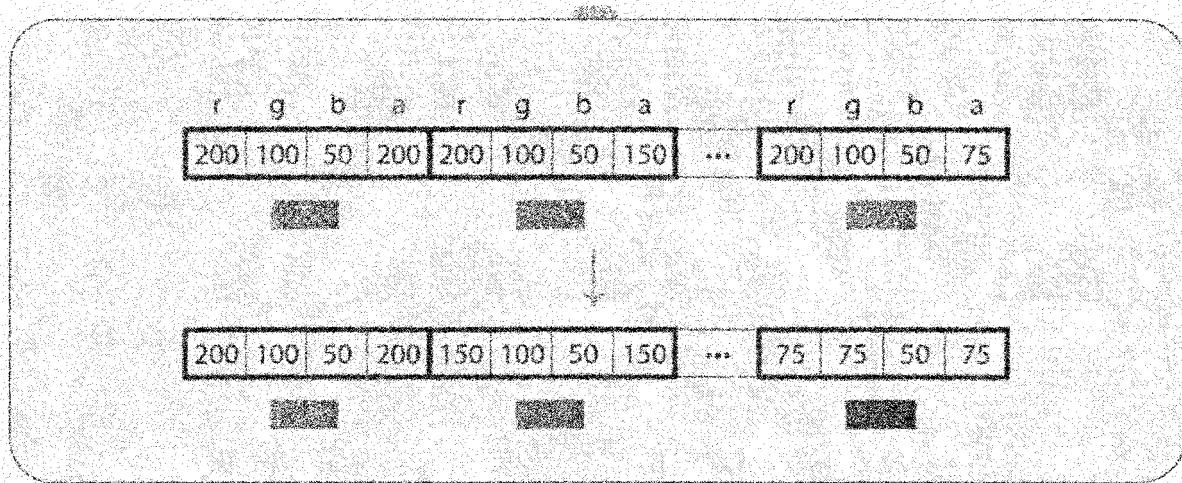

| 4.3                 | Saturation alpha.....                                                            | 97         |

| 4.3.1               | Implantation C .....                                                             | 98         |

| 4.3.2               | Implantation Assembleur.....                                                     | 99         |

| 4.3.3               | Implantation psC.....                                                            | 100        |

| 4.3.4               | Résultats.....                                                                   | 101        |

| 4.4                 | Multiplication matricielle.....                                                  | 101        |

| 4.4.1               | Implantation C .....                                                             | 103        |

| 4.4.2               | Implantation Assembleur.....                                                     | 103        |

| 4.4.3               | Implantation psC.....                                                            | 104        |

| 4.4.4               | Résultats.....                                                                   | 105        |

| <b>5 CONCLUSION</b> | .....                                                                            | <b>107</b> |

## TABLE DES FIGURES

|                                                                                         |     |

|-----------------------------------------------------------------------------------------|-----|

| Figure 1-1: Calcul de bit .....                                                         | 3   |

| Figure 1-2: Pipeline d'instructions à cinq étapes .....                                 | 4   |

| Figure 1-3: Calcul parallèle .....                                                      | 5   |

| Figure 1-4: Tâches parallèles .....                                                     | 6   |

| Figure 1-5: Instruction Unique Donnée Unique .....                                      | 8   |

| Figure 1-6: Instructions Multiples Donnée Unique .....                                  | 9   |

| Figure 1-7: Instruction Unique Données Multiples .....                                  | 10  |

| Figure 1-8: Instructions Multiples Données Multiples .....                              | 11  |

| Figure 1-9: Registres MMX .....                                                         | 12  |

| Figure 1-10: Registres SSE .....                                                        | 14  |

| Figure 2-1: Algorithme synchrone .....                                                  | 29  |

| Figure 2-2: Algorithme légèrement synchrone - opération à priori .....                  | 31  |

| Figure 2-3: Algorithme légèrement synchrone - opération à postériori .....              | 32  |

| Figure 2-4: Algorithme légèrement synchrone - opérations à priori et à postériori ..... | 33  |

| Figure 2-5: Algorithme asynchrone .....                                                 | 34  |

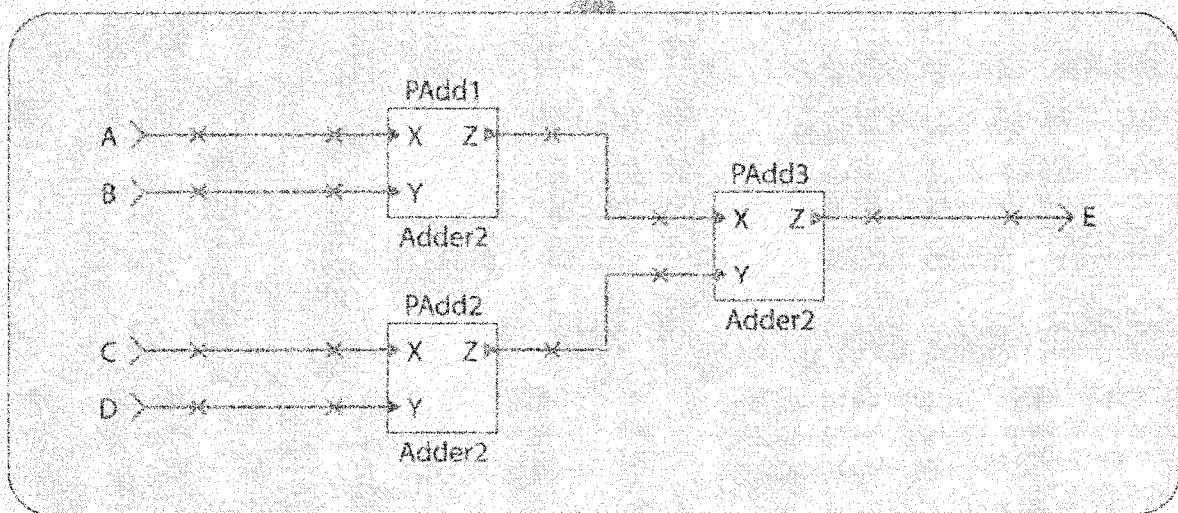

| Figure 3-1: psC – additionneur à quatre nombres en graphique .....                      | 65  |

| Figure 3-2: Algorithme synchrone .....                                                  | 74  |

| Figure 3-3: Registres MMX et SSE .....                                                  | 76  |

| Figure 4-1: Filtre à réponse impulsionnelle finie .....                                 | 89  |

| Figure 4-2: Exemples de saturation alpha .....                                          | 98  |

| Figure 4-3: Exemples de multiplication matricielle .....                                | 102 |

## TABLE DES CODES

|                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------|----|

| Code 1-1 : Addition d'un vecteur d'entier en assembleur.....                                        | 21 |

| Code 1-2 : Addition d'un vecteur d'entier en langage C en utilisant les fonctions intrinsèques..... | 24 |

| Code 1-3 : Addition d'un vecteur d'entier en langage C.....                                         | 24 |

| Code 1-4 : Boucle optimisée par le compilateur d'Intel.....                                         | 25 |

| Code 1-5 : Boucle non optimisée par le compilateur d'Intel.....                                     | 25 |

| Code 2-1 : Algorithme synchrone.....                                                                | 28 |

| Code 2-2 : Algorithme légèrement synchrone.....                                                     | 29 |

| Code 2-3 : Utilisation du type index.....                                                           | 36 |

| Code 2-4 : Instruction de communication.....                                                        | 36 |

| Code 2-5 : Instruction de sectionnement.....                                                        | 37 |

| Code 2-6 : Instruction conditionnelle.....                                                          | 38 |

| Code 2-7 : Instruction de réduction.....                                                            | 38 |

| Code 2-8 : Instruction vectorielle.....                                                             | 39 |

| Code 2-9 : Instruction vectorielle en langage C.....                                                | 39 |

| Code 2-10 : Valarray – construction.....                                                            | 40 |

| Code 2-11 : Valarray – affectation et extraction d'un scalaire.....                                 | 41 |

| Code 2-12 : Valarray – Instructions de sectionnement.....                                           | 42 |

| Code 2-13 : Valarray – Instructions conditionnelles.....                                            | 42 |

| Code 2-14 : instructions vectorielles de valarray.....                                              | 44 |

| Code 2-15 : Blitz++ – construction.....                                                             | 46 |

| Code 2-16 : Blitz++ – affectation et extraction d'un scalaire.....                                  | 47 |

| Code 2-17 : Blitz++ - index.....                                                                    | 48 |

| Code 2-18 : Instructions conditionnelles de Blitz++.....                                            | 48 |

| Code 2-19 : Blitz++ – Instruction conditionnelle.....                                               | 49 |

| Code 2-20 : Blitz++ – instruction vectorielle.....                                                  | 51 |

| Code 2-21 : psC – déclaration sans initialisation.....                                              | 53 |

| Code 2-22 : psC – Déclaration avec initialisation via un scalaire.....                              | 53 |

| Code 2-23 : psC – Déclaration avec initialisation via un tableau de même taille.....                | 54 |

| Code 2-24 : psC – Déclaration avec initialisation via un tableau plus grand.....                    | 54 |

| Code 2-25 : psC – Déclaration avec initialisation via un tableau plus petit.....                    | 54 |

| Code 2-26 : psC – Extraction d'un scalaire.....                                                     | 55 |

| Code 2-27 : psC – Extraction d'un tableau.....                                                      | 55 |

| Code 2-28 : psC – Affectation.....                                                                  | 56 |

| Code 2-29 : psC – Opération de sectionnement.....                                                   | 57 |

| Code 2-30 : psC – Opération ternaire.....                                                           | 57 |

|                                                                                                    |     |

|----------------------------------------------------------------------------------------------------|-----|

| Code 2-31 : psC – Opération équivalente à l’opération ternaire. ....                               | 58  |

| Code 3-1 : psC – additionneur. ....                                                                | 66  |

| Code 3-2 : psC – additionneur à quatre nombres en texte. ....                                      | 67  |

| Code 3-3 : psC – transtypage. ....                                                                 | 71  |

| Code 3-4 : psC – type index explicite. ....                                                        | 72  |

| Code 3-5 : psC – index type. ....                                                                  | 73  |

| Code 3-6 : psC – patron index. ....                                                                | 79  |

| Code 3-7 : psC – Patron chargement de données alignées. ....                                       | 80  |

| Code 3-8 : psC – Patron minimum. ....                                                              | 81  |

| Code 3-9 : psC – Patron multiplication parallèle valeur points flottant de simple précision. ....  | 82  |

| Code 3-10 : psC – Patron multiplication parallèle valeur points flottant de double précision. .... | 82  |

| Code 3-11 : psC – Patron addition parallèle valeur points flottant de simple précision. ....       | 82  |

| Code 3-12 : psC – sum(A[i][j]) + B[i]. ....                                                        | 83  |

| Code 3-13 : psC – B[i] + sum(A[i][j]). ....                                                        | 83  |

| Code 3-14 : psC – Patron somme de points flottant à simple précision. ....                         | 84  |

| Code 3-15 : psC – Patron multiplication matriciel de points flottant à double précision. ....      | 85  |

| Code 3-16 : psC – Masque pour transformation d’entier huit bits en vecteur. ....                   | 85  |

| Code 3-17 : psC – Patron transformation d’entier huit bits en vecteur. ....                        | 86  |

| Code 4-1 : Filtre RIF en C. ....                                                                   | 90  |

| Code 4-2 : Alignement de valeurs pondérées. ....                                                   | 91  |

| Code 4-3 : Initialisation registre pour RIF. ....                                                  | 92  |

| Code 4-4 : Filtre RIF en assembleur. ....                                                          | 95  |

| Code 4-5 : Filtre RIF en psC. ....                                                                 | 96  |

| Code 4-6 : Saturation alpha en C. ....                                                             | 99  |

| Code 4-7 : Saturation alpha en assembleur. ....                                                    | 100 |

| Code 4-8 : Saturation alpha en psC. ....                                                           | 100 |

| Code 4-9 : Multiplication matricielle en C. ....                                                   | 103 |

| Code 4-10 : Multiplication matricielle en assembleur. ....                                         | 104 |

| Code 4-11 : Multiplication matricielle en psC. ....                                                | 105 |

## TABLE DES TABLEAUX

|                                                                                  |     |

|----------------------------------------------------------------------------------|-----|

| Tableau 1-2 : Classification des architectures des ordinateurs selon Flynn ..... | 7   |

| Tableau 1-3 : Jeux d'instructions IUDM supportés par les compilateurs .....      | 24  |

| Tableau 2-1 : Valarray – instructions de réduction .....                         | 43  |

| Tableau 2-2 : Valarray – instructions vectorielles .....                         | 45  |

| Tableau 2-3 : Blitz++ – Instructions de réduction .....                          | 50  |

| Tableau 2-4 : Blitz++ – liste partielle des instructions vectorielles .....      | 51  |

| Tableau 2-5 : psC – Instructions de réduction .....                              | 58  |

| Tableau 2-6 : psC – Opérations unaires .....                                     | 59  |

| Tableau 2-7 : psC – Opérations binaires .....                                    | 60  |

| Tableau 2-8 : psC – Fonctions data-parallèles .....                              | 61  |

| Tableau 2-9 : psC – Opérations multimédia .....                                  | 62  |

| Tableau 3-1 : types du psC .....                                                 | 68  |

| Tableau 3-2 : Fonctions prédéfinies .....                                        | 69  |

| Tableau 3-3 : Opérateurs de psC .....                                            | 70  |

| Tableau 3-4 : Opérations data-parallèles implémentées .....                      | 73  |

| Tableau 3-5 : Opérations MMX et SSE utilisés .....                               | 77  |

| Tableau 4-1 : mises en œuvre de validation .....                                 | 87  |

| Tableau 4-2 : Résultats filtre FIR .....                                         | 97  |

| Tableau 4-3 : Résultats saturation alpha .....                                   | 101 |

| Tableau 4-4 : Résultats multiplication matricielle .....                         | 106 |

| Tableau 5-1 : Sommaire des résultats .....                                       | 108 |

## 1

## INTRODUCTION

Il y a plusieurs années, les gens du domaine de l'informatique pensaient qu'aujourd'hui l'optimisation ne serait plus aussi importante qu'elle l'était pour eux. Ils disaient que la quantité de mémoire et la puissance de calculs des processeurs ferait en sorte que le gain en temps ne vaudrait pas l'effort de programmation nécessaire pour programmer du code optimisé. Maintenant, nous savons que ce n'est pas le cas. Les processeurs ont certes eu un gain de performance important, mais les tâches qu'ils accomplissent nécessitent de plus en plus de puissance de calculs et de mémoire. Nous ne citerons que quelques exemples, qui n'étaient tout simplement pas imaginable voilà quelques années à peine: le traitement d'images à haute résolution en temps réel, le traitement de la voix et la simulation physique d'écoulement des fluides.

### 1.1 Parallélisme

Pendant plusieurs années, le gain de performance provenait principalement de la cadence des processeurs. Maintenant le gain de performance provient principalement du parallélisme. La définition du parallélisme selon le dictionnaire Larousse est : « Technique d'accroissement des performances d'un système informatique fondée sur l'utilisation

simultanée de plusieurs processeurs ». Selon ce même dictionnaire, la définition de processeur est : « Organe destiné, dans un ordinateur, à interpréter et exécuter des instructions ». Dans cet ouvrage, nous désignerons un processeur comme une unité de traitement (UT). Le mot processeur quant à lui, désignera ce qui est généralement reconnu par tous comme étant la composante électrique complète avec toutes les unités de traitement qui le compose.

### 1.1.1 Parallélisme de bit

Le parallélisme de bit consiste à traiter plusieurs bits simultanément dans une opération. Les premiers processeurs constitué de relais étaient de seulement 1 bit. C'est-à-dire qu'ils ne traitaient qu'un seul bit à la fois. Avec l'avenue des transistors, les unités de traitement pouvant traiter plusieurs bits en simultanés sont apparus, doublant le nombre de leur prédecesseurs à chaque évolution. L'apparition des ordinateurs personnels s'est faite avec des unités de traitement à 8 bits pour la compagnie IBM et les ordinateurs compatibles. La compagnie Apple à utiliser des unités de traitement de 32 bits. Présentement, les unités de traitement de 32 bit utilisés dans les ordinateurs personnels laissent graduellement la place à ceux à 64 bits.

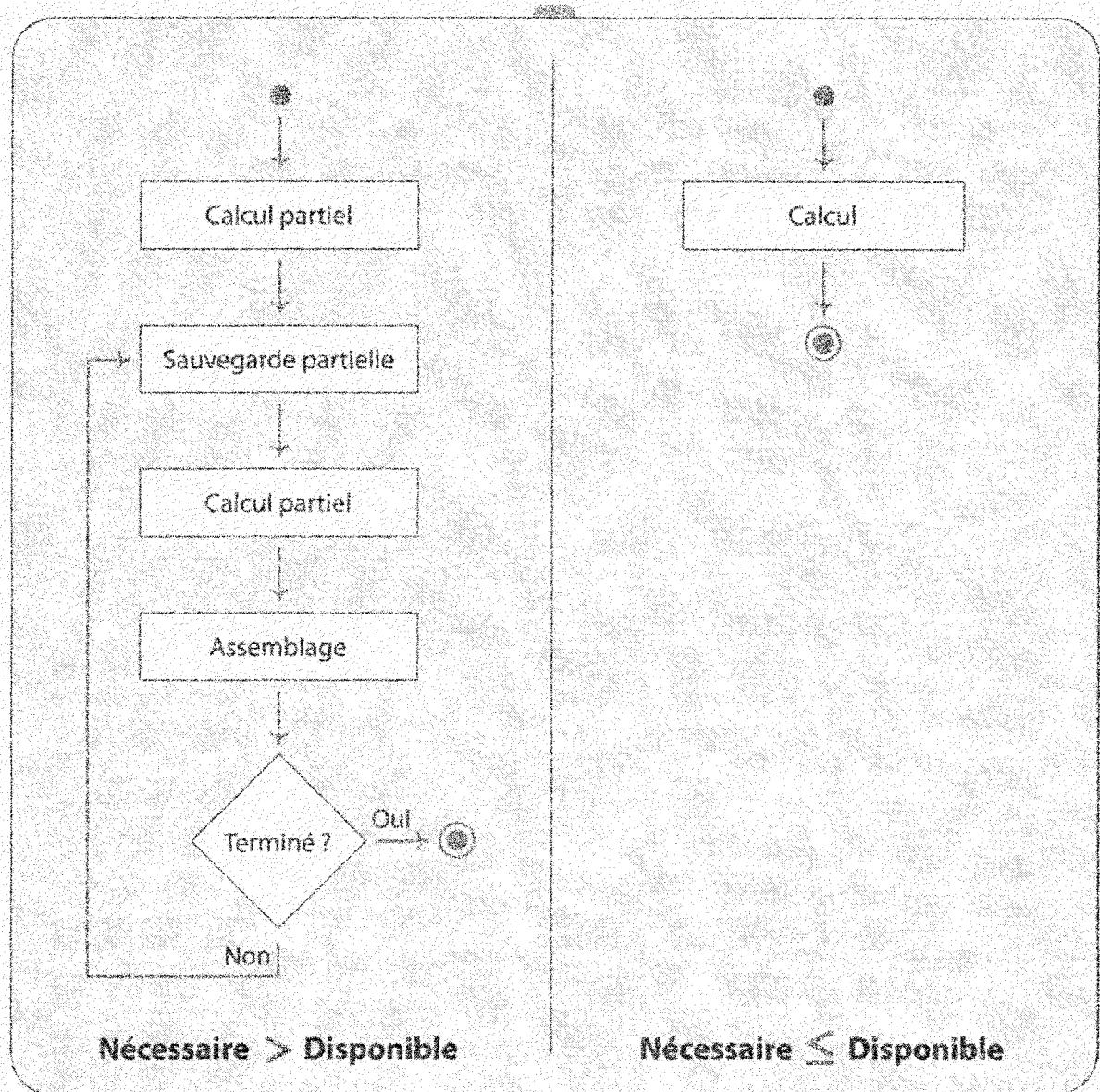

Lorsqu'un calcul nécessite plus de bits que ce que l'unité de traitement en offre, il est nécessaire d'effectuer des calculs partiels et d'assembler les résultats partiels pour obtenir le résultat final désiré. Inutile de mentionner que ceci implique un coût en temps de calcul qui serait non nécessaire si l'unité de traitement possédait un nombre de bits suffisant pour effectuer le calcul en une seule opération.

Les programmeurs ne peuvent rien faire pour améliorer ce parallélisme, il est disponible où il ne l'est pas. La Figure 1-1 démontre la logique utilisée en fonction du nombre de bits nécessaires pour effectuer un calcul versus le nombre disponible dans le registre.

Figure 1-1: Calcul de bit.

### 1.1.2 Le parallélisme d'instructions

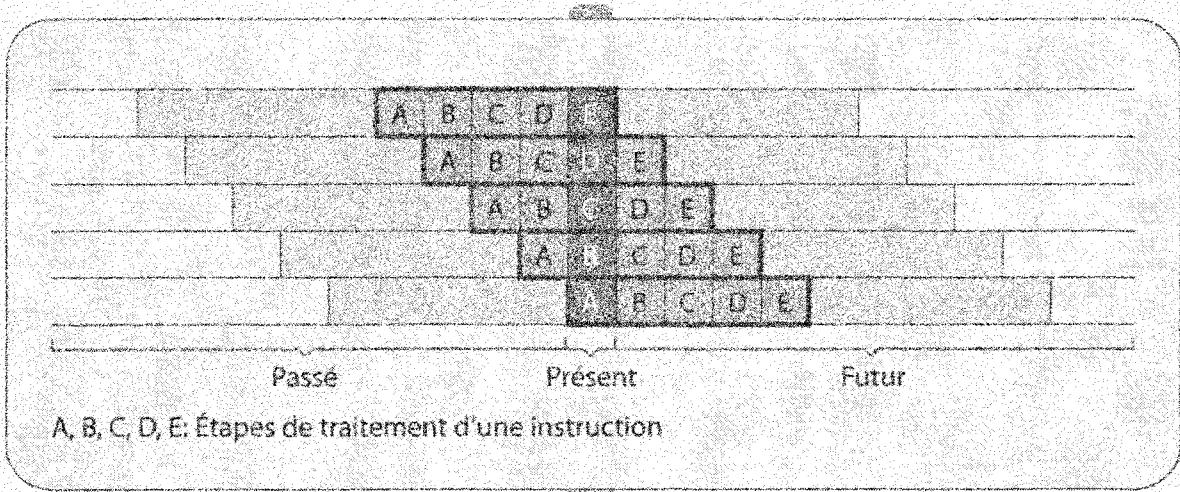

Une instruction est une commande donnée à un processeur. Une instruction peut résulter en une ou plusieurs opérations. Lors de l'exécution d'une opération, il y a plusieurs étapes impliquées dans le processeur. Le nombre d'étapes et l'ordre de celles-ci dépend de l'architecture matérielle du processeur. Cependant, il est possible d'exécuter plusieurs de ces étapes en parallèle, c'est-à-dire en simultané, dans un pipeline. La taille du pipeline a atteint 31 étapes dans les processeurs Pentium D. La Figure 1-2 montre un exemple de pipeline à 5 étapes.

Figure 1-2: Pipeline d'instructions à cinq étapes.

Les programmeurs ont peu de contrôle sur ce parallélisme. Tout ce qu'ils peuvent faire est d'ordonner les instructions pour aider le processeur à effectuer son travail de parallélisme.

### 1.1.3 Le parallélisme de données

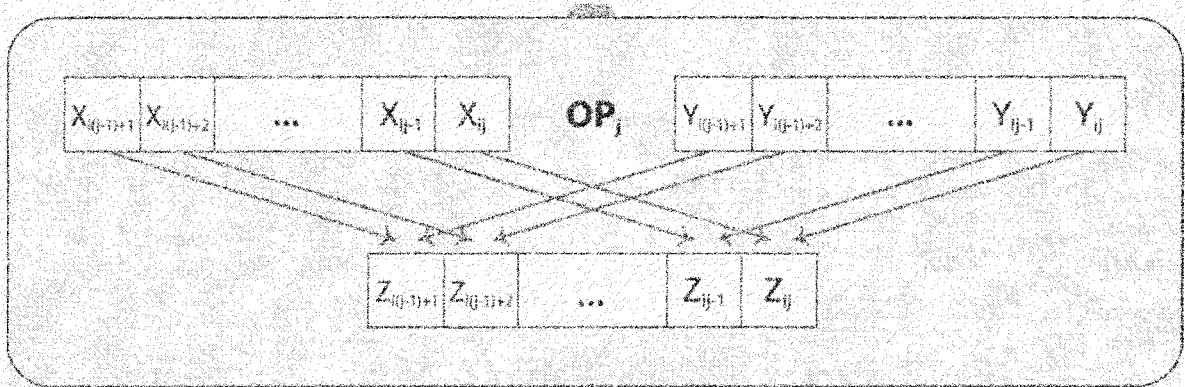

Dans plusieurs algorithmes, particulièrement les calculs vectoriels (basé sur des vecteurs), une instruction est appliquée à plusieurs données différentes. Historiquement, il était nécessaire d'appliquer la même instruction à chaque donnée. Lorsque la même instruction peut être appliquée pour effectuer le même travail sur plusieurs données, on effectue du parallélisme de données, ou data-parallélisme. Ceci réduit le nombre d'instructions par un facteur égal au nombre de données traités simultanément lorsque l'instruction data-parallèle est utilisée. Par exemple, une instruction data-parallèle qui traite quatre données en simultané réduit d'un facteur quatre le nombre d'instructions nécessaire, comparativement à une architecture qui nécessite une instruction pour chaque donnée.

Les programmeurs sont fortement impliqués dans ce parallélisme. Nous traiterons comment plus en détail dans le reste de cet ouvrage. La Figure 1-3 montre la logique d'un calcul parallèle de  $j$  opérations data-parallèles qui traitent  $i$  données à chaque instruction.

Figure 1-3: Calcul parallèle.

#### 1.1.4 Le parallélisme de tâches

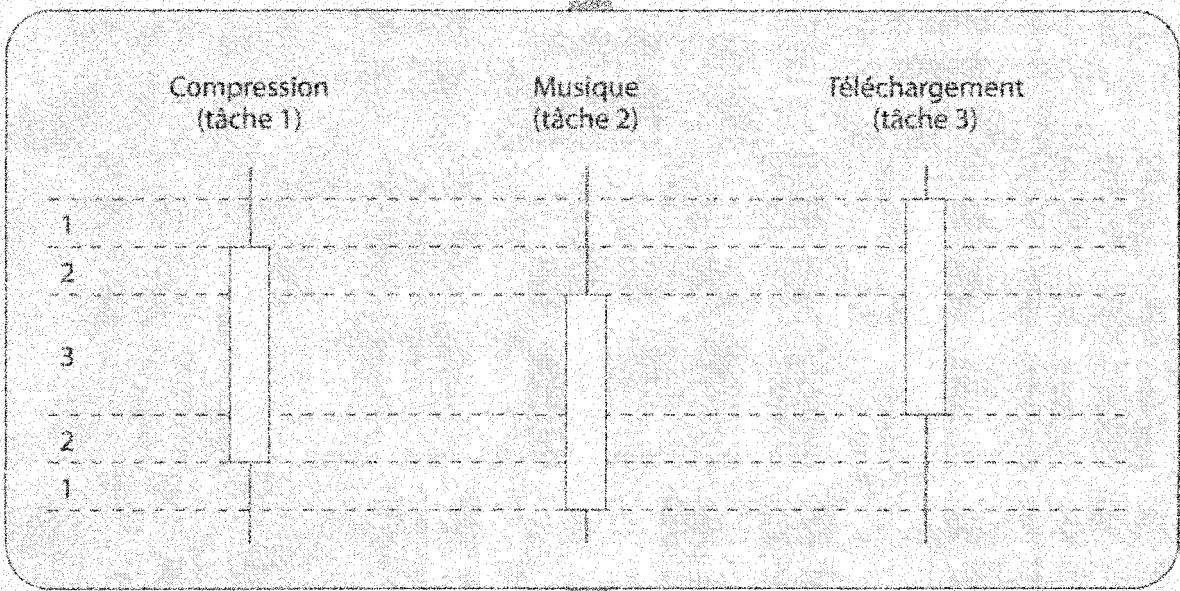

Lorsque l'on parle de parallélisme, c'est naturellement celui auquel les gens pensent. Il consiste en l'accomplissement de plusieurs tâches distinctes simultanément. Par exemple, effectuer la compression d'un fichier, jouer de la musique et effectuer un téléchargement. La Figure 1-4 le démontre graphiquement.

Figure 1-4: Tâches parallèles.

Les programmeurs utilisent peu ce type de parallélisme. Lorsqu'ils le font, il est nécessaire de gérer le parallélisme et toutes les synchronisations nécessaires de manière explicite. Lorsqu'implémenté sur un seul processeur, ce type de parallélisme ne produit aucun gain de performance.

## 1.2 Architectures parallèles

Il existe plusieurs architectures matérielles qui permettent d'effectuer des opérations parallèles. Michael J. Flynn a inventé une classification des architectures des ordinateurs (Flynn, 1972). Le Tableau 1-1 indique les types existant dans cette classification et elles sont décrites plus en détails ici-bas.

| Mnémonique | Terme Complet                           |

|------------|-----------------------------------------|

| IUDU       | Instruction Unique Donnée Unique        |

| IMDU       | Instructions Multiples Donnée Unique    |

| IUDM       | Instruction Unique Données Multiples    |

| IMDM       | Instruction Multiples Données Multiples |

Tableau 1-1 : Classification des architectures des ordinateurs selon Flynn.

### 1.2.1 Instruction unique donnée unique

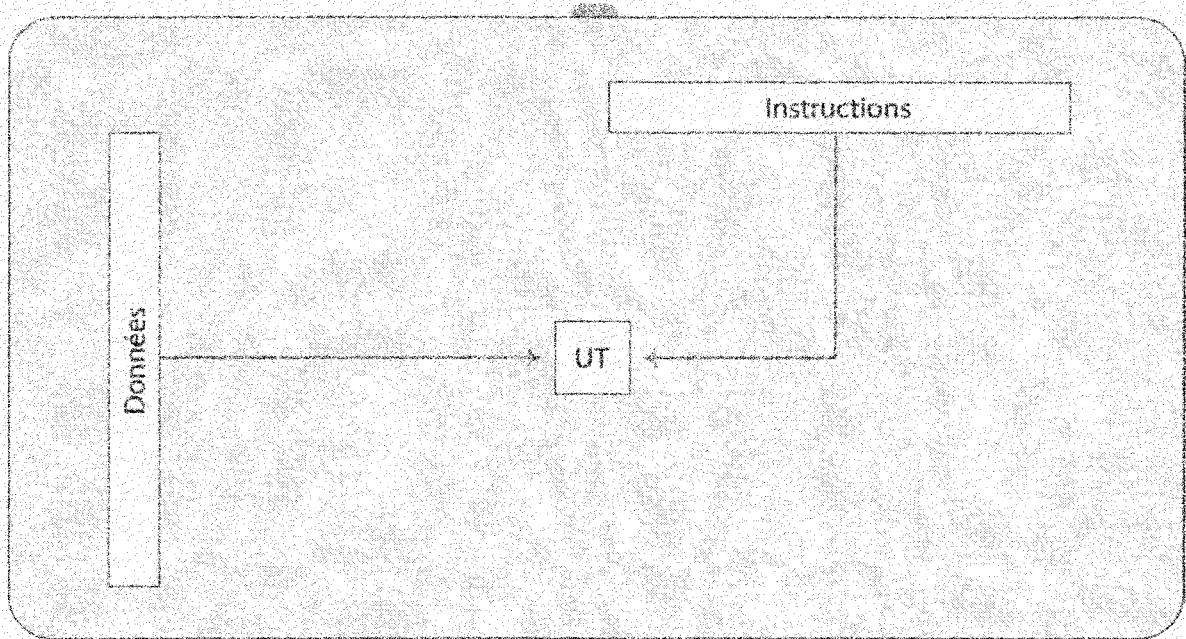

Une architecture IUDU consiste en un seul flux d'instruction qui opère sur un seul flux de données. À chaque pas, une seule instruction opère sur une seule donnée. Ce modèle est la base de l'informatique. À l'exception de quelques instructions, les processeurs à un seul cœur (unité de traitement) adhèrent à ce modèle inventé par John Von Neumann à la fin des années quarante (Wikipedia, 2010). Un algorithme qui s'exécute de manière IUDU est dit séquentiel ou serial. Il peut contenir du parallélisme de bits et du parallélisme d'instructions. La Figure 1-5 en fait l'illustration.

Figure 1-5: Instruction Unique Donnée Unique.

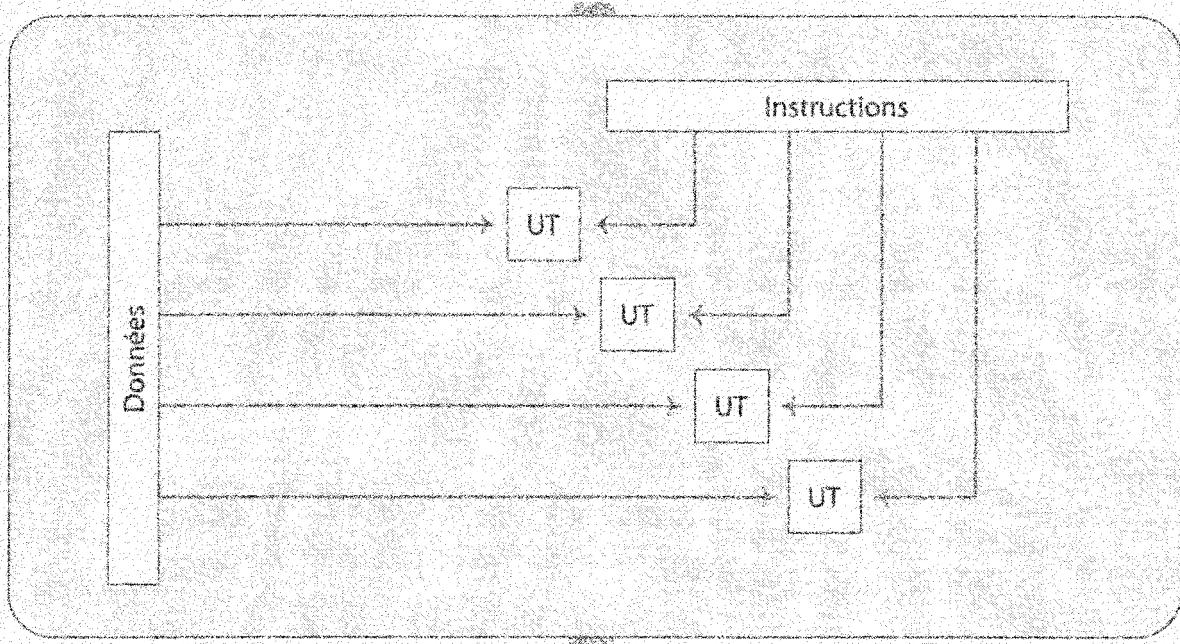

### 1.2.2 Instructions multiples donnée unique

Une architecture IMDU consiste en plusieurs flux d'instructions qui opèrent tous sur le même flux de données. À chaque pas, plusieurs instructions opèrent sur la même donnée. Par exemple, on peut vouloir additionner le nombre B au nombre A et également soustraire de nombre B du nombre A. Chacune de ces tâches sont distinctes et peuvent être effectuées en simultanés. La Figure 1-6 en fait l'illustration. Ce modèle est peu utilisé car peu de problèmes exigent ce type d'architecture parallèle.

Figure 1-6: Instructions Multiples Donnée Unique.

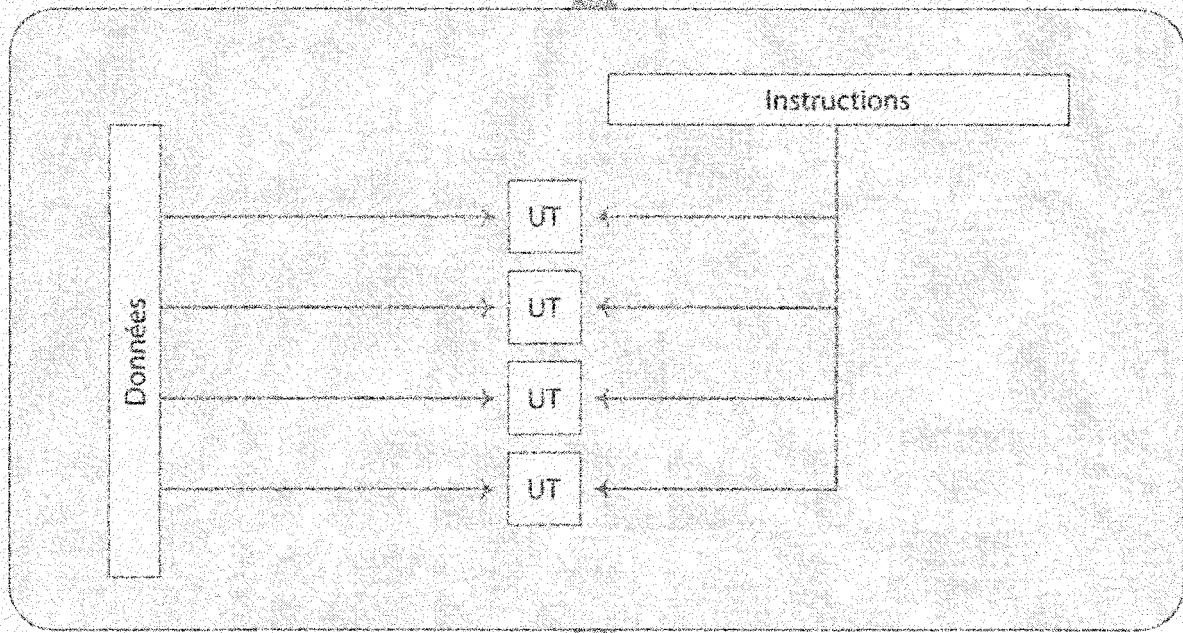

### 1.2.3 Instruction unique données multiples

Une architecture IUDM consiste en un seul flux d'instruction qui opère sur plusieurs flux de données. À chaque pas, une seule instruction opère sur plusieurs données différentes. Par exemple, on peut vouloir additionner le nombre B au nombre A et le nombre D au nombre C. Chacune de ces tâches sont distinctes et peuvent être effectuées en simultanés. La Figure 1-7 en fait l'illustration. Ce modèle est utilisé dans tous les algorithmes qui traitent des vecteurs de données comme le traitement d'images, l'analyse et le traitement des signaux numériques, les comparaisons, etc. On nomme ceci le data-parallélisme.

Figure 1-7: Instruction Unique Données Multiples.

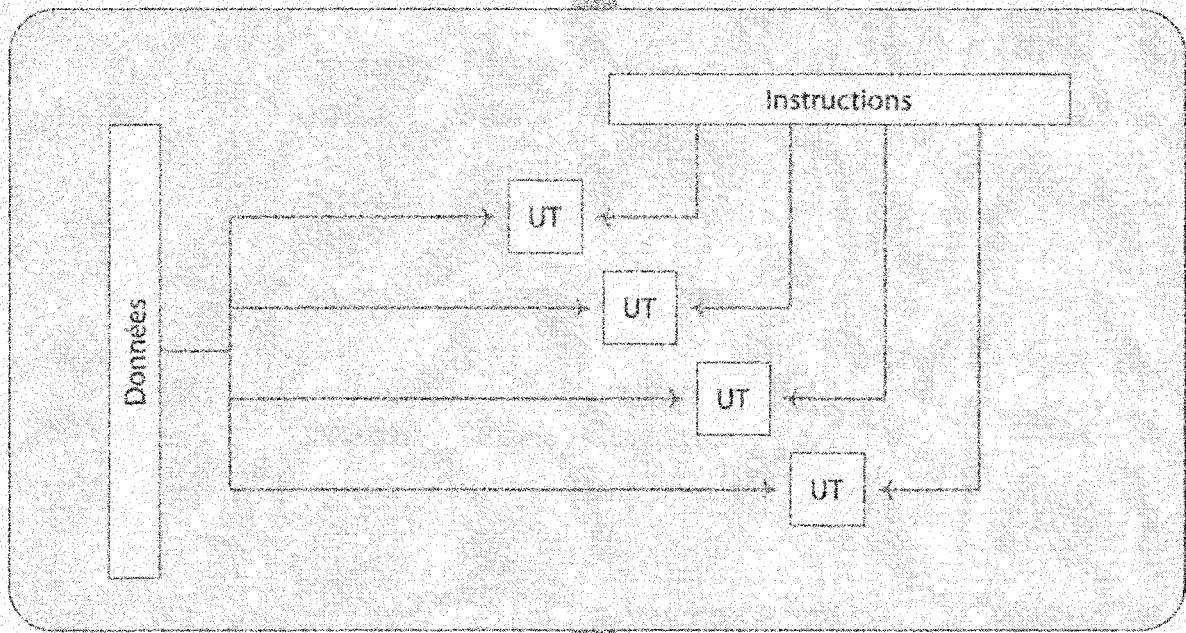

#### 1.2.4 Instructions multiples données multiples (IMDM)

Une architecture IMDM consiste en plusieurs flux d'instructions qui opèrent sur plusieurs flux de données. À chaque pas, plusieurs instructions opèrent sur plusieurs données différentes. Par exemple, on peut vouloir décoder un fichier encrypté et jouer de la musique. Ce modèle est utilisé pour effectuer plusieurs tâches non liées entre elles en simultané. La Figure 1-8 en fait l'illustration. Souvent cette architecture est réalisée avec des ordinateurs multiprocesseurs, qu'ils soient ou non sur un même support matériel. Chaque unité de traitement est en soi un IUDU.

Figure 1-8: Instructions Multiples Données Multiples.

### 1.3 Architecture des ordinateurs personnels

Selon la classification vue précédemment, les architectures des ordinateurs personnels et des superordinateurs sont classé soit en tant que IMDM ou IUDM. Les processeurs disponibles dans les ordinateurs personnels, fabriqué principalement par les compagnies Intel et AMD, possèdent plusieurs cœurs et sont donc de types IMDM. Chacun de ces cœurs est de type IUDU. Autrement dit, les cœurs sont séquentiels. Cependant, ils possèdent des jeux instructions data-parallèles qui permettent certaines opérations IUDM.

#### 1.3.1 Jeu d'instruction MMX

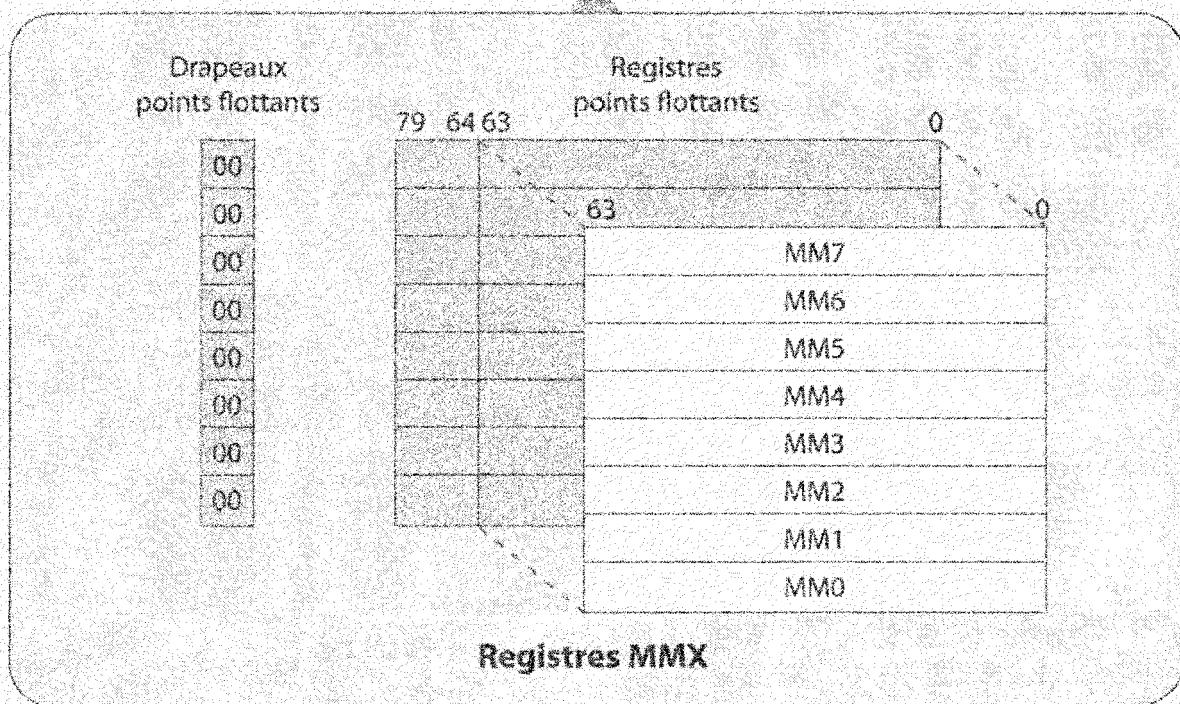

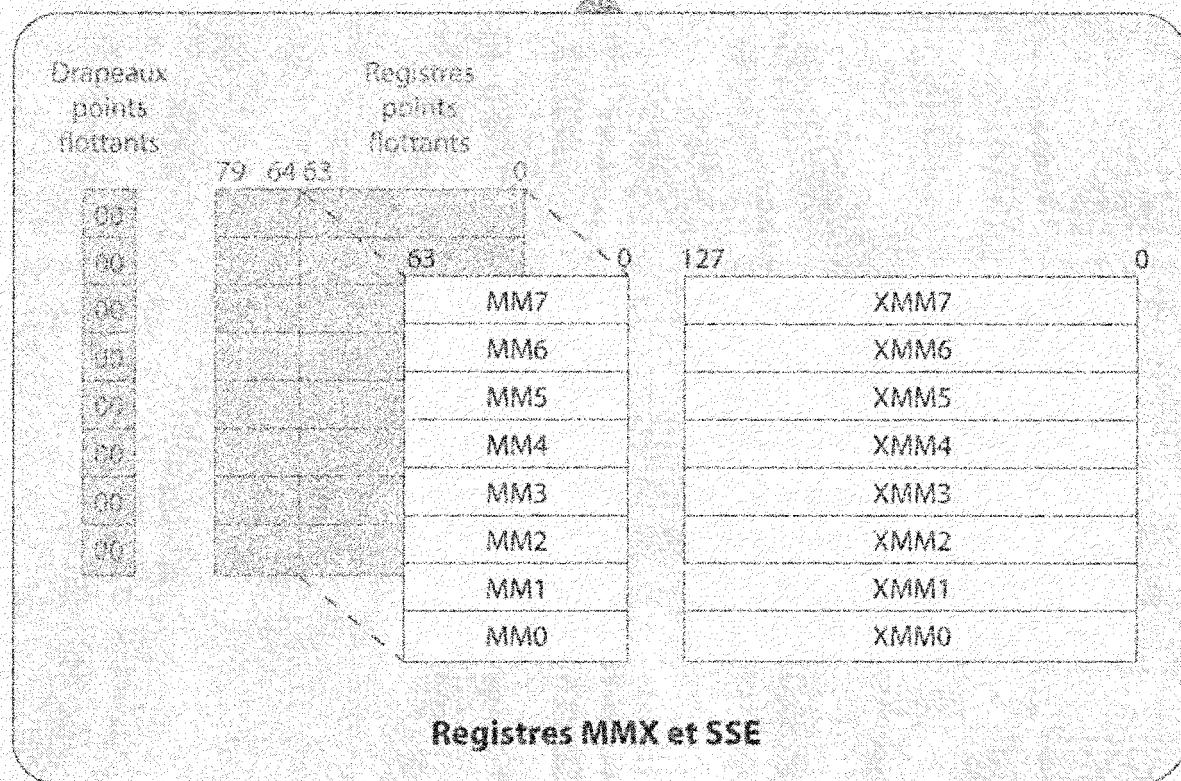

Le jeu d'instruction MMX est le premier jeu d'instruction data-parallèle disponible pour les ordinateurs personnels dans les processeurs Intel en 1996. Les instructions utilisent les mantisses des huit registres de calcul en points flottant (voir la Figure 1-9) pour

effectuer des opérations d'arithmétique entière condensé. Il est possible de travailler sur une valeur de 64 bits, deux valeurs de 32 bits, quatre valeurs de 16 bits ou huit valeurs de 8 bits.

Figure 1-9: Registres MMX.

Ce jeu d'instruction comprend 57 instructions divisé en sept catégories : arithmétique de base, comparaison, conversion, logique, décalages de bits, transfert de données et gestion.

Le but de ce jeu d'instructions est d'augmenter les performances des applications multimédia et scientifiques. Toutes les applications utilisant beaucoup de calculs sur des entiers peuvent bénéficier de ce jeu d'instruction.

### 1.3.2 Jeu d'instruction 3DNow!

Suite à l'introduction du jeu d'instruction MMX par la compagnie Intel, la compagnie AMD a fabriqué le jeu d'instruction 3DNow! Disponible en 1998. Ce jeu d'instruction ajoute 21 instructions, dont certaines permettent d'effectuer des calculs en points flottant condensés (deux variables de 32 bits). Tout comme le jeu d'instruction MMX, ce jeu d'instruction partage les registres avec ceux du calcul en points flottant.

Tout comme le jeu d'instruction MMX et les jeux d'instructions qui lui succèderont, le but est d'améliorer les performances des applications effectuant beaucoup de calculs, peu importe qu'ils soient en valeur entières ou en points flottants.

### 1.3.3 Jeux d'instructions SSE et successeurs

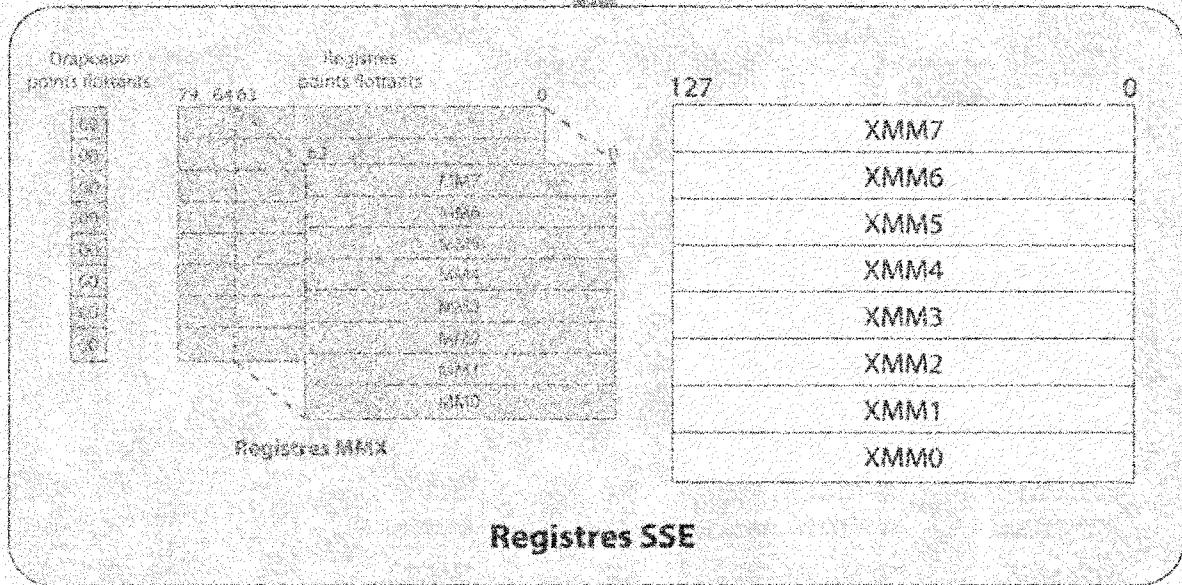

En réplique à l'addition des opérations à points flottant condensé, la compagnie a développé le jeu d'instruction SSE, disponible depuis 1999. Il consiste en 70 instructions, traitant principalement de calculs en points flottant condensés. Contrairement aux jeux d'instructions précédent, huit nouveaux registres de 128 bits ont été ajoutés (voir la Figure 1-10).

Figure 1-10: Registres SSE.

Suite au jeu d'instruction SSE, plusieurs autres jeux d'instructions ont été ajoutés : SSE2, SSE3, SSSE3, SSE4.1 et SSE4.2. Ces jeux d'instructions ajoutent de nouvelles opérations en valeur entières et en point flottant utilisant les huit registres ajoutés avec le jeu d'instruction SSE.

#### 1.4 Programmation

Pour effectuer une tâche sur un ordinateur, il est nécessaire de lui indiquer comment faire. Le seul langage qu'un processeur comprend est son langage machine. Le langage machine est très difficile à comprendre par les humains. Pour pallier à ce problème, le langage assembleur est né. Il fait correspondre une instruction assembleur à une instruction machine. Malgré le fait qu'un humain peut plus aisément comprendre ce langage que le langage machine, il reste très complexe. Plusieurs langages de programmation ont donc vu le jour, ayant tous pour but de permettre de coder plus simplement pour un humain. Les

instructions dans un langage de programmation haut niveau peuvent, et c'est souvent le cas, se traduisent en plusieurs instructions assembleurs ou machine. Chaque langage apporte des avantages (et inconvénients) sur certains aspects de la programmation. Ils peuvent être classés en plusieurs paradigmes, en fonction de la manière dont ils gèrent le parallélisme.

#### 1.4.1 Paradigme impératif

Ce paradigme se caractérise par le fait que les programmes s'exécutent selon l'ordre des instructions qui le compose et qui changent son état. Dans cette catégorie, on retrouve la programmation procédurale, la programmation structurée et la programmation objet. Le C, le C++, le Pascal, le Delphi, le C# et plusieurs autres langages en sont des exemples.

Dans ce paradigme, il incombe aux programmeurs d'indiquer explicitement le parallélisme et la synchronisation. Certains langages ont des mots clé ou des fonctions qui aident les programmeurs, mais rien qui est fait de manière complètement transparente.

#### 1.4.2 Paradigme événementiel

Ce paradigme se caractérise par le fait que les programmes s'exécutent selon l'ordre des événements qu'il reçoit. Un programme de ce paradigme se caractérise par deux parties distinctes : la détection des événements et le traitement des événements. Les diagrammes de Pétri (Petri, 1962) sont un moyen de décrire ce paradigme qui peut être interprété comme étant contrôlé par le flux de données. La plupart des bibliothèques d'interfaces usagers entrent dans cette catégorie. Souvent, les langages impératifs sont utilisés pour fabriquer les programmes événementiels.

Il est possible que le langage ou l'outil de génération de code permette que chaque événement soit traité de manière parallèle aux autres événements. Durant le traitement d'un événement, il incombe aux programmeurs d'indiquer explicitement le parallélisme. La synchronisation entre les événements est prise en charge. Cependant, la synchronisation qui doit être effectuée à l'intérieur du traitement d'un événement doit être faite explicitement par le programmeur.

#### 1.4.3 Paradigme data-parallèles

Ce paradigme se caractérise par le fait que le parallélisme s'exprime en fonction d'opérations parallèles sur des structures de données.

Dans ce paradigme, il incombe aux programmeurs d'indiquer explicitement la synchronisation. Cependant, le parallélisme est fait de manière complètement transparente. Les programmes data-parallèles sont écrits dans des langages spécialisés, et ne sont souvent disponible que pour une, ou un petit nombre, d'architectures matérielles. On peut citer High Performance Fortran (HPF) (Koelbel, 2010), C//, C\*, Cilk, IDOLE, L, PARALLAXIS-III, Scientific Vector Language (SVL) (Santavy et Labute, 2010) et ZPL (University of Washington, 2010) comme exemples. Selon l'analyse de (Hammarlund et Lisper, 1993), les langages data-parallèles et les techniques d'exécutions parallèles sont principalement des extensions de langages séquentiels existant.

Le data-parallélisme est la forme principale de parallélisme dans les calculs scientifiques (biologie, chimie, géologie, ingénierie, etc.).

#### 1.4.4 Paradigme fonctionnel

Ce paradigme se caractérise par le fait que les langages fonctionnels ne comportent que des affectations et des appels de fonctions. Une fonction peut être appelée aussitôt que tous ses arguments sont connus. On peut citer Sisal (Streams and Iteration in a Single Assignment Language), LISP (McCarthy, 1960) et NESL (Blelloch, 2010) comme exemples de langages fonctionnels.

La synchronisation et le parallélisme peuvent être pris en charge implicitement ou laissé à la charge du programmeur.

### 1.5 Problématique

Comme indiqué en 1.1, les logiciels demandent de plus en plus de puissance de calculs. Cette puissance de calcul peut provenir de l'utilisation des instructions data-parallèles disponibles dans les processeurs modernes (voir 1.3). Cependant, il existe peu de moyens d'utiliser ces instructions de manière simple et efficace. Trois techniques existent pour inclure ces instructions data-parallèles dans un programme. Il est possible d'utiliser le langage assembleur, les fonctions intrinsèques en langage C ou laisser le compilateur effectuer le travail.

#### 1.5.1 Le langage assembleur

Pour coder en langage assembleur, il est nécessaire d'avoir une connaissance approfondie des jeux d'instructions des processeurs. Il faut comprendre le fonctionnement de la mémoire vive, des mémoires caches et des registres. Il faut être en mesure d'effectuer l'alignement des données en mémoire et d'éviter le dépassement de capacité lors du

traitement des tableaux. Le dépassement de capacité arrive lorsque la taille des tableaux n'est pas un multiple du nombre de données qui entrent dans un registre. Lors de calculs importants, il faut effectuer des transferts mémoire ou utiliser la pile comme une zone de stockage temporaire car le nombre de registre disponible ne sera pas suffisant.

L'utilisation des instructions data-parallèles en assembleur ont les mêmes problématiques que tout autre code en langage assembleur, mais demandent d'aligner les données en mémoire à seize octets en plus. Autrement dit, il faut que l'adresse des données soit divisible par seize sans reste.

Le Code 1-1 montre comment l'addition des valeurs d'un vecteur d'entier peut être faite. Dans cet exemple, la définition des variables et constantes a été omise, ainsi que la pré-lecture des données en mémoire.

---

```

/* Additionne les entiers du vecteur x et place le résultat dans la

* variable y.

*

* Étapes :

* 1) assignation globales

* 2) On additionne, un à la fois, les entiers de 4 octets jusqu'à ce

*    que le vecteur soit aligné à un 16 octets en mémoire.

* 3) On additionne en block de 4 entiers de 4 octets à la fois.

* 4) On additionne les sommes partielles.

* 5) On additionne les entiers restant.

* 6) On place le résultat dans la variable y en mémoire.

*/

/** 1) assignation globales **/

/* pointe sur la donnée de x ou l'on est rendu */

lea esi, x

/* pointe sur où il faut sauvegarder le résultat */

lea edi, y

/* calcul la fin du tableau */

mov edx, esi

add edx, x_size

/* y = 0; */

xor ebx, ebx

/* 2) On additionne, un à la fois, les entiers de 4 octets jusqu'à ce

*    que le vecteur soit aligné à un 16 octets en mémoire

*/

/* calcul si on est aligné au 16 bit */

mov ecx, esi

and ecx, 0x0000000f

cmp ecx, 0

jz forlb

sub ecx, 16

/* tant qu'on n'est pas aligné */

forlb :

/* effectue une addition */

add ebx, [esi]

/* change à l'entier suivant */

add esi, 4

/* valide si on est aligné maintenant */

add ecx, 4

cmp ecx, 0

jnz forlb

```

---

---

```

/* fin de la boucle */

for1e:

/* *** 3) On additionne en block de 4 entiers de 4 octets à la fois ***/

/* initialise l'endroit des résultats partiels */

pxor xmm0, xmm0

/* calcul le dernier endroit aligné du tableau */

mov eax, edx

and eax, 0xffffffff0

/* valide qu'il y a de quoi à calculer */

cmp esi, eax

jge for2e

/* déroulement de boucle pour le premier seulement */

/* y += x[i-3] + x[i-2] + x[i-1] + x[i] */

paddd xmm0, [esi]

/* début de la boucle */

for2b:

/* place pour le prochain calcul */

add esi, 16

cmp esi, eax

jge for2e

/* y += x[i-3] + x[i-2] + x[i-1] + x[i] */

paddd xmm0, [esi]

/* débute une autre boucle */

jmp for2b

/* fin de la boucle */

for2e :

/* *** 4) On additionne les sommes partielles ***/

push esp

movd [esp], xmm0

psrlq xmm0, 4

push esp

movd [esp], xmm0

psrlq xmm0, 4

push esp

movd [esp], xmm0

psrlq xmm0, 4

push esp

movd [esp], xmm0

add ebx, [esp]

add esp, 4

add ebx, [esp]

add esp, 4

```

---

---

```

add    ebx,    [esp]

add    esp,    4

add    ebx,    [esp]

add    esp,    4

/* *** 5) On additionne les entiers restant ***/

/* calcul les entiers restant */

for3b :

/* est-ce que c'est terminé ? */

cmp esi, edx

jge for3e

/* effectue une addition */

add ebx, [esi]

/* change à l'entier suivant */

add esi, 4

jmp for3b

/* fin de la boucle */

for3e:

/* *** 6) On place le résultat dans la variable y en mémoire ***/

mov [edi], ebx

```

---

*Code 1-1 : Addition d'un vecteur d'entier en assembleur.*

Voyant tout ce qu'implique la programmation des instructions data-parallèles en langage assembleur, il est aisément de comprendre pourquoi peu de gens l'apprécient et encore moins l'utilise. Elle reste néanmoins utilisée lorsqu'un gain de performance est obligatoire, et que les autres moyens plus simples ont échoués à l'atteinte des objectifs.

### 1.5.2 Les fonctions intrinsèques

Une autre avenue pour utiliser les instructions data-parallèles est l'utilisation d'un compilateur qui inclut des fonctions intrinsèques pour travailler avec les instructions data-parallèles. Une fonction intrinsèque est une fonction dans le langage C, dont l'implémentation est assurée par le compilateur, qui ne provient pas d'une librairie de code externe. Le compilateur en possède une connaissance approfondie et est en mesure de

l'optimiser. Ces fonctions sont pour l'essentiel un remplacement direct des instructions assembleurs. Par exemple, la fonction intrinsèque `_mm_add_pi32` en C est l'équivalent de l'instruction `PADDD` en assembleur. Il faut utiliser un type de donnée spécifique pour ces opérations. Ceci implique qu'il faut transférer les données de travail du type choisis (entier trente-deux bits par exemple) vers ce type. Cette opération correspond au transfert de données de la mémoire à un registre du processeur. Ensuite, l'appel de la fonction peut avoir lieu. Finalement, il faut transférer le résultat vers l'endroit désiré, représentant le déplacement des données du registre vers la mémoire.

Donc, ces fonctions aident à écrire le code, mais tout comme le langage assembleur, elles ont plusieurs défauts. Nous nommerons seulement l'utilisation d'un type de donné particulier et l'alignement de données en mémoire. Le Code 1-2 est le même que le Code 1-1, mais en langage C avec l'utilisation des fonctions intrinsèques.

---

```

/* Additionne les entiers du vecteur x et place le résultat dans la

* variable y.

*/

/* 1) Assignment globales */

/* pointe sur la donnée de x où l'on est rendu */

const unsigned int * px = x;

/* calcul la fin du tableau */

const unsigned int *const pxend = *(x + 1);

/* y = 0; */

y = 0;

/* 2) On additionne, un à la fois, les entiers de 4 octets jusqu'à ce que

* le vecteur soit aligné à un 16 octets en mémoire

*/

/* tant qu'on n'est pas aligné */

while (reinterpret_cast<unsigned int>(px) & 0x0000000f)

{

y += *px++;

}

/* 3) On additionne en block de 4 entiers à la fois */

/* initialise l'endroit des résultats partiels */

__m128i tmp1 = {0};

/* calcul le dernier endroit aligné du tableau */

const unsigned int *const pxenda =

reinterpret_cast<unsigned int *>(

reinterpret_cast<unsigned int>(pxend) & 0xfffffff0

);

/* Tant qu'il y a de quoi à calculer en block */

while (px < pxenda)

{

/* y += x[i-3] + x[i-2] + x[i-1] + x[i] */

__m128i tmp2;

tmp2 = _mm_setr_epi32(*px++, *px++, *px++, *px++);

tmp1 = _mm_add_epi32(tmp1, tmp2);

}

/* 4) On additionne les sommes partielles */

for (size_t i = 0; i < 4; ++i)

{

y += tmp1.m128i_u32[i];

}

/* 5) On additionne les entiers restant */

```

---

---

```

while (px < pxend)

{

y += *px++;

}

```

---

*Code 1-2 : Addition d'un vecteur d'entier en langage C en utilisant les fonctions intrinsèques.*

### 1.5.3 Optimisation par le compilateur

La troisième option est d'opter pour un compilateur optimisant qui sait comment utiliser les instructions data-parallèles. Présentement il est aisément de trouver un compilateur qui est capable d'utiliser une partie des instructions data-parallèles. Le Code 1-3 montre la même opération qu'au Code 1-1 et au Code 1-2 qui serait optimisé par un compilateur optimisant.

---

```

/* Additionne les entiers du vecteur x et place le résultat dans la

* variable y.

*/

y = 0;

for (int i = 0; i < X_SIZE; ++i)

{

y += x[i];

}

```

---

*Code 1-3 : Addition d'un vecteur d'entier en langage C.*

| Compilateur | Jeux d'instructions IUDM supportés                |

|-------------|---------------------------------------------------|

| Microsoft   | MMX, SSE, SSE2                                    |

| Intel       | MMX, SSE, SSE2, SSE3, SSSE3, SSE4, SSE4.1, SSE4.2 |

| gcc         | MMX, SSE, SSE2, SSE3, SSSE3, SSE4, SSE4.1, SSE4.2 |

*Tableau 1-2 : Jeux d'instructions IUDM supportés par les compilateurs.*

En plus de ne pas toujours supporter tous les jeux d'instructions IUDM disponibles comme le montre le Tableau 1-2, ils ne sont pas capables d'optimiser le code dans toutes les circonstances. Le document (Levicki, 2012) montre que le compilateur d'Intel est capable

d'optimiser le Code 1-4 mais pas le Code 1-5, deux codes qui sont presque identiques. La différence est en caractères gras dans le code.

---

```

for (short i = 0; i < SIZE; ++i)

{

// corps de la boucle

}

```

---

*Code 1-4 : Boucle optimisée par le compilateur d'Intel.*

---

```

for (unsigned short i = 0; i < SIZE; ++i)

{

// corps de la boucle

}

```

---

*Code 1-5 : Boucle non optimisée par le compilateur d'Intel.*

L'utilisation d'un compilateur optimisant qui inclus l'utilisation d'une partie des instructions data-parallèles est mieux que celle d'un compilateur qui ne les utilise pas, mais ceci n'est pas l'idéal et n'est parfois pas suffisant.

#### 1.5.4 Besoin

Il est maintenant clair qu'un outil permettant au programmeur d'utiliser la puissance offerte par les instructions data-parallèles de manières simple et efficace est pertinent et nécessaire. Cet outil devrait utiliser les instructions data-parallèles partout où c'est pertinent. Le programmeur ne devrait pas avoir à fournir d'effort supplémentaire.

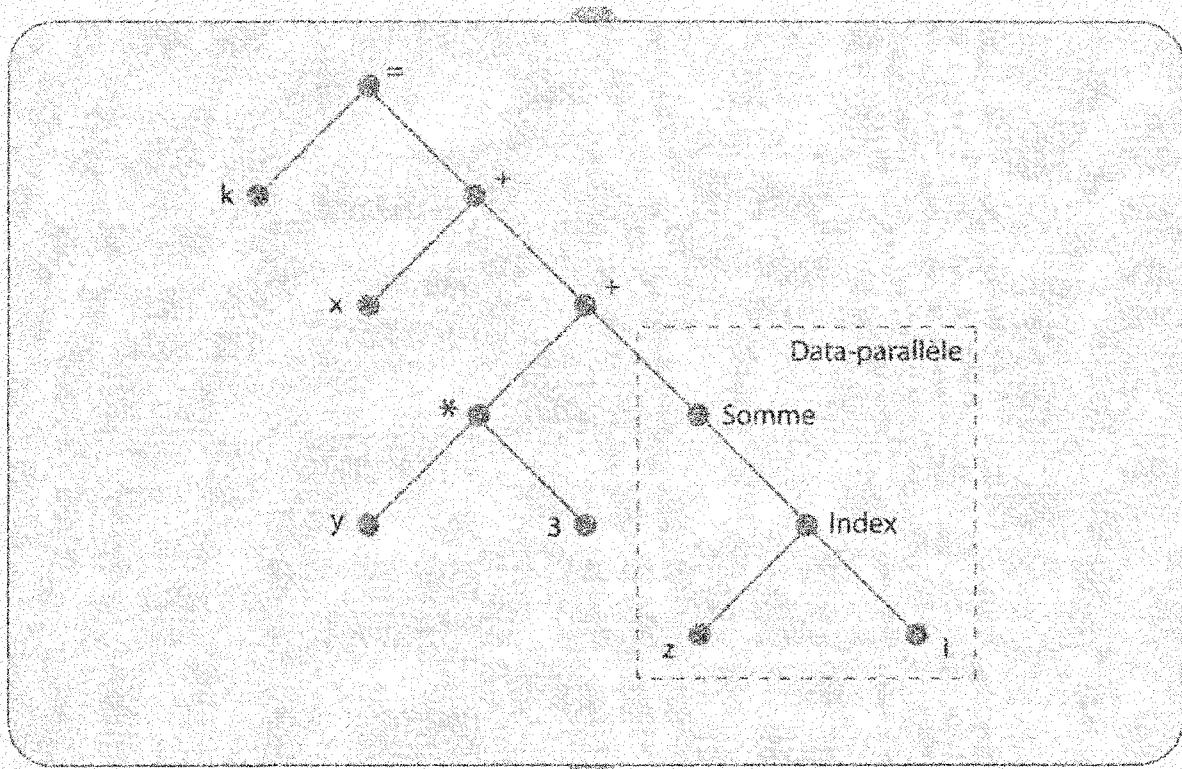

Afin de résoudre cette problématique, nous proposons un ensemble d'instructions data-parallèles qui seront intégrées au langage psC. Le paradigme supporté par le langage psC étant parallèle, en non séquentiel, fait de ce langage de programmation de FPGA le candidat idéal pour y intégrer des instructions data-parallèles.

Intel offre une implémentation de valarray qui utilise les instructions SSE. L'objectif étant d'évaluer la faisabilité d'utiliser un langage pour programmation matérielle pour générer le code pour FPGA, cette approche n'a pas été investiguée.

## 2

## ALGORITHMES

Les logiciels, ou applications, sont des ensembles d'algorithmes ordonnés de manière à effectuer une ou plusieurs tâches précises. Pour être en mesure d'améliorer la performance, il est nécessaire de comprendre et classifier ces algorithmes. Ceci, afin de mieux définir les instructions data-parallèles pertinentes et utiles.

### 2.1 Classification des algorithmes

Comme vu en 1.2, il existe plusieurs architectures matérielles. L'existence de ces architectures matérielles provient du fait que les algorithmes sont différents, et que certains sont plus simple à implémenté sur certaines architectures.

On présente ici une classification des algorithmes qui se base sur la dépendance entre les données. Ceci nous permet de déterminé ceux qu'il est possible paralléliser sur l'architecture PC et de mieux les connaître. Pour définir le comportement des algorithmes, on utilise les termes bloc d'instructions et bloc de données. Un bloc d'instructions est un ensemble d'instructions ordonnées d'une manière précise pour effectuer une tâche. Un bloc d'instructions ne peut pas être divisé. Il doit être vu comme monolithique. Un bloc de

données est constitué de plusieurs données, toutes traitées simultanément par un bloc d'instructions.

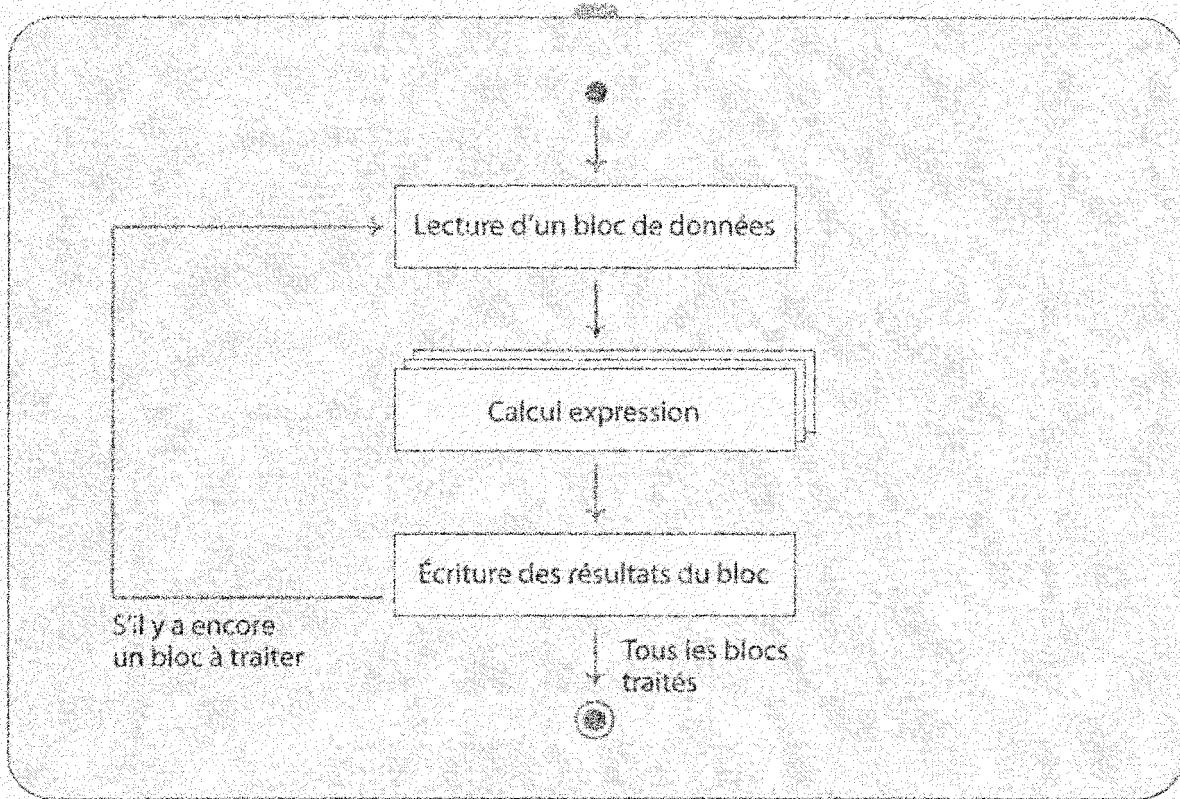

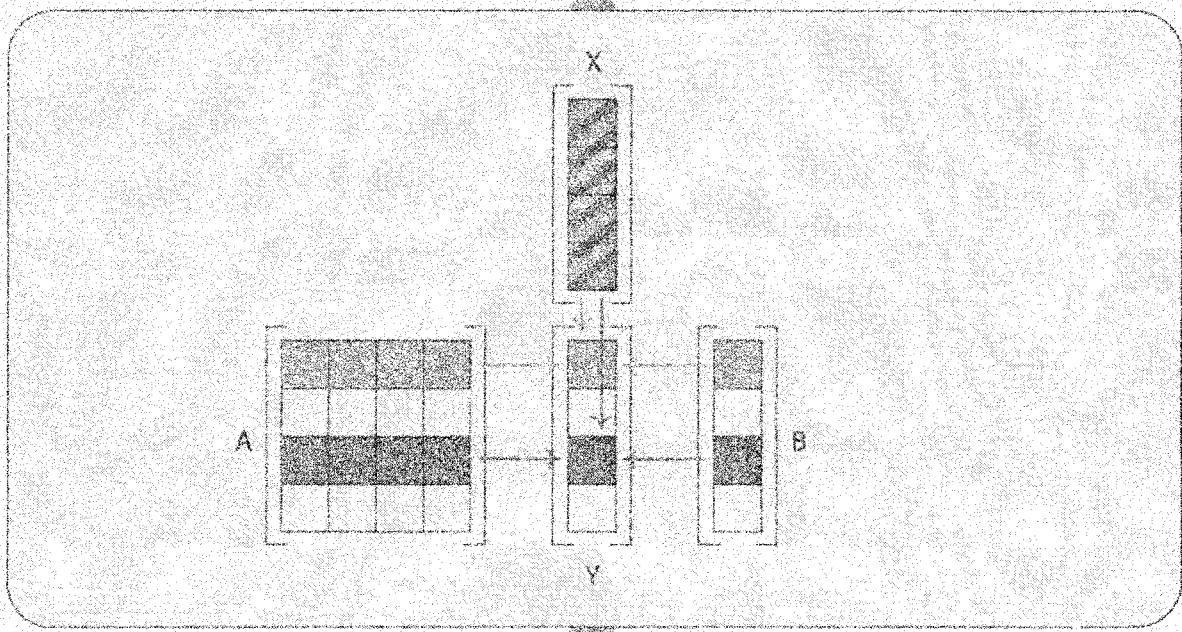

### 2.1.1 Algorithmes synchrones

Les algorithmes synchrones peuvent se composer d'un ou plusieurs blocs d'instructions. Cependant, il n'y a qu'un seul chemin d'exécution possible. De plus, il ne doit pas y avoir de corrélation entre les données pour que chacun des blocs de données puissent être traités indépendamment des autres. Lorsque l'architecture matérielle le permet, les blocs de données peuvent être traités de manière parallèle. Ces algorithmes sont des candidats parfaits pour un traitement via une architecture IUDM car ils peuvent être traités avec une séquence de blocs d'instructions.

Voici un exemple algorithme synchrone : considérant  $A$ ,  $B$  et  $C$  comme des vecteurs, il est possible d'exécuter l'algorithme montré au Code 2-1 en utilisant  $i$  comme index de bloc de données. La Figure 2-1 l'illustre.

---

```

C[i] = A[i] + B[i];

```

---

*Code 2-1 : Algorithme synchrone*

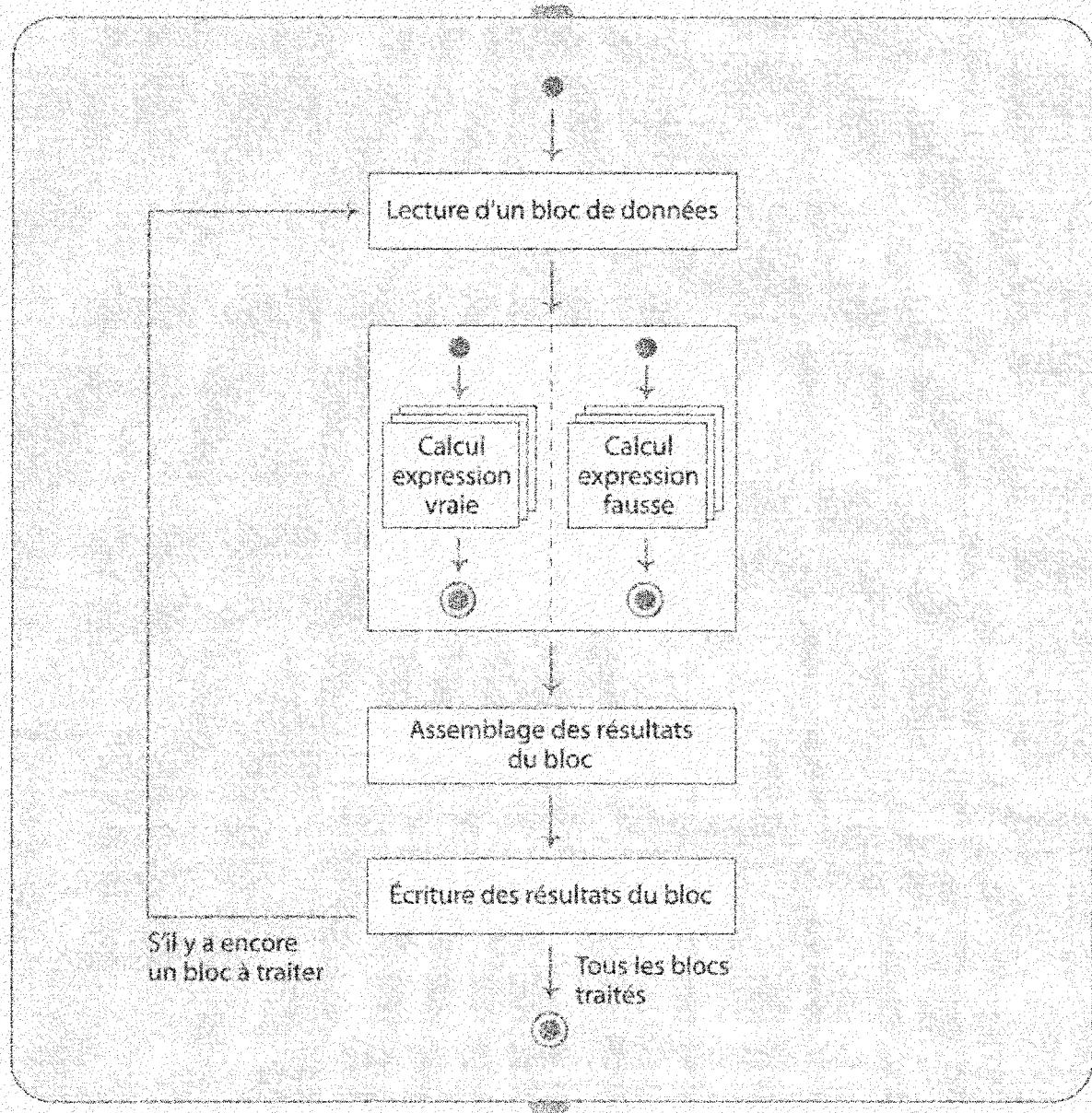

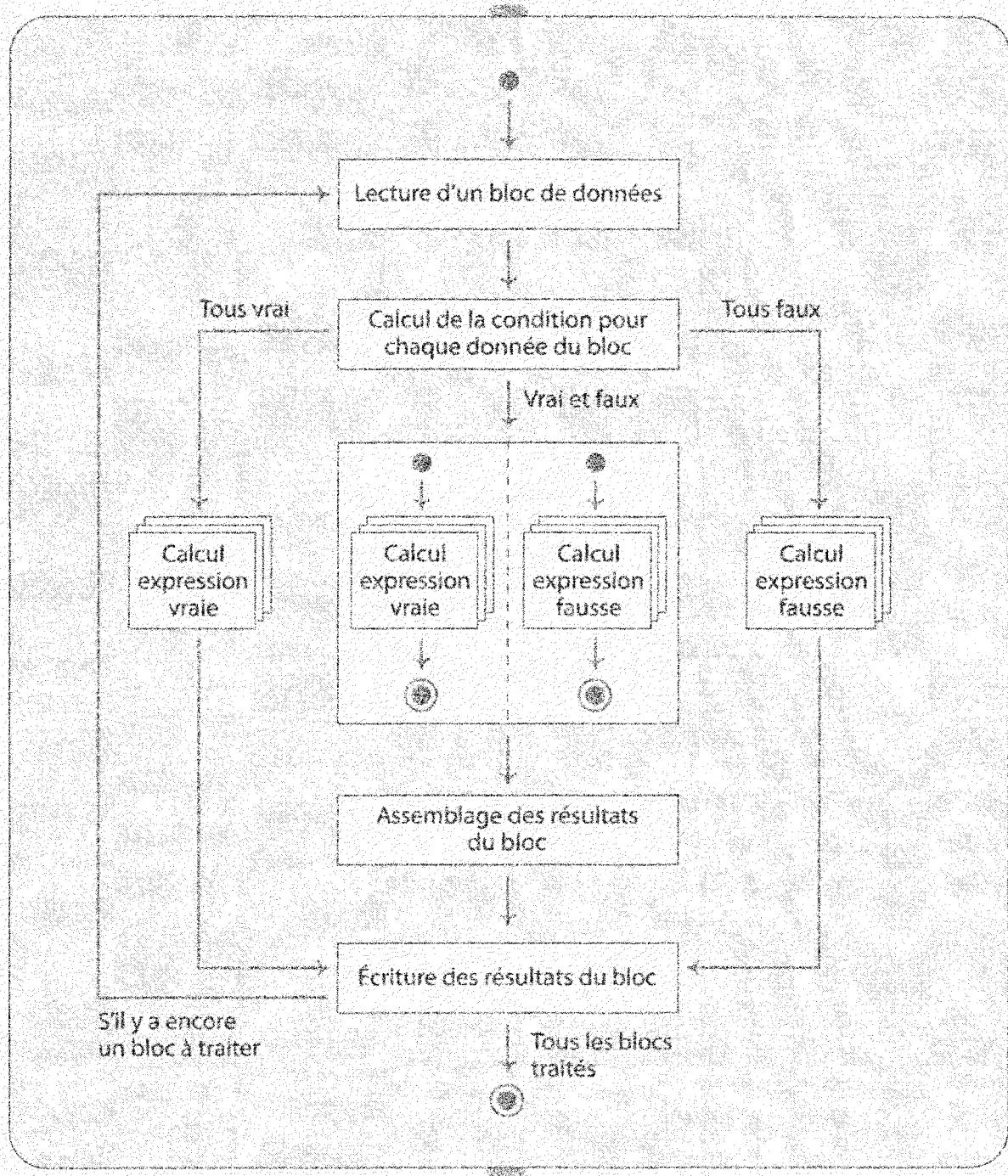

Figure 2-1: Algorithme synchrone.

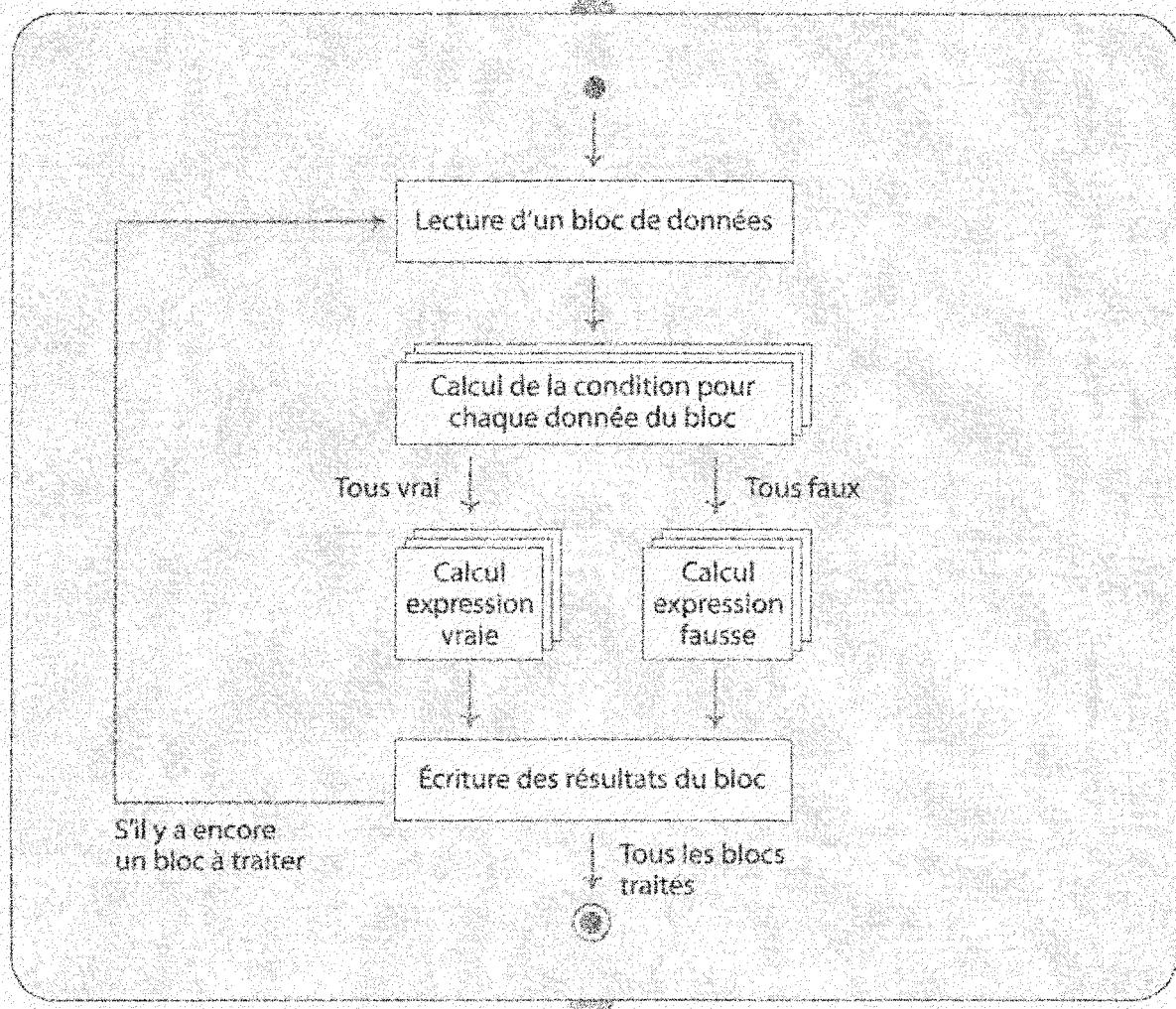

### 2.1.2 Algorithmes légèrement synchrones

Les algorithmes légèrement synchrones sont similaires aux algorithmes synchrones à l'exception d'un seul point. Le chemin d'exécution entre les blocs d'instructions varie en fonction du bloc de données traité. Le meilleur moyen pour expliquer est via un exemple. En reprenant l'exemple précédent et en changeant le calcul, nous obtenons un algorithme légèrement synchrone (voir le Code 2-2). Il y a plusieurs chemins différents entre les blocs d'instructions en fonction de la comparaison  $A[i] < 0$ .

---

```

C[i] = (A[i] < 0) ? (A[i] | B[i]) : (A[i] & B[i]);

```

---

Code 2-2 : Algorithme légèrement synchrone.

Contrairement aux les algorithmes synchrones, il est impossible de les traiter en une seule séquence de blocs d'instructions sous une architecture IUDM. Il est nécessaire d'effectuer des opérations à priori ou à postériori supplémentaires. Les opérations à priori servent à détecter lequel des chemins d'exécutions doit être emprunté, pour ensuite effectuer les blocs d'instructions s'y trouvant (voir la Figure 2-2). Cette approche exige que le chemin d'exécution convienne à toutes les données d'un bloc de données. Pour le cas à postériori, tous les chemins d'exécutions sont fait et on choisit le bon résultat pour chaque donné du bloc de données par la suite (voir la Figure 2-3). Ceci implique d'effectuer toujours tous les blocs d'instructions, qu'il soit nécessaire ou pas au résultat final. Enfin, il est possible d'effectuer les deux techniques en simultané (voir la Figure 2-4). Aucune de ces solutions n'est optimale car il y a du travail supplémentaire qui est requis dans tous les cas.

Figure 2-2: Algorithme légèrement synchrone - opération à priori.

Figure 2-3: Algorithme légèrement synchrone - opération à postériori.

Figure 2-4: Algorithme légèrement synchrone - opérations à priori et à postériori.

Ces algorithmes sont de bons candidats pour les architectures IMDM. Sur ces architectures, chaque bloc peut être effectué sur une unité de traitement différente.

### 2.1.3 Algorithmes asynchrones

Les algorithmes asynchrones ont comme caractéristique que leurs données ne sont pas indépendantes. Il faut donc avoir une connaissance particulière de l'algorithme pour synchroniser l'accès aux données et paralléliser les parties qui peuvent l'être.

Historiquement, tous les programmes sont traités comme des algorithmes asynchrones car les architectures matérielles n'avaient pas la possibilité d'améliorer les performances de manière automatique. Généralement, il n'y a pas de parallélisme mis de l'avant et un seul chemin d'exécution est actif à un temps précis. Ce sont les algorithmes que les programmeurs trouvent les plus simples à comprendre, concevoir, implanter et maintenir (voir la Figure 2-5).

Figure 2-5: Algorithme asynchrone.

Ils sont de bons candidats pour les architectures IUDU.

## 2.2 Instructions souhaitables

Pour être viables, les langages inclus dans le paradigme de programmation data-parallèles doivent supporter les instructions traditionnelles disponibles dans le paradigme de programmation impératif, mais ils doivent en plus offrir plusieurs instructions qui ne sont pas disponibles dans les autres paradigmes de programmations. Ces instructions sont des instructions qui traitent des données en parallèles. Ces instructions sont décrites dans les sections suivantes.

Pour simplifier l'écriture, nous utiliserons la notion de groupe de données. Un groupe de données est soit un vecteur ou une matrice contenant les données. Toutes les données d'un groupe de donnée sont du même type.

### 2.2.1 Le type « index »

Un nouveau type `index` est utilisé pour les instructions data parallèles proposées. Les variables de type `index` permettent d'identifier des plages de valeurs. Par exemple, pour indiquer d'effectuer une opération sur tous les éléments de la première dimension de tableaux, un `index` est utilisé, comme le montre le Code 2-3.

---

```

/* Exemple d'utilisation du type index.

*/

/* déclaration */

int32 M[10];

int32 N[10];

int32 V[10];

index i;

/* Effectuer ici du travail pour assigner des valeurs. */

/* calcul qui utilise l'index */

V[i] = M[i] + N[i];

```

---

*Code 2-3 : Utilisation du type index.*

### 2.2.2 Instructions d'affectations

Une instruction d'affectation permet d'assigner un groupe de données à un endroit précis d'un autre groupe de données. Par exemple, envoyer les données d'un vecteur dans une rangée d'une matrice. Le Code 2-4 montre comment cette instruction pourrait être effectuée dans un langage hypothétique. De plus, la combinaison avec les instructions de sectionnement permet d'extraire un sous-groupe de données à partir d'un groupe de données et de les insérer dans un autre groupe de données.

---

```

/* Déclaration du vecteur de taille T et de la matrice de taille T x T,

* tous deux de type entier à 32 bit.

*/

int32 V[T];

int32 M[T][T];

/* Effectuer ici du travail pour assigner des valeurs. */

/* Effectue des communications. */

index i;

M[2][i] = V[i]; // rangée

M[i][2] = V[i]; // colonne

M[i][i] = V[i]; // diagonale

```

---

*Code 2-4 : Instruction de communication.*

### 2.2.3 Instructions de sectionnement

Du moment que l'on parle d'un groupe de donnée, il devient nécessaire de pouvoir référencer à un sous-ensemble du groupe de données comme s'il était lui-même un groupe de données. Cette capacité d'extraire une partie du groupe de donnée se nomme sectionnement. Par exemple, si une fonction qui effectue un travail avec un vecteur et que nous avons une matrice de deux dimensions, il faut être en mesure d'exécuter la fonction sur une colonne de la matrice. Le Code 2-5 montre comment ceci pourrait être fait dans un langage hypothétique.

---

```

/* déclaration d'une matrice A de taille 4x8 et de type entier à 32 bit.

*/

int32 A[4][8];

/* Effectuer ici du travail avec A pour lui assigner des valeurs. */

/* Indique quel est le sectionnement et récupère l'élément (Colonne 2),

* via un tableau de référence pour ne pas avoir de copie.

*/

index i;

int32 & SGA[8] = A[2][i];

/* Utiliser le sous-groupe comme étant un vecteur de taille 8 */

```

---

*Code 2-5 : Instruction de sectionnement.*

### 2.2.4 Instructions conditionnelles

Certains algorithmes nécessitent qu'un calcul soit appliqué à seulement une partie des éléments d'un groupe de données. Lorsque ceci se produit, il est nécessaire d'effectuer un test sur les données elles-mêmes pour décider si l'opération les affecte. Cette capacité se nomme instruction conditionnelle. Par exemple, des instructions permettant d'effectuer l'inverse des éléments différents de zéro. Le Code 2-6 montre comment ceci pourrait être fait dans un langage hypothétique.

---

```

/* déclaration d'un vecteur V de taille T et de type entier à 32 bit. */

int32 V[T];

/* Effectuer ici du travail avec V pour lui assigner des valeurs. */

/* Effectue l'inverse de tous les éléments non nul. */

index i;

V[i] = (V[i] == 0) ? V[i] : (1 / V[i]);

```

---

*Code 2-6 : Instruction conditionnelle.*

#### 2.2.5 Instructions de réductions

Les instructions de réduction consistent à diminuer le nombre de dimensions d'un groupe de données. Par exemple, passer d'une matrice à cinq dimensions à une matrice à quatre dimensions. La réduction est dite complète lorsque le groupe devient un scalaire. Sinon elle est qualifiée de partielle. Il existe plusieurs techniques qui peuvent être utilisés pour effectuer cette réduction. Par exemple, l'élément du groupe de dimension moindre pourrait correspondre à la somme de tous les éléments correspondant dans le groupe de dimensions plus importante. Ce pourrait également être le plus petit élément, le plus grand, la variance, la covariance, l'écart type, etc. Le Code 2-7 montre comment une réduction partielle utilisant la valeur minimale pourrait être effectuée dans un langage hypothétique.

---

```

/* déclaration d'une matrice M de taille 4x8 et de type entier à 32 bit.

*/

int32 M[4][8];

/* Effectuer ici du travail avec M pour lui assigner des valeurs. */

/* Effectue la réduction vers un vecteur de taille 4. */

int32 V[4];

index i;

V = min(M[i]);

```

---

*Code 2-7 : Instruction de réduction.*

### 2.2.6 Instructions vectorielles

Une instruction vectorielle est une instruction qui s'exécute sur chacune des données d'un groupe de données. Il doit être transparent pour l'usager qu'il utilise une instruction scalaire ou vectorielle. L'instruction scalaire traitera une donnée, l'instruction vectorielle traitera un groupe de données. Par exemple, si un langage offre la possibilité d'écrire le Code 2-8 où  $A$ ,  $B$  et  $C$  sont des scalaires, le même code devrait pouvoir être utilisé lorsque  $A$ ,  $B$  et  $C$  sont des groupes de données de même taille.

---

$A = B + C$

---

*Code 2-8 : Instruction vectorielle.*

L'utilisation d'un langage impératif, contraint à l'utilisation d'une boucle (voir le Code 2-8). Il va sans dire que l'optimisation du code machine généré, qu'il soit axé sur le temps d'exécution ou la taille du code, n'est pas garantie.

---

```

for (int i = 0; i < DATA_SIZE; ++i)

{

A[i] = B[i] + C[i];

}

```

---

*Code 2-9 : Instruction vectorielle en langage C.*

### 2.3 Solution selon valarray

Valarray est le nom donné à un ensemble d'objets et fonctions faisant partie du standard C++. Il offre la possibilité d'effectuer plusieurs des opérations souhaitables directement en langage C++. Cependant, comme le montre le document (AFNOR, 2000), valarray n'est pas parfait du point de vue de la syntaxe. De plus il ne supporte pas les tableaux à plusieurs dimensions naturellement. Il est néanmoins utile de regarder comment

il adresse chacune des instructions souhaitées pour la création, l'affectation et l'accès aux données, afin de s'en inspirer dans le cadre du travail.

### 2.3.1 Construction

Il est possible de créer un objet valarray de plusieurs manières, comme le démontre le Code 2-10. Il est intéressant de noter la création par copie (en gras) qui utilise une syntaxe vectorielle simple.

---

```

/* Création d'un vecteur de int. */

valarray<int> v1;

/* Création d'un vecteur de taille précise (8). */

valarray<int> v2(8);

/* Création d'un vecteur de taille précise (8), dont les éléments sont

* tous initialisés à une même valeur (3).

*/

valarray<int> v3(3, 8);

/* Création d'un vecteur de taille précise (8), dont les éléments sont

* initialisés à des valeurs données.

*/

static const int initval[] = {0, 1, 2, 3, 4, 5, 6, 7};

valarray<int> v4(initval, 8);

/* Création d'une copie d'un vecteur */

valarray<int> v5(v4);

valarray<int> v6 = v4;

```

---

*Code 2-10 : Valarray – construction.*

### 2.3.2 Instructions d'affectation

La première manière d'affecter des valeurs à un valarray est lors de sa création. Le Code 2-10 montre comment affecter tous les indices à la même valeur et à des valeurs différentes dans cette situation.

En dehors de la création, il est possible d'affecter un scalaire à chacun des éléments via l'opérateur égal. Pour l'accès à un seul élément (un scalaire) en dehors de la création, l'opérateur crochet est utilisé. Le Code 2-11 montre comment les accès en lecture et en écriture fonctionnent.

---

```

/* Affectation de la valeur 'a' à tous les éléments d'un valarray 'v' */

v = a

/* Affectation de la valeur 'a' à un élément 'i' d'un valarray 'v' */

v[i] = a

/* Extraction d'une valeur 'a' d'un élément 'i' d'un valarray 'v' */

a = v[i];

```

---

*Code 2-11 : Valarray – affectation et extraction d'un scalaire.*

Enfin, il est possible d'affecter des groupes de données à des endroits précis en utilisant l'opérateur crochet et des objets explicitement fabriqués pour ce faire. Ces cas seront couverts dans la section 2.3.3.

### 2.3.3 Instructions de sectionnement

Valarray offre deux objets pour effectuer le sectionnement; *splice* et *gsplice*. Le premier est utilisé pour transformer un index à deux dimensions vers l'index unique du valarray. Le second, plus complexe, est utilisé pour transformer un index à dimensions plus élevé vers l'index unique de valarray. L'application de ces objets à un valarray donne un objet intermédiaire qui peut être utilisé pour créer un nouvel objet valarray ou utilisé à la place d'un valarray dans certaines instructions. Le Code 2-12 montre des exemples.

---

```

/* Multiplie les éléments 1, 3 et 5 du valarray 'v' par 10 */

v[std::slice(1,3,2)] *= std::valarray<int>(10, 3);

/* Affecte 99 aux éléments 0, 3, 6 du valarray 'v' */

v[std::slice(0,3,3)] = 99;

/* Affecte les éléments 0, 3 et 6 du valarray 'v2' et les affectent aux

* éléments 0, 4, 8 du valarray 'v2'

*/

v1[std::slice(0,3,3)] = v2[std::slice(0,3,4)] = 99;

```

---

*Code 2-12 : Valarray – Instructions de sectionnement.*

#### 2.3.4 Instructions conditionnelles

L'instruction conditionnelle n'existe pas avec valarray. Cependant, il est possible d'obtenir un résultat similaire en utilisant un opérateur de comparaison avec un valarray.

L'objet fabriqué par cette opération est un `valarray<bool>` qui contient `true` pour chaque élément pour lequel la condition est vraie. Appliquée au valarray via l'opérateur crochet, il sélectionne les éléments pour lesquels il est à `true`. Il est possible d'inverser un `valarray<bool>` avec l'opérateur de négation logique. Enfin, une opération peut être effectuée à un sous-groupe et affecter à un endroit précis. Le Code 2-13 en montre l'utilisation.

---

```

/* Effectue l'opération v = v > 25 ? 25 : -v; avec valarray */

valarray<int> v(50);

for (int i = 0; i < v.size(); ++i)

v[i] = i;

/* Sélectionne les éléments plus grand que 25 du valarray 'v' */

valarray<bool> greater25 = v > 25;

/* Affecte 25 à tous les éléments de 'v' qui sont plus grand que 25 */

v[greater25] = 25;

/* Affecte '-v' aux autres éléments de 'v' */

v[!greater25] = -std::valarray<int>(v[!greater25]);

```

---

*Code 2-13 : Valarray – Instructions conditionnelles.*

### 2.3.5 Instructions de réductions

Valarray n'offre qu'une sélection limitée de réductions listé au Tableau 2-1. Pour toute autre instruction de réduction, il est nécessaire que le programmeur fasse preuve d'originalité dans l'utilisation des `slice` et de la fonction `apply`. La somme de travail pour le programmeur serait moindre si plus d'opérations de réductions seraient offertes.

| Opération         | Description                                       |

|-------------------|---------------------------------------------------|

| <code>size</code> | La taille du valarray.                            |

| <code>sum</code>  | La somme des éléments du valarray.                |

| <code>min</code>  | L'élément le plus petit contenu dans le valarray. |

| <code>max</code>  | L'élément le plus grand contenu dans le valarray. |

Tableau 2-1 : Valarray - instructions de réduction.

### 2.3.6 Instructions vectorielle

Valarray supporte certaines instructions vectorielles via des fonctions spécialisées prenant un valarray en paramètre. Le Tableau 2-2 indique toutes les opérations vectorielles supportées. Chacune de ces opérations a comme paramètre un valarray. Lorsqu'elle nécessite plus d'un paramètre, il peut être soit un scalaire qui est réutilisé pour chaque élément, soit un valarray de taille identique dont chaque élément est utilisé avec l'élément réciproque de l'autre valarray. De plus, la fonction membre `apply` permet d'appliquer une fonction fournie par l'usager à chaque élément du valarray.

```

/* Additionne 3 à tous les éléments d'un valarray 'v' */

v += 3;

/* Divise par 5 tous les éléments d'un valarray 'v' */

v /= 5;

/* Effectue la puissance d'un valarray 'v' par 2 */

v = pow(v, 2);

/* Effectue la puissance d'un valarray 'v' par un autre valarray 'p' */

v = pow(v, p);

/* Applique la fonction fn à chaque éléments du valarray 'v' */

v = v.apply(fn);

```

*Code 2-14 : instructions vectorielles de valarray.*

| Fonction    | Description                                  |

|-------------|----------------------------------------------|

| abs         | Valeur absolue                               |

| asin        | Arc sinus                                    |

| acos        | Arc cosinus                                  |

| atan        | Arc tangente                                 |

| atan2       | Arc tangente à deux arguments                |

| cos         | Cosinus                                      |

| cosh        | Cosinus hyperbolique                         |

| exp         | Exponentiel naturel                          |

| log         | Logarithme naturel                           |

| log10       | Logarithme à base 10                         |

| pow         | Puissance                                    |

| sin         | Sinus                                        |

| sinh        | Sinus hyperbolique                           |

| sqrt        | Racine carrée                                |

| tan         | Tangente                                     |

| tanh        | Tangente hyperbolique                        |

| + (unaire)  | Ne change pas la valeur                      |

| - (unaire)  | Inverse le signe                             |

| + (binaire) | Addition                                     |

| - (binaire) | Soustraction                                 |

| ~           | Inverse les bits qui composent le nombre     |

| *           | Multiplication                               |

| /           | Division                                     |

| %           | Reste de la division (modulo)                |

| ^           | Ou exclusif binaire                          |

| &           | Et binaire                                   |

|             | Ou inclusif binaire                          |

| <<          | Décalage à gauche des bits de chaque élément |

| >>          | Décalage à droite des bits de chaque élément |

| ==          | Égalité                                      |

| !=          | Non égalité, différent                       |

| <           | Plus petit                                   |

| >           | Plus grand                                   |

| <=          | Plus petit ou égal                           |

| >=          | Plus grand ou égal                           |

|             | Ou logique                                   |

| &&          | Et logique                                   |

Tableau 2-2 : Valarray – instructions vectorielles.

## 2.4 Solution selon Blitz++

Blitz++ est également une librairie conçue pour le langage C++. Comme valarray, elle ajoute la possibilité d'effectuer les opérations souhaitables. Les opérations sont seulement au niveau de la syntaxe, et aucune optimisation n'est effectuée pour prendre en charge les possibilités offertes par le matériel, sauf ce que le compilateur réussira à optimiser. À l'instar de valarray, son étude est une bonne source d'inspiration pour la solution proposée. La classe sur laquelle est basée la librairie se nomme *Array*.

### 2.4.1 Construction

La création d'un objet *Array* s'effectue principalement via l'une des deux formes démontrées au Code 2-15. Via la seconde manière, celle utilisant l'objet *Range*, il est possible de créer des objets dont les index ne débutent pas à zéro. Il est également possible de créer des objets dont la structure mémoire est ordonnée comme en Fortran, où la colonne est majeure, au lieu de la manière C, où rangée est majeur. Un *Array* ne peut pas recevoir de valeur initialement, sauf si c'est le résultat d'une opération qui produit un *Array*.

---

```

/* Création d'une matrice tridimensionnelle de taille NxNxN de float */

blitz::Array<float,3> A(N,N,N);

/* Création d'une matrice 5x5 dont les indices sont -2 à 2 et 1 à 5. */

blitz::Array<float,2> A(blitz::Range(-2,2), blitz::Range(1, 5));

```

---

*Code 2-15 : Blitz++ – construction.*

### 2.4.2 Affectation et extraction de valeurs

La première manière d'affecter des valeurs à un *Array* de Blitz++ est d'utiliser l'opérateur « virgule » pour assigner directement une matrice. Le Code 2-16 montre l'utilisation de cette technique. Il est possible d'affecter la valeur d'un scalaire à tous les

éléments via l'opérateur égal. Pour l'accès à un seul élément (un scalaire), l'opérateur parenthèse (et non l'opérateur crochet comme avec valarray et les tableaux) est utilisé. Le Code 2-16 montre les accès en lecture et en écriture.

---

```

/* Affectation de la valeur 'a' à l'array 'v' */

v = a;

/* Affectation de la matrice identité à 'v' qui est de taille 3x3 */

v = 1, 0, 0,

0, 1, 0,

0, 0, 1;

/* Extraction d'une valeur à la position 'i' 'j' d'un Array 'v' et

* assignation à la position 'k' 'l'

*/

v(k, l) = v(i, j);

```

---