UNIVERSITÉ DU QUÉBEC À CHICOUTIMI

STÉPHANE SIMARD

ÉTUDE DES COMPROMIS ESPACE/TEMPS DANS LES SYSTÈMES

RECONFIGURABLES, POUR LA TECHNOLOGIE PSC

MÉMOIRE PRÉSENTÉ

COMME EXIGEANCE PARTIELLE

DE LA MAÎTRISE EN INGÉNIERIE

MAI 2006

## Mise en garde/Advice

Afin de rendre accessible au plus grand nombre le résultat des travaux de recherche menés par ses étudiants gradués et dans l'esprit des règles qui régissent le dépôt et la diffusion des mémoires et thèses produits dans cette Institution, **l'Université du Québec à Chicoutimi (UQAC)** est fière de rendre accessible une version complète et gratuite de cette œuvre.

Motivated by a desire to make the results of its graduate students' research accessible to all, and in accordance with the rules governing the acceptance and diffusion of dissertations and theses in this Institution, the **Université du Québec à Chicoutimi (UQAC)** is proud to make a complete version of this work available at no cost to the reader.

L'auteur conserve néanmoins la propriété du droit d'auteur qui protège ce mémoire ou cette thèse. Ni le mémoire ou la thèse ni des extraits substantiels de ceux-ci ne peuvent être imprimés ou autrement reproduits sans son autorisation.

The author retains ownership of the copyright of this dissertation or thesis. Neither the dissertation or thesis, nor substantial extracts from it, may be printed or otherwise reproduced without the author's permission.

# Table des matières

|          |                                                                  |           |

|----------|------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                              | <b>1</b>  |

| 1.1      | Le langage psC . . . . .                                         | 2         |

| 1.2      | Historique . . . . .                                             | 3         |

| 1.3      | Les FPGA . . . . .                                               | 4         |

| 1.4      | Problématique . . . . .                                          | 5         |

| 1.5      | Objectifs et méthodologie de recherche . . . . .                 | 10        |

| <b>2</b> | <b>Revue de l'arithmétique des FPGA</b>                          | <b>13</b> |

| 2.1      | Arithmétique parallèle . . . . .                                 | 14        |

| 2.2      | Arithmétique serielle . . . . .                                  | 15        |

| 2.3      | Opérateurs entiers . . . . .                                     | 17        |

| 2.3.1    | Additionneurs et soustracteurs . . . . .                         | 17        |

| 2.3.2    | Multiplieurs . . . . .                                           | 21        |

| 2.3.3    | Multiplieurs bit-séries . . . . .                                | 27        |

| 2.3.4    | Additionneurs et multiplieurs modulaires . . . . .               | 31        |

| 2.3.5    | Opérateurs arithmétiques à base de petits blocs multiplieurs . . | 32        |

| 2.3.6    | Diviseurs et extracteurs de racine carrée . . . . .              | 34        |

| 2.4      | Opérateurs à virgule fixe . . . . .                              | 44        |

| 2.4.1    | Opérateurs à virgule fixe parallèles . . . . .                   | 45        |

| 2.4.2    | Opérateurs en-ligne . . . . .                                    | 46        |

| 2.5      | Opérateurs à virgule flottante . . . . .                         | 54        |

| 2.5.1    | Opérateurs parallèles à virgule flottante . . . . .              | 54        |

| 2.5.2    | Opérateurs sériels à virgule flottante . . . . .                 | 55        |

| 2.6      | Calcul des fonctions élémentaires . . . . .                      | 57        |

| <b>3</b> | <b>Mises en œuvre</b>                                            | <b>59</b> |

| 3.1      | Opérateurs arithmétiques . . . . .                               | 60        |

|          |                                                                                                                                          |           |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 3.1.1    | Additionneurs et soustracteurs . . . . .                                                                                                 | 61        |

| 3.1.2    | Multiplieurs . . . . .                                                                                                                   | 63        |

| 3.1.3    | Diviseurs et opérateur de racine carrée . . . . .                                                                                        | 66        |

| 3.2      | Processeur CORDIC . . . . .                                                                                                              | 68        |

| 3.3      | Étude d'opérateurs arithmétiques sériels MSBF non redondants . . . . .                                                                   | 70        |

| 3.3.1    | Discussion des solutions envisageables . . . . .                                                                                         | 70        |

| 3.3.2    | Mise en œuvre et résultats . . . . .                                                                                                     | 74        |

| <b>4</b> | <b>Analyses de résultats en vue d'estimer la puissance de calcul</b>                                                                     | <b>77</b> |

| 4.1      | Classes de problèmes se limitant aux opérations de la famille de la multiplication et de l'addition entières et à virgule fixe . . . . . | 80        |

| 4.2      | Classes de problèmes comportant des divisions entières et à virgule fixe . . . . .                                                       | 82        |

| 4.3      | Classes de problèmes utilisant des opérations à virgule flottante . . . . .                                                              | 83        |

| <b>5</b> | <b>Conclusion</b>                                                                                                                        | <b>86</b> |

| <b>A</b> | <b>Code psC des principaux composants développés</b>                                                                                     | <b>91</b> |

| A.1      | Description des composants . . . . .                                                                                                     | 92        |

| A.2      | Additionneur-soustracteur bit-sériel . . . . .                                                                                           | 94        |

| A.3      | Multiplieurs . . . . .                                                                                                                   | 94        |

| A.4      | Diviseurs et racine carrée . . . . .                                                                                                     | 102       |

| A.5      | Processeurs CORDIC . . . . .                                                                                                             | 106       |

| A.6      | Opérateurs à virgule flottante sériels . . . . .                                                                                         | 111       |

|          | Bibliographie . . . . .                                                                                                                  | 128       |

# Table des figures

|      |                                                                                                              |    |

|------|--------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Transmission parallèle versus sérieelle . . . . .                                                            | 6  |

| 2.1  | Additionneur à retenue propagée standard . . . . .                                                           | 19 |

| 2.2  | Pipelinage des additionneurs . . . . .                                                                       | 20 |

| 2.3  | Additionneur et soustracteur bit-séries . . . . .                                                            | 21 |

| 2.4  | Multiplieur 8 bits sous forme d'arbre d'additionneurs à propagation de<br>retenues . . . . .                 | 22 |

| 2.5  | Un multiplieur 8 bits par une constante . . . . .                                                            | 24 |

| 2.6  | Multiplieur parallèle-série RCAD conventionnel . . . . .                                                     | 27 |

| 2.7  | Multiplieur parallèle-série RPAD exploitant les lignes de propagation de<br>retenues dédiées . . . . .       | 27 |

| 2.8  | Un multiplieur série-série construit à partir de deux multiplieurs série-<br>parallèle . . . . .             | 29 |

| 2.9  | Un multiplieur série-série utilisant un compteur parallèle . . . . .                                         | 29 |

| 2.10 | Opérateur bit-sériel d'élévation au carré . . . . .                                                          | 30 |

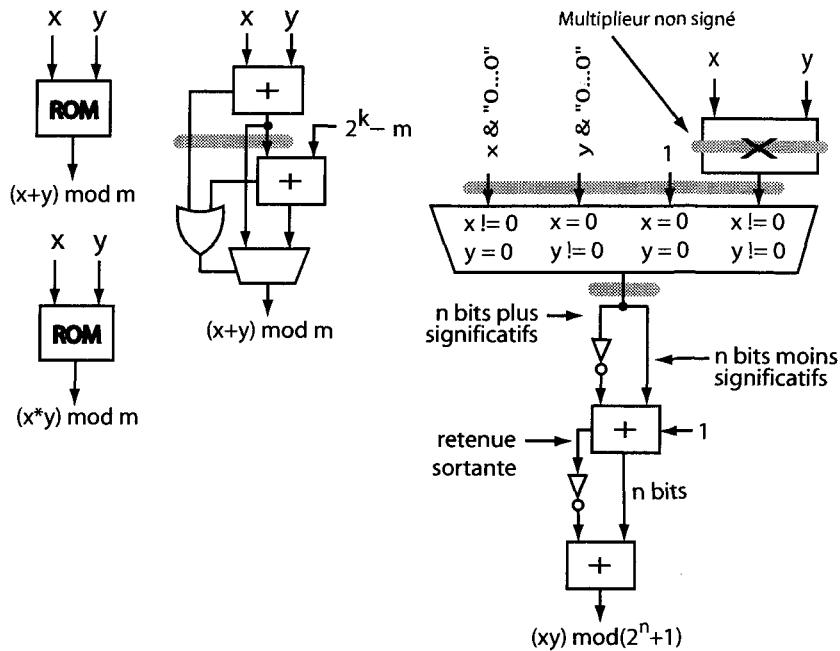

| 2.11 | Quelques additionneurs et multiplieurs modulaires . . . . .                                                  | 31 |

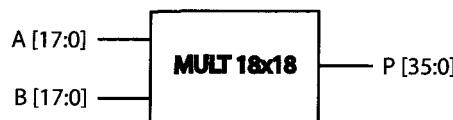

| 2.12 | Multiplieur 18x18 embarqué . . . . .                                                                         | 32 |

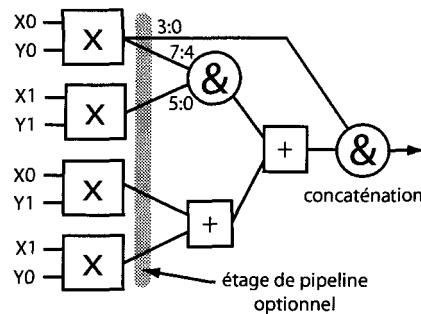

| 2.13 | Bloc DSP d'un FPGA Stratix d'Altera . . . . .                                                                | 33 |

| 2.14 | Multiplieur de 36 bits réalisé au moyen de multiplieurs 18x18 embarqués                                      | 33 |

| 2.15 | Diviseur séquentiel restaurant . . . . .                                                                     | 35 |

| 2.16 | Diviseur séquentiel non restaurant . . . . .                                                                 | 35 |

| 2.17 | Chronogramme de l'exemple 1 . . . . .                                                                        | 37 |

| 2.18 | Chronogramme de l'exemple 2 . . . . .                                                                        | 37 |

| 2.19 | Diviseur série-parallèle non restaurant utilisant les lignes de propagation<br>de retenues dédiées . . . . . | 37 |

|                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------|----|

| 2.20 Correspondance directe d'un diviseur série-parallèle non restaurant avec l'architecture physique d'un FPGA . . . . . | 39 |

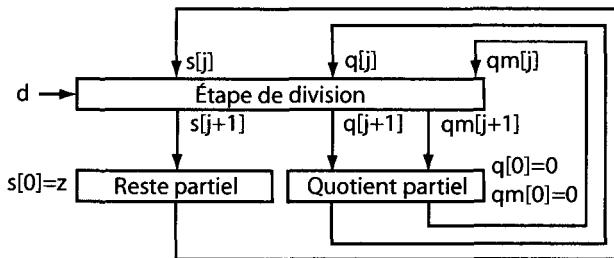

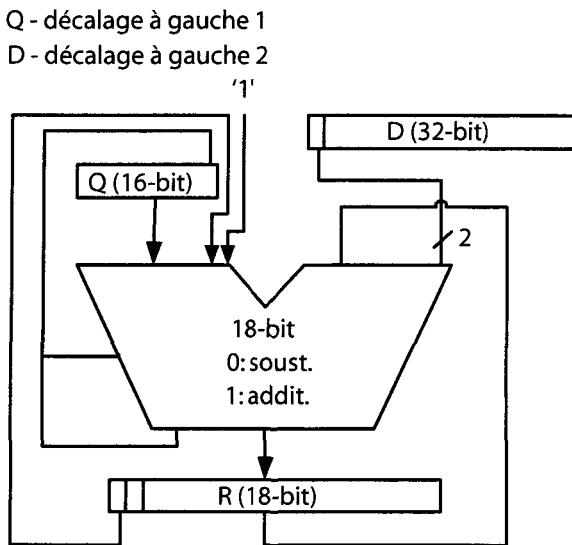

| 2.21 Étape de division SRT en base 4 . . . . .                                                                            | 41 |

| 2.22 Mise en œuvre itérative de la division SRT . . . . .                                                                 | 41 |

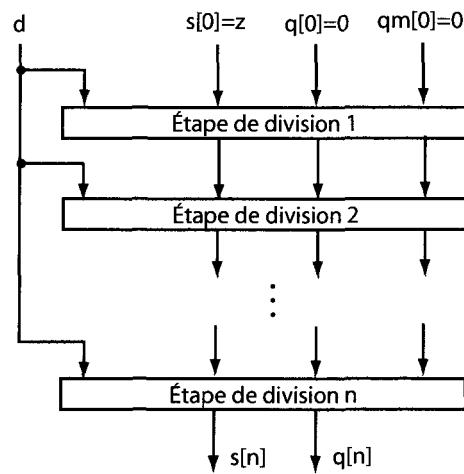

| 2.23 Mise en œuvre de la division SRT sous forme de tableau . . . . .                                                     | 42 |

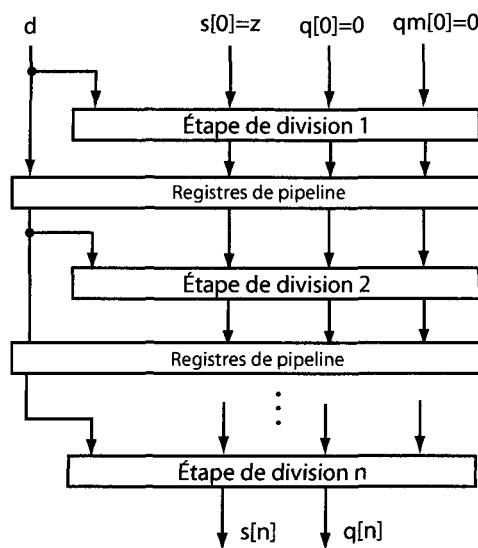

| 2.24 Mise en œuvre de la division SRT pipelinée . . . . .                                                                 | 42 |

| 2.25 Racine carrée non restaurante . . . . .                                                                              | 43 |

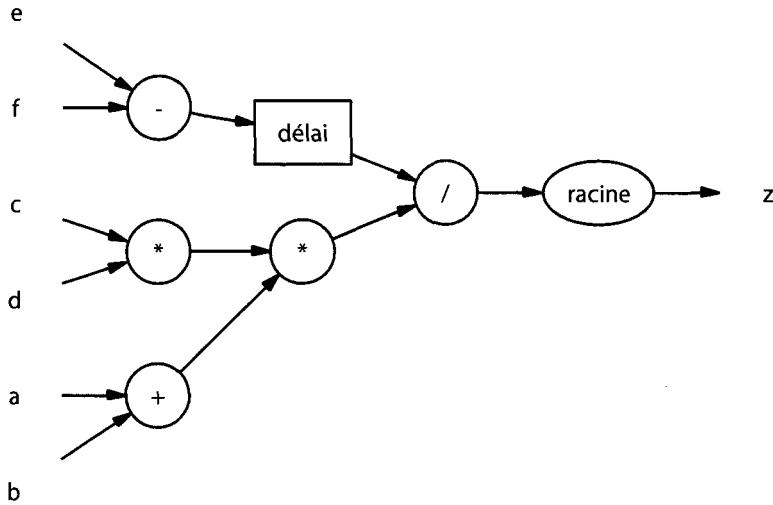

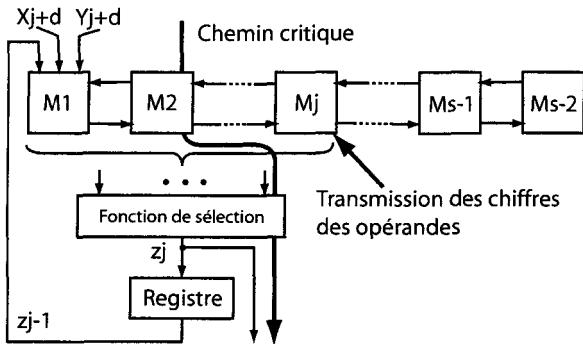

| 2.26 Exemple de réseau d'opérateurs en-ligne . . . . .                                                                    | 47 |

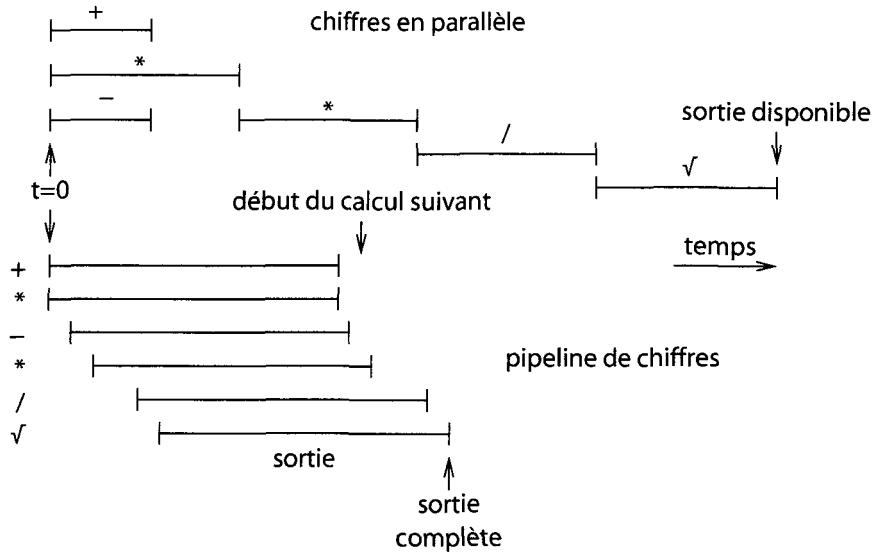

| 2.27 Déroulement temporel comparé d'un calcul parallèle et d'un calcul en-ligne                                           | 48 |

| 2.28 Structure générale d'un opérateur en-ligne . . . . .                                                                 | 49 |

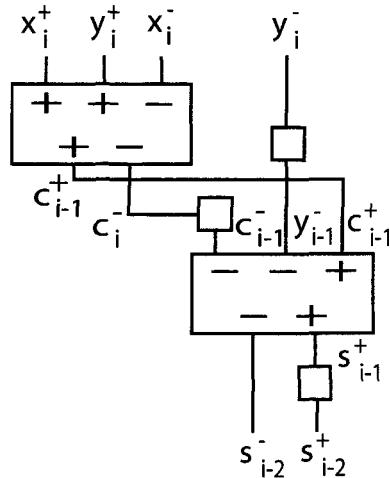

| 2.29 Additionneur en-ligne fait de deux cellules PPM . . . . .                                                            | 51 |

| <br>                                                                                                                      |    |

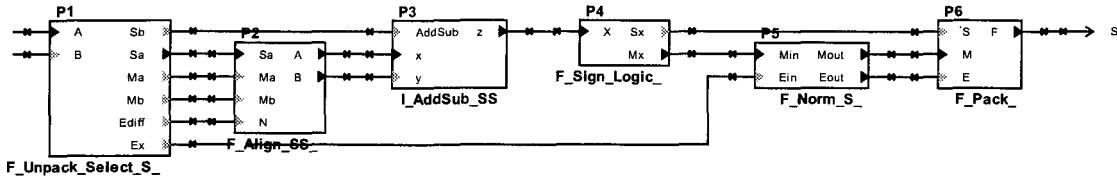

| 3.1 Schéma de conception des composants F_Add_SS et F_Sub_SS . . . . .                                                    | 63 |

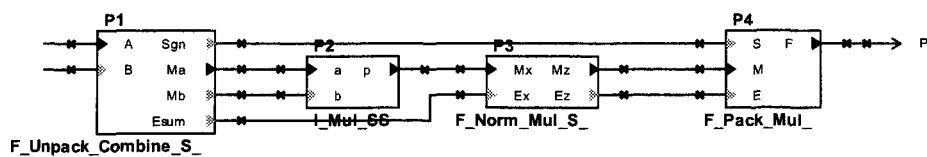

| 3.2 Schéma de conception du composant F_Mul_SS . . . . .                                                                  | 65 |

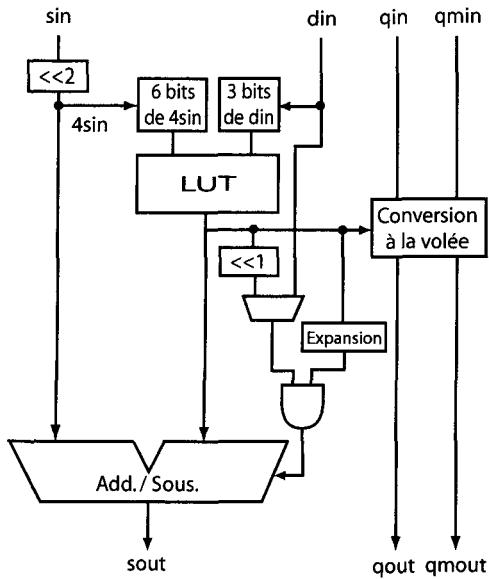

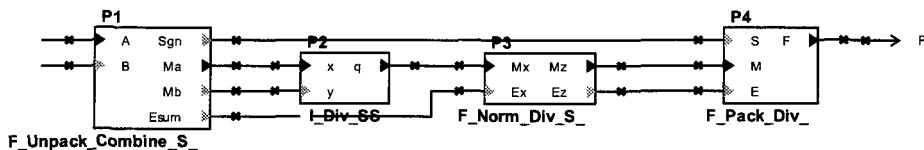

| 3.3 Schéma de conception du composant F_Div_SS . . . . .                                                                  | 67 |

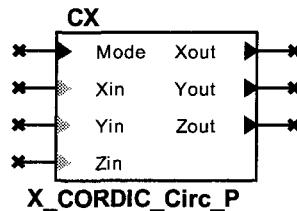

| 3.4 Interface du composant psC_X_CORDIC_Circ_p . . . . .                                                                  | 68 |

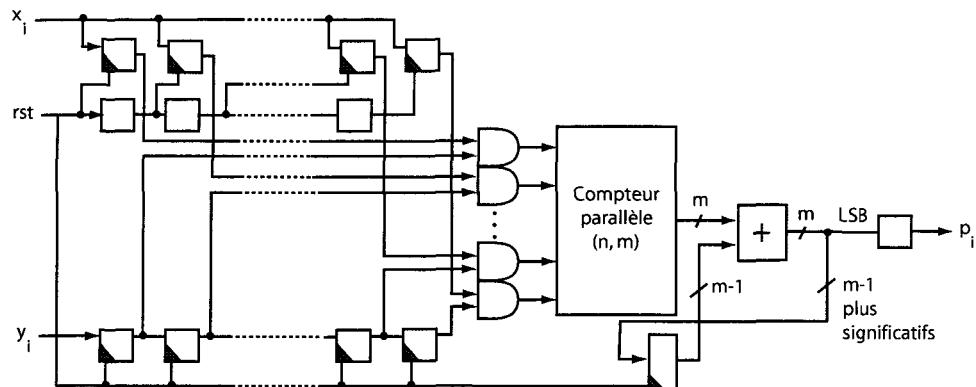

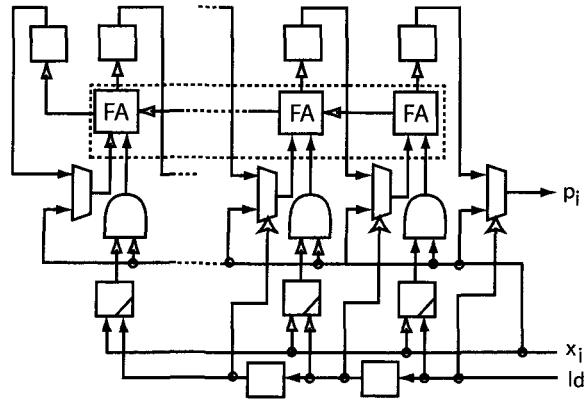

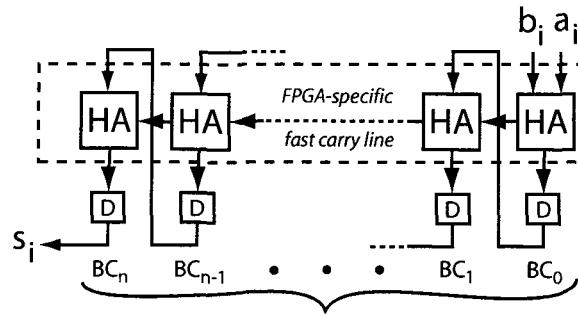

| 3.5 Additionneur MSBF non redondant utilisant la logique de propagation rapide de retenues . . . . .                      | 72 |

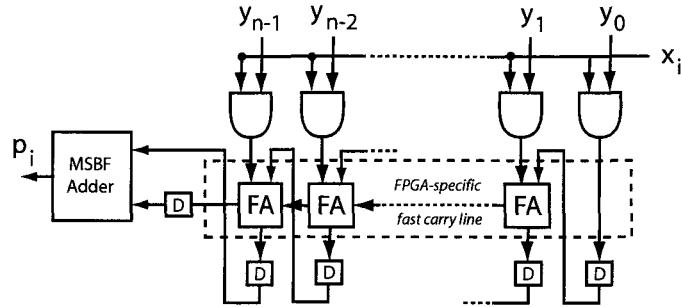

| 3.6 Multiplieur série-parallèle MSBF non redondant . . . . .                                                              | 73 |

# Liste des tableaux

|      |                                                                                                                  |    |

|------|------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Comparaison de la taille des opérateurs et de la période d'horloge d'opérateurs en-ligne et parallèles . . . . . | 49 |

| 3.1  | Comparaison de différentes largeurs d'additionneurs standards sur FPGA (résultats de synthèse) . . . . .         | 61 |

| 3.2  | Résultats de synthèse des additionneurs et soustracteurs codés en psC .                                          | 62 |

| 3.3  | Multiplieur 32 bits à base de blocs MULT18x18 (sortie enregistrée) . .                                           | 63 |

| 3.4  | Multiplieur 32 bits à base de LUT (sortie enregistrée) . . . . .                                                 | 64 |

| 3.5  | Multiplieurs pipelinés à base de blocs MULT18x18 (Spartan-3 xc3s5000-4)                                          | 64 |

| 3.6  | Multiplieurs pipelinés à base de LUT (Spartan-3 xc3s5000-4) . . . .                                              | 64 |

| 3.7  | Résultats de synthèse des multiplieurs codés en psC . . . . .                                                    | 65 |

| 3.8  | Mises en œuvre de diviseurs-tableaux 32 bits (Virtex II xc2v1000-6) [83]                                         | 66 |

| 3.9  | Mises en œuvre de diviseurs itératifs 32 bits (Virtex II xc2v1000-6) .                                           | 66 |

| 3.10 | Résultats de synthèse des diviseurs codés en psC . . . . .                                                       | 67 |

| 3.11 | Résultats de synthèse du processeur CORDIC codé en psC . . . . .                                                 | 69 |

| 3.12 | Résultats de synthèse pour l'additionneur MSBF non redondant . . .                                               | 74 |

| 3.13 | Résultats de synthèse pour le multiplieur MSBF série-parallèle non redondant . . . . .                           | 74 |

| 3.14 | Résultats de synthèse pour le multiplieur MSBF non redondant entièrement sériel . . . . .                        | 75 |

| 3.15 | Résultats de synthèse des multiplieurs série-parallèle et en-ligne de [42]                                       | 75 |

| 4.1  | Puissance de calcul : additionneurs et multiplieurs en nombre égal . .                                           | 80 |

| 4.2  | Puissance de calcul : 2 additionneurs pour 1 multiplieur . . . . .                                               | 81 |

| 4.3  | Puissance de calcul : 10 additionneurs pour 1 multiplieur . . . . .                                              | 81 |

| 4.4  | Puissance de calcul : 5 additionneurs, 5 multiplieurs et 1 diviseur . .                                          | 82 |

| 4.5  | Puissance de calcul : opérateurs à virgule flottante de J. Detrey . . .                                          | 84 |

|     |                                                                               |    |

|-----|-------------------------------------------------------------------------------|----|

| 4.6 | Puissance de calcul : opérateurs à virgule flottante de K. Underwood . . . .  | 84 |

| 4.7 | Puissance de calcul : opérateurs à virgule flottante en-ligne de R. McIlhenny | 84 |

# Résumé

Cette recherche a été effectuée dans le cadre du développement du langage psC, de la compagnie saguenéenne Novakod Technologies, un projet majoritairement subventionné par l'Agence spatiale canadienne, et auquel ont collaboré des chercheurs de l'Université du Québec à Chicoutimi.

Le langage psC est un nouveau langage, supporté par un compilateur et un environnement intégré de développement, visant à faciliter la programmation de systèmes en temps réel, parallèles et reconfigurables.

L'objectif de cette recherche était d'étudier, de réaliser et de comparer divers compromis espace-temps fondamentaux, dans le but de permettre au langage psC d'accélérer des calculs numériques habituellement réalisés par logiciel, au moyen de circuits reconfigurables, et à développer une bibliothèque d'opérateurs arithmétiques matériels, de fonctions logiques et de fonctions mathématiques répondant, dans la mesure du possible, aux besoins de psC dans le cadre de ce projet. Notre étude dresse, pour la première fois, un panorama général des mises en œuvres d'opérateurs arithmétiques sur FPGA et apporte plusieurs constats importants.

Une bibliothèque de composants arithmétiques et de fonctions élémentaires a été développée, testée, évaluée et livrée. Le développement de cette bibliothèque a donné lieu à une participation importante au débogage et à l'amélioration des outils psC, qui étaient eux-mêmes en cours de développement.

Les résultats de notre recherche nous ont permis de découvrir une architecture simple et économique pour la mise en œuvre sérielle des opérations arithmétiques avec des opérandes et des résultats circulant bit de poids fort en tête. Cette architecture présente un intérêt pour la réalisation d'opérateurs arithmétiques à virgule flottante économiques.

Nous présentons une stratégie d'analyse pour l'estimation de la puissance de calcul d'un réseau d'opérateurs massivement parallèle.

Les résultats de cette étude seront repris, dans le cadre d'un doctorat, en vue de réaliser un contrôleur sur puce haute-performance pour la commande de moteurs AC à induction.

# Abstract

This research has been conducted within the framework of the development of the psC language, from Novakod Technologies, a Saguenay company, a project mainly subsidized by the Canadian Space Agency, and to which researchers from the University of Quebec at Chicoutimi have collaborated.

The psC language is a new language, supported by a compiler and an integrated development environment, aiming to facilitate real-time, parallel and reconfigurable systems programming.

The objective of this research was to study, implement, and compare various fundamental space-time tradeoffs, in order to allow the psC language to accelerate numerical computations usually carried out by software, by means of reconfigurable circuits, and to develop a library of hardware arithmetic operators, logic and mathematical functions answering, as far as possible, psC's needs in the context of this project.

Our study draws up, for the first time, a general panorama of arithmetic operator implementations on FPGA, and brings several significant findings.

A library of arithmetic components and elementary functions was developed, tested, evaluated and delivered. The development of this library have led to a significant participation in the debugging and the improvement of the psC tools, which were themselves under development.

Our research results enabled us to discover a simple and economic architecture for the serial implementation of arithmetic operations with the operands and results flowing in a most-significant-bit-first manner. This architecture is certainly of interest for the realization of economic floating point operators.

The results of this study will further serve, in the context of a doctorate, in order to devise a high-performance system-on-chip AC induction motor controller.

# Remerciements

Je remercie mon directeur et mon codirecteur de recherche, Luc Morin et Rachid Beguenane, pour leurs suggestions et leur support au cours de cette recherche, et la compagnie Novakod Technologies de nous avoir confié ce projet.

Un merci particulier va au professeur Beguenane, qui a consacré un soin et des ressources considérables afin de rehausser ma formation en micro-électronique ainsi qu'en recherche. Notamment, en sa qualité de représentant de CMC Microsystems pour l'UQAC, il m'a permis de participer à plusieurs séminaires et ateliers de formation organisés par CMC. Les gens de CMC font un travail magnifique, et leur support, le matériel et les outils de développement qu'ils fournissent aux chercheurs du domaine des micro-systèmes, encouragent et rehaussent des recherches telles que celle-ci.

Un merci particulier va également à Jean-Luc Beuchat, du projet Arénaire, pour ses conseils et sa collaboration, et pour m'avoir initié à l'arithmétique modulaire matérielle pour la cryptographie.

Le support financier de Novakod Technologies à l'Université du Québec à Chicoutimi, m'employant en tant qu'assistant de recherche du professeur Beguenane, au sein du groupe ERMETIS, a été crucial pour la réussite de ce projet.

Enfin, merci à mon collègue Éric Larouche pour ses conseils, aux membres du comité d'évaluation, D. Audet, R. Beguenane, O. Ait Mohamed, et L. Morin, et à tous ceux qui, de près ou de loin, ont contribué à la réussite de ce mémoire.

Chicoutimi, Québec

Mai 2006

Stéphane Simard

## Liste des abréviations

|           |                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------|

| ASIC      | Circuit intégré à application spécifique<br>(de l'anglais : Application-Specific Integrated Circuit) |

| BS        | Borrow-save                                                                                          |

| C2        | Complément à 2                                                                                       |

| CL        | Cellule logique                                                                                      |

| CLB       | Bloc logique configurable (de l'anglais : Configurable Logic Bloc)                                   |

| CORDIC    | COordinate Rotation DIgital Computer                                                                 |

| DSP       | Processeur de signaux numériques<br>(de l'anglais : Digital Signal Processor)                        |

| FPGA      | Réseau prédiffusé programmable par l'utilisateur<br>(de l'anglais : Field-Programmable Gate Array)   |

| GOPS      | Milliards d'opérations par seconde (GOPS)                                                            |

| ITGE      | Intégration/intégré à très grande échelle (anglais : VLSI)                                           |

| LUT       | Table de conversion matérielle (de l'anglais : Look-Up Table)<br>4-LUT : LUT à quatre entrées        |

| MAC       | Multiplieur-accumulateur                                                                             |

| MEPS      | Millions d'échantillons par seconde                                                                  |

| MOPS      | Millions d'opérations par seconde (MOPS)                                                             |

| MSBF      | Bit de poids fort en tête (de l'anglais : most significant bit first)                                |

| MULT18x18 | Bloc multiplieur ITGE embarqué $18 \times 18$ bits                                                   |

| PAM       | Mémoire active programmable<br>(de l'anglais : Programmable Active Memory)                           |

|       |                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------|

| PPOE  | Programmation Parallèle Orientée Événements                                                      |

| psC   | Parallel Synchronous C                                                                           |

| RCAD  | Retenue conservée–addition–décalage                                                              |

| RPAD  | Retenue propagée–addition–décalage                                                               |

| RVM   | Machine virtuelle Rodin (de l'anglais : Rodin Virtual Machine)                                   |

| SIMD  | Single Instruction Multiple Data                                                                 |

| SISO  | Shift-in, shift-out (registre à décalage série, utilisé comme simple délai)                      |

| VHDL  | VHSIC Hardware Description Language                                                              |

| VHSIC | Very-High-Speed Integrated Circuit<br>(circuit intégré pouvant fonctionner à très haute vitesse) |

# Chapitre 1

## Introduction

## 1.1 Le langage psC

Le langage psC se veut le premier environnement de programmation entièrement parallèle basé sur un nouveau paradigme nommé *programmation parallèle orientée événement* (PPOE). Le langage et son paradigme découlent de la recherche du professeur Luc Morin, de l'Université du Québec à Chicoutimi (UQAC), président et fondateur de Novakod Technologies inc., une compagnie en démarrage, fondée en 2003, qui développe et commercialise désormais les outils de développement psC. En tant que professeur, M. Morin est, de plus, le directeur de la présente recherche, et le professeur Rachid Beguenane, également de l'UQAC, en est le codirecteur.

L'approche de psC, entièrement parallèle, consiste en un réseau de composants reliés par des fils via des ports d'entrée/sortie, et ne comporte pas les séquences d'instructions ni les boucles propres aux langages informatiques. Tout comme en conception numérique, les séquences et les boucles doivent être réalisées par des composants branchés en série ou par des machines à états finis. Puisque, en psC, le parallélisme est explicite, le concepteur a tout avantage à maîtriser l'algorithmique parallèle en plus de posséder au moins quelques notions de conception numérique.

Le langage se distingue cependant des langages de description matérielle en ce qu'il est entièrement synchrone et apporte des constructions et des types de données de plus haut niveau. Les différents blocs de code parallèle au sein des composants sont déclenchés par des *événements* arrivant sur les ports d'entrée déclarés *actifs*. Un signal d'événement est une impulsion circulant de port en port sur un fil implicite associé à toute donnée. Les ports actifs laissent passer les événements, alors que les ports *passifs* ne les laissent pas passer. Les événements transmis sur les ports de sortie actifs d'un composant sont gérés explicitement par le concepteur.

On trouve des explications plus détaillées dans le guide du programmeur psC [72].

## 1.2 Historique

L'origine de psC remonte à 1984, à l'Université Concordia, alors que M. Morin travaillait à la rédaction de sa thèse de doctorat en informatique intitulée : *A modeling technique for specification and simulation of digital systems.*

Dans les années 1990, une version modifiée du langage, connue sous le nom de Rodin, ayant perdu ses caractéristiques purement fonctionnelles tout en conservant sa syntaxe postfixe, vise désormais à faciliter la programmation des systèmes concurrents et en temps réel sur micro-processeur.

L'approche par composants parallèles orientée événements a été conçue en 1997. Le parallélisme était alors simulé par une machine virtuelle (la *Rodin Virtual Machine* — RVM) qui interprétabit un code machine compilé. Par la suite, le langage a évolué lentement grâce à des projets confiés à des étudiants de l'UQAC.

En janvier 2003, M. Morin reçoit une première subvention de l'Agence Spatiale Canadienne, dans le cadre du Programme de développement des technologies spatiales (projet PDTS-2003), donnant le coup d'envoi d'une première phase des développements qui vont conduire au projet actuel. À ce stade, le langage ne comporte que des types de données entiers. Un groupe d'étudiants est embauché dans le cadre de stages/projets au Laboratoire de développement de logiciels (LDL) de l'UQAC afin d'ajouter d'une vaste gamme de nouveaux types et d'apporter diverses améliorations. Concomitamment, un stage/projet du présent auteur donne lieu à un travail de recherche menant à la conception et au développement d'exemples d'applications du langage Rodin à l'algorithme parallèle et à la commande en temps réel.

Suite aux résultats obtenus, M. Morin décide de commercialiser le produit. Il entame une procédure de prise de brevet et fonde, à Chicoutimi, la compagnie Novakod Technologies, embauchant 4 des étudiants du LDL, désormais gradués.

Il est important de souligner les efforts de tous ceux qui ont contribué, de près ou de loin, et ce, parfois gracieusement, aux travaux de recherche et de développement qui ont conduit à cette commercialisation. La liste est longue, mais, parmi les contributeurs connus du présent auteur, il convient de mentionner, notamment, ceux dont la contribution a immédiatement précédé la commercialisation (par ordre alphabétique) : François Blackburn, Jean-Michel Fortin, Bruno Gagnon, Michel Héraud, Éric Larouche, Patrick Latour, Jean-François Michaud, l'auteur du présent mémoire, Stéphane Simard, Simon Tremblay, ainsi qu'une foule d'autres contributeurs.

En 2004–05, Novakod obtient un contrat majeur de l'Agence Spatiale Canadienne, et le projet actuel, que l'on conviendra d'appeler simplement le Projet, est lancé. Au cours du Projet, le compilateur est réécrit en entier pour introduire une nouvelle syntaxe, proche de celle du langage C. Le langage subit alors une transformation radicale et devient psC (Parallel Synchronous C). L'objectif visé est désormais de faciliter la programmation des systèmes reconfigurables à base de puces FPGA, et l'environnement de développement psC, appelé Novakod Studio, entend supporter les applications parallèles et en temps réel tant sur les plateformes à FPGA que celles à micro-processeurs.

### 1.3 Les FPGA

Les FPGA (de l'anglais : *field-programmable gate arrays*), ou *réseaux prédiffusés programmables*, se composent d'un grand nombre de blocs logiques combinatoires, mis en œuvre par des multiplexeurs, des tables de conversion et des registres, pouvant être reprogrammés et interconnectés les uns aux autres un nombre arbitraire de fois dans n'importe quelle configuration. Une fois conçues les fonctions logiques de configuration, la procédure d'adaptation est très rapide et peu coûteuse comparativement au processus traditionnel de conception sur mesure d'un circuit intégré.

Les structures de calcul à grain fin présentes dans les FPGA conviennent bien à la réalisation matérielle d’algorithmes pouvant exploiter un parallélisme massif au niveau du bit ou s’adaptant bien à des architectures hautement pipelinées. La flexibilité architecturale des FPGA permet aussi aux concepteurs d’ajuster les largeurs de données afin de s’adapter à différents besoins d’un même algorithme. Les progrès récents ont d’ailleurs fait des FPGA des plateformes idéales pour la mise en œuvre du calcul reconfigurable, qui consiste à adapter sur le vif un circuit à des calculs complexes.

Réalisés sur FPGA, des calculateurs dédiés et des machines à structure massivement parallèle d’architecture SIMD (de l’anglais : *single instruction, multiple data*), capables de traiter une instruction sans affectation préalable des processeurs de traitement, peuvent potentiellement atteindre des performances du calibre d’un superordinateur pour un certain nombre d’applications spécifiques, et ce, à seulement une fraction du prix [18]. Ces calculateurs massivement parallèles peuvent exploiter les avantages d’une architecture serielle afin d’obtenir un pipeline à grain très fin tout en minimisant la taille des éléments individuels de traitement. Comme les architectures sérielles tendent à faire grand usage de registres tout en ne nécessitant que peu de ressources de routage, elles produisent habituellement des réalisations sur FPGA à la fois économiques et relativement rapides et efficaces.

## 1.4 Problématique

L’arithmétique sur FPGA, à cause des contraintes technologiques, a longtemps été restreinte aux opérations sur les entiers et aux opérations sur les nombres fractionnaires à virgule fixe. Au stade actuel du progrès technologique, grâce à leur architecture configurable au niveau du bit, il est devenu possible de réaliser efficacement sur FPGA une vaste gamme d’opérations arithmétiques et de fonctions mathématiques.

Les opérateurs arithmétiques se classifient en deux grands types d'architectures : les architectures parallèles et les architectures sérielles. Dans les microprocesseurs courants, les opérations arithmétiques de base s'effectuent en parallèle, et tous les bits des opérandes sont traités en même temps. À l'opposé, lorsque l'on effectue des calculs sur papier, on procède de manière *sérielle*, c'est-à-dire chiffre à chiffre, en progressant soit de droite à gauche (chiffres de poids faible en tête), soit de gauche à droite (chiffres de poids fort en tête), selon la méthode employée.

Lorsqu'une application particulière nécessite une grande précision ou un grand nombre d'opérateurs de calcul, la surface occupée par un module dans un circuit peut devenir un critère aussi important, sinon plus, que sa vitesse. L'arithmétique sérielle est bien adaptée à de telles applications, car elle a l'avantage d'économiser l'espace et de minimiser les interconnexions, les chiffres étant calculés et émis un à un. Dans d'autres applications, par contre, où c'est la vitesse d'un opérateur isolé qui importe, le recours à une mise en œuvre parallèle, habituellement coûteuse, peut s'avérer le seul moyen d'atteindre la vitesse requise.

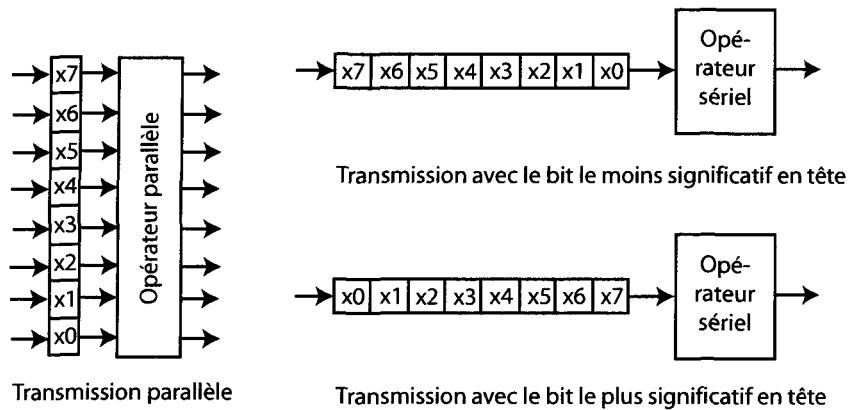

FIG. 1.1 – Transmission parallèle versus serielle

En arithmétique parallèle, les bits des opérandes et des résultats circulent en parallèle, ce qui permet, bien qu'à un coût élevé, d'obtenir une haute performance, car

les modules arithmétiques parallèles occupent un espace considérable sur une puce et il est par conséquent nécessaire de les réutiliser au maximum. En arithmétique sérielle, les opérandes et les résultats circulent en série, chiffre à chiffre, à travers les modules. La direction de circulation des chiffres engendre les deux *modes d'opération* sériels déjà mentionnés, selon que la circulation s'effectue chiffre de poids faible (de droite à gauche) ou chiffre de poids fort (de gauche à droite) en tête (Fig. 1.1).

Additionner sériellement deux nombres chiffre de poids faible en tête est particulièrement simple. Il faut cependant tenir compte du fait que la retenue d'une addition se propage toujours de droite à gauche et que le contraire n'est pas possible. À mesure que chaque paire d'opérandes est reçue, il suffit de calculer un chiffre de somme et un autre de retenue. Le chiffre de retenue est ensuite additionné à la prochaine paire d'opérateurs, et ainsi de suite. La réalisation d'un tel additionneur ne nécessite qu'un simple additionneur complet et une bascule. La multiplication est essentiellement une somme de produits partiels, et, étant donné le sens de la propagation de retenue dans les additions, elle, fonctionne, elle aussi, naturellement chiffre de poids faible en tête. Le mode de calcul sériel chiffre de poids faible en tête semble donc, a priori, être une manière simple, rapide et économique de calculer, car elle procède dans le même sens que la propagation des retenues.

Si l'arithmétique sérielle présente certains avantages, en particulier parce qu'elle offre une économie d'espace considérable, son utilisation et ses performances sont toutefois limités par deux caractéristiques fondamentales contradictoires, contradiction qui est à l'origine de difficultés majeures ayant entraîné des décennies de recherches plus ou moins fructueuses, sachant bien que l'on ne pourrait jamais arriver qu'à des solutions de compromis. Effectuer les opérations d'addition et de multiplication dans le sens contraire de la propagation des retenues entraîne des complications qui affectent

considérablement le coût et la performance des mises en œuvre. Or, il n'est pas possible d'effectuer les opérations de division et d'extraction de la racine carrée en commençant par les chiffres les moins significatifs, car les chiffres les moins significatifs du résultat dépendent des chiffres les plus significatifs des opérandes. Il en résulte une incompatibilité intrinsèque, en arithmétique serielle, entre les modules de la famille de l'addition et de la multiplication, d'un côté, et, de l'autre, les modules de la famille de la division et des fonctions élémentaires, dont l'extraction de la racine carrée.

Dans certaines applications, telles que le traitement de signal, où seuls des additionneurs, des soustracteurs, des multiplieurs et des modules d'élévation au carré sont nécessaires, des calculs chiffre de poids faible en tête peuvent s'avérer intéressants [32].

Il faut cependant considérer le fait que le résultat d'une multiplication de deux nombres de  $N$  chiffres comporte  $2N$  chiffres, de sorte que le nombre de chiffres du produit final croît de manière exponentielle lorsque l'on fait des multiplications répétées. Dans le cas d'un multiplieur sériel produisant les chiffres les moins significatifs en premier (chiffre de poids faible en tête), il faut attendre au moins  $2N - 1$  cycles d'horloge, avant que le chiffre le plus significatif du produit ne soit émis en sortie, ce qui nécessite une mise en tampon durant tout le processus.

Si l'on fait abstraction des problèmes de compatibilité entre différents types d'opérateurs, un traitement en série est beaucoup plus économique en espace qu'un traitement en parallèle, mais prend, en contrepartie, un plus grand nombre de cycles d'horloge pour effectuer une opération isolée. La performance de différents réseaux de modules parallèles varie beaucoup comparativement à celle de réseaux sériels équivalents, et peut même, dans certains cas, être surpassée par un réseau sériel, pourvu que ce dernier ait une profondeur suffisante et que la latence des modules sériels ainsi cascadés soit relativement faible.

Comme les modules sériels tendent à faire grand usage de registres tout en ne demandant que peu de ressources de routage, ils donnent habituellement lieu à des réalisations sur FPGA à la fois efficaces et rapides. Par la reconfiguration de leur degré de sérialisation, les modules sériels peuvent s'adapter aux exigences de diverses applications en termes de performances ou de ressources, ainsi qu'aux variations des conditions d'opération ou aux différentes phases de calcul d'une même application. Le choix de la largeur de chiffre influe aussi grandement sur le coût et les performances de la mise en œuvre.

Pour améliorer la fréquence d'horloge maximale d'opérateurs parallèles, qui tendent, de par leur nature même, à comporter un long chemin critique, on a généralement recours à une technique nommée *pipelinage*, qui consiste à insérer des étages de bascules au sein d'un circuit afin de scinder en tranches plus courtes le long chemin combinatoire qui le traverse. Le principal intérêt du pipelinage est d'obtenir un fort débit de calcul. Un module ainsi pipeliné aura une latence initiale de cycles d'horloge égale au nombre d'étages de pipeline, mais produira ensuite à chaque cycle, à fréquence élevée, un résultat en parallèle à sa sortie.

Du côté des opérateurs sériels, puisqu'ils commencent à calculer des chiffres du résultat d'après une entrée partielle des chiffres des opérandes, ceux-ci peuvent être pipelinés au niveau du chiffre, permettant ainsi, dans certains cas, de réduire la latence lors du calcul d'expressions composées, comparativement à une mise en œuvre parallèle.

L'arithmétique en-ligne est une arithmétique serielle ayant la particularité d'effectuer les calculs en commençant par les chiffres les plus significatifs (chiffre le plus significatif en tête). Elle favorise le pipelinage des opérations arithmétiques, qui peuvent alors s'effectuer simultanément, à mesure que chaque chiffre devient disponible, permettant ainsi de réduire le temps de calcul de longues séquences d'opérations tout en minimisant les interconnexions entre modules. Elle tente, de plus, de solutionner les problèmes

mentionnés ci-dessus découlant du sens de propagation des retenues et de l'incompatibilité des deux différents groupes d'opérateurs arithmétiques entre eux. Nous verrons plus loin que, malgré un arsenal de sophistications théoriques imposant, l'arithmétique en-ligne n'atteint ce dernier objectif que partiellement.

## 1.5 Objectifs et méthodologie de recherche

Le Projet commandait l'étude des compromis espace-temps dans les systèmes reconfigurables en vue d'ouvrir la voie au développement de modules arithmétiques et de fonctions mathématiques pour FPGA dans le langage psC. En supportant, en psC, la synthèse de réseaux d'arithmétique dédiés sur FPGA, la compagnie Novakod entend permettre d'accélérer des algorithmes tournant habituellement sur microprocesseur. Il ne s'agit pas là, cependant, de synthèse directe à partir d'une description algorithmique classique, mais plutôt d'une approche s'apparentant à la conception numérique.

Cette recherche visait à étudier, à mettre en œuvre et à comparer des compromis espace-temps fondamentaux, dans le but de comprendre comment accélérer des calculs numériques grâce à des mises en œuvre sur FPGA, et à développer un ensemble d'opérateurs arithmétiques, de fonctions logiques et de fonctions mathématiques de base.

La liste d'opérateurs arithmétiques à développer et les choix de conception ont fait l'objet de discussions dans le cadre de multiples réunions, et reflètent strictement les directives reçues, fondées sur la base des exigences et des contraintes du Projet. Ces réunions se sont généralement déroulées en présence d'un représentant de la compagnie, du directeur de la compagnie et directeur de recherche à l'UQAC, ainsi que du codirecteur de recherche et superviseur du Projet pour l'UQAC.

La cueillette des données s'est déroulée concurremment au développement. Les données consistent en des mesures permettant d'évaluer et de comparer le coût en temps et

en espace des diverses mises en œuvre. Ces mesures sont basées sur des caractéristiques architecturales et sur des résultats de synthèse fournis par les outils de développement commerciaux, incluant, pour chaque opérateur arithmétique ou fonction élémentaire, sa latence (en tops d'horloge), son débit maximal (en MHz) et son coût en cellules logiques (CL).

Dans une première étape, une revue du domaine de l'arithmétique des ordinateurs a été effectuée, avec emphase sur les réalisations sur FPGA. Cette revue a démontré, dans un premier temps, que la mise en œuvre d'opérateurs arithmétiques et de fonctions élémentaires parallèles et en série sur FPGA avait suffisamment d'assises dans la littérature et était réalisable au stade actuel du progrès technologique.

Outre l'apport d'une revue du domaine, une part importante de la contribution du présent travail consiste dans la mise en œuvre et la comparaison de plusieurs architectures d'opérateurs arithmétiques et de fonctions élémentaires, constituant, dans le cadre du Projet, une bibliothèque de modules optimisés pour FPGA et codés en psC.

Les critères que nous définissons pour évaluer la performance et faire des comparaisons entre différentes mises en œuvre, sont les suivants :

- *Uniformité* : La capacité d'interconnecter des modules individuels sans avoir à introduire des structures intermédiaires pour reformater les données ;

- *Espace* : Le nombre d'unités physiques occupées par un module sur une puce. Pour les circuits réalisés sur FPGA étudiés dans le présent mémoire, l'espace est mesuré en cellules logiques (CL), constituées chacune d'une table de vérité (LUT) à 4 entrées, d'une bascule D et d'éléments logiques destinés à assurer la propagation d'une retenue ;

- *Débit* : Le débit d'un module est défini comme le nombre d'ensembles d'entrées qu'il peut traiter par unité de temps ;

- *Latence* : La latence est le nombre d’unités de temps entre l’application d’entrées et l’obtention d’une sortie. Dans la littérature sur l’arithmétique en-ligne, la latence est souvent exprimée sous forme de *délai en-ligne*,  $\delta$ , mais la définition du délai en-ligne n’est pas compatible avec d’autres types d’arithmétique. Pour les mises en œuvre sérielles, nous définissons la latence comme le temps, en cycles d’horloge, séparant l’entrée du premier bit des opérandes de la sortie du dernier bit du résultat.

## Chapitre 2

# Revue de l'arithmétique des FPGA

Les FPGA sont devenus, au cours des dernières années, l'option favorite pour la mise en œuvre matérielle des systèmes numériques, car ils permettent d'adapter le matériel à une application donnée. Puisque les opérations arithmétiques sont les constituantes fondamentales des systèmes numériques, les spécificités de leur mise en œuvre dans la logique programmable a fait l'objet, jusqu'à présent, de recherches approfondies, et de nombreuses propositions ont été avancées en vue d'atteindre une haute performance pour des applications spécifiques. J.-L. Beuchat et A. Tisserand ont rédigé, en 2004, un chapitre de livre sur la mise en œuvre des opérateurs arithmétiques sur FPGA [26].

Il convient de remarquer que les modèles de délais et les analyses de coût développés pour la conception de circuits intégrés à application spécifique (ASIC) ne sont pas utiles pour la conception et la réalisation de dispositifs sur FPGA [47, 108]. Si les unités de mesures utilisées en conception ITGE sont le nombre de portes logiques et leur délai, des mesures de performance données en termes du nombre d'éléments logiques configurables et des délais logiques et de routage sont plus appropriées à la terminologie FPGA.

## 2.1 Arithmétique parallèle

Les contributions à l'arithmétique parallèle sont abondantes, et il est bon de consulter un ouvrage de référence tel que [40] pour en avoir un panorama complet.

R. Zimmermann [109] a développé, en VHDL, une bibliothèque de modules arithmétiques parallèles paramétrisables. Cette bibliothèque, indépendante de la plateforme, est dans le domaine public et elle fournit, pour ASIC, des circuits dont la performance est comparable aux bibliothèques commerciales, mais avec une plus grande flexibilité et une plus grande diversité d'opérateurs arithmétiques. Cette bibliothèque se limite toutefois aux opérations sur les entiers et n'est pas optimisée pour FPGA avec logique de propagation de retenues dédiée.

D'autres mises en oeuvres de modules d'arithmétique parallèle peuvent être obtenues sur le site <http://www.opencores.org> et d'une multitude d'autres sources. On en trouve plusieurs dans les références données ci-après.

## 2.2 Arithmétique sérielle

Les modules d'arithmétique sérielle ont une structure très simple et économique en espace. Les opérandes et les résultats des calculs circulent en série, chiffre à chiffre, à travers les modules. Un traitement sériel nécessite un plus grand nombre de cycles d'horloge qu'un traitement parallèle pour effectuer une opération, mais, excepté dans le cas de l'utilisation de blocs arithmétiques intégrés, un flux sériel épouse mieux la structure logique des FPGA [79].

L'approche sérielle conventionnelle, qui consiste à effectuer les calculs en commençant par les chiffres les moins significatifs, semble être une manière simple et rapide de calculer. Cependant, il existe une difficulté majeure : il n'est pas possible d'effectuer les opérations de division et de racine carrée en commençant par les chiffres les moins significatifs, car les chiffres les moins significatifs du résultat dépendent des chiffres les plus significatifs des opérandes. Il serait donc nécessaire de mémoriser tous les chiffres des opérandes jusqu'au dernier avant de pouvoir commencer à calculer le quotient. Si cet inconvénient, ajouté à l'incompatibilité intrinsèque qui existe entre l'addition et la multiplication, d'une part, et la division et la racine carrée, d'autre part, rend l'arithmétique sérielle bit de poids faible en tête non généralisable, cette dernière est néanmoins d'un usage facile, elle est compacte, et convient bien aux applications de traitement de signal, où seuls des additionneurs/soustracteurs, des multiplicateurs et/ou des opérateurs d'élévation au carré sont requis [32].

L'approche *en-ligne*, introduite par M.D. Ercegovac en 1977 [91], a la particularité

d'effectuer les calculs dans la direction opposée, en commençant par les chiffres les plus significatifs, ce qui est possible en ayant recours à une représentation numérique spéciale, dite *redondante*, permettant de ne pas avoir à propager les retenues. Il est possible d'effectuer en-ligne, de cette manière, une succession de plusieurs opérations reliées par un *pipeline de chiffres*. Le temps de calcul total du pipeline est alors la somme des temps de calcul des modules individuels, et les interconnexions entre modules sont minimales. L'approche en-ligne apporte une solution, bien qu'imparfaite, aux problèmes reliés à la compatibilité de l'addition et de la multiplication avec la division et la racine carrée [40, 77].

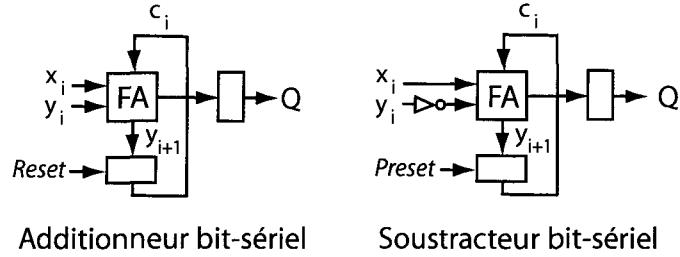

Les opérateurs sériels conventionnels utilisent une représentation numérique binaire standard et fonctionnent en mode chiffre de poids faible en tête. L'un des principaux intérêts de l'utilisation de ce type d'opérateurs vient du fait qu'un additionneur *bit-sériel* (Fig. 2.3) peut fonctionner à très haute fréquence, et que sa taille ne change pas selon la longueur des opérandes. De plus, les multiplicateurs bit-sériels sont les composants les plus critiques en traitement de signal haute fréquence, et sont aussi requis dans la plupart des applications parallèles.

L'un des premiers modules d'arithmétique bit-sérielles à avoir été proposé pour FPGA, en 1993, était systolique et utilisait une approche hybride où les bits d'un opérande entrent, à chaque deux cycles, en commençant au cycle 1, dans le tableau linéaire par la cellule d'extrême gauche, bit le moins significatif en tête, et les bits du second opérande entrent de manière similaire, en commençant au cycle 2, par la cellule d'extrême droite, bit de poids fort en tête [82]. Un tel module est économique au niveau de l'opérateur isolé, mais, à cause de son flux de données bidirectionnel en directions contraires, souffre d'un manque de régularité pour une utilisation en système.

L'objectif de ce chapitre est de faire une revue de l'état actuel de l'art de l'arith-

métique pour FPGA. Sont couverts, les opérateurs entiers d'addition/soustraction, de multiplication, d'élévation au carré, de division et de racine carrée, en parallèle et dans les deux modes sériels (chiffre de poids faible et chiffre de poids fort en tête).

## 2.3 Opérateurs entiers

### 2.3.1 Additionneurs et soustracteurs

Les FPGA modernes comportent des circuits de propagation de retenues très rapides permettant à une cellule logique de fonctionner comme un additionneur complet. Ces circuits n'occupent pas d'espace dans la logique standard, puisqu'ils sont réalisés à l'extérieur des LUTs [1,29,101]. Bien que la vitesse des additions sur FPGA soit toujours limitée par les circuits de propagation des retenues, ces circuits sont si rapides et efficaces comparativement à la logique à base de tables de vérité et aux délais d'interconnexion que les méthodes d'accélération traditionnelles utilisées en conception de circuits ITGE deviennent inutiles et coûteuses.

À cause de leur coût élevé, de leur complexité, de leurs structures irrégulières, de leur entrée et de leur sortance élevées et du fait qu'ils sont incapables de profiter de la logique de propagation de retenue dédiée, les additionneurs conventionnels à retenue anticipée (*carry-lookahead*) et à retenue sélectionnée (*carry-select*), qui donnent habituellement les mises en œuvre les plus rapides en conception ITGE, ne conviennent pas à une réalisation sur FPGA.

Dans une étude de 1998, Xing et Yu [108] ont comparé des additionneurs à retenue complétée *carry-complete* et à retenue ignorée and *carry-skip* optimisés pour FPGA, mais n'ont constaté aucune amélioration du délai pour des additionneurs de moins de 48 et 56 bits, respectivement, et ce, malgré une augmentation considérable de la

surface occupée. Selon cette étude, ce sont les additionneurs à retenue propagée qui ont le plus faible coût et le meilleur rapport performance/coût, à cause de leur structure très régulière et de leur utilisation efficace de la logique de propagation de retenues dédiée. Pour la réalisation d'additionneurs de plus de 48 bits, l'étude conclut que des additionneurs optimisés de type sélection–propagation–propagation (*select-ripple-ripple — (S-R-R)*) semblent être le meilleur choix lorsqu'un meilleur temps de fonctionnement est désiré, moyennant une augmentation raisonnable du coût en espace. Par ailleurs, une nouvelle structure d'additionneur à retenue ignorée, donnant des mises en oeuvre FPGA efficientes, a été introduite par Kantabutra et al. en 2002 [49].

Les soustracteurs se construisent à partir d'additionneurs avec retenue entrante, dont le second opérande passe par un circuit de complémentation (complément à 1). On peut construire un additionneur/soustracteur combiné en faisant en sorte qu'un même signal de sélection serve à la fois de retenue entrante et désactive (0) ou active (1) la complémentation. Selon que le signal de sélection vaille 0 ou 1, le circuit effectue, respectivement, une addition ou une soustraction.

### Additionneurs standards

Plusieurs études [35, 47, 55, 108] ont confirmé le fait que sur FPGA, il convenait d'effectuer l'addition de manière standard, en utilisant des structures à propagation de retenue plutôt que des additionneurs redondants à retenue conservée (*carry-save adders*) (Fig. 2.1). D'autre part, il ressort de ces études, qu'étant donné que le routage a une influence significative sur le coût de l'addition, il y a une différence notable dans la méthode appropriée pour pipeliner des additionneurs pour ASIC que pour FPGA.

Pour la conception d'ASIC, afin de subdiviser un additionneur en segments plus courts, les bascules de pipeline devraient être insérés à l'intérieur de l'additionneur à des

FIG. 2.1 – Additionneur à retenue propagée standard

intervalles réguliers de cellules logiques.

Sur FPGA, cette technique n'est utile que pour réduire le délai des additionneurs larges. Autrement, les bascules ne devraient être insérées qu'à des intervalles réguliers entre les additionneurs. Cette méthode a, de plus, l'avantage d'utiliser les bascules présentes à l'intérieur des cellules logiques déjà allouées à un additionneur sans augmenter sa taille ou sa complexité.

### Additionneurs larges

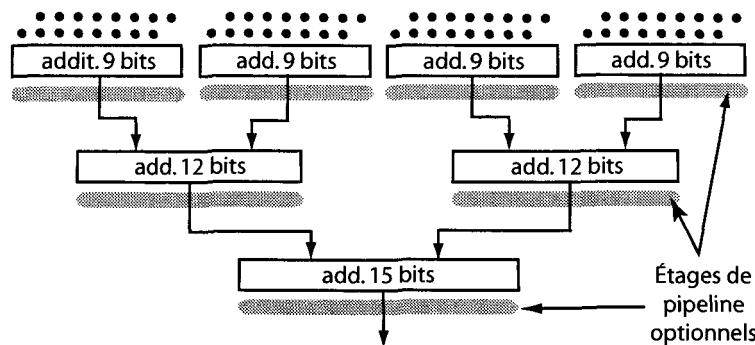

Pour des additionneurs larges, Jamro et Wiatr [47] ont proposé une solution hybride qui consiste à la fois à diviser les additionneurs larges en de plus petits segments, comme dans la méthode ASIC, et d'insérer des bascules de pipeline à des intervalles réguliers entre additionneurs (Fig. 2.2). Ils ont suggéré que cette solution apparaissait meilleure que la technique d'addition retardée introduite par Luo et Martonosi en 1998 [62], qui utilise des arbres de Wallace pour accumuler des valeurs sans effectuer une propagation de retenue complète.

Pour des applications demandant une plus grande vitesse, telles que la cryptographie, une méthode alternative rapide pour la réalisation d'additionneurs larges sur FPGA de la famille Virtex a été présentée dans un article en 2002 par Perri et al. [78]. Cette méthode est aussi utile pour les FPGA des familles XC4000X, Spartan et Spartan-

FIG. 2.2 – Pipelinage des additionneurs

XL. Les auteurs ont utilisé des éléments logiques de contournement pour éliminer les délais de routage difficiles du chemin critique. Pour un additionneur 128 bits réalisé par cette méthode, les auteurs rapportent un gain de performance allant jusqu'à 47 % comparativement à un additionneur à propagation de retenue conventionnel, avec un surcoût en espace de 28 %.

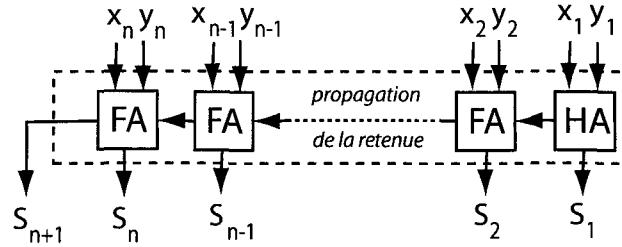

### Additionneurs et soustracteurs bit-séries

L'addition sérielle de deux nombres est particulièrement simple. À mesure que chaque paire d'opérandes est reçue, il suffit de calculer un chiffre de somme et un chiffre de retenue, puis le chiffre de retenue est additionné avec la prochaine paire d'opérandes, et ainsi de suite. La réalisation d'un tel additionneur ne requiert rien de plus qu'un additionneur complet et une bascule (Fig. 2.3).

FIG. 2.3 – Additionneur et soustracteur bit-séries

Le principal intérêt de l'utilisation d'un additionneur bit-sériel est qu'il peut fonctionner à très haute fréquence et que sa taille, d'environ deux cellules logiques sur FPGA, ne varie pas en fonction de la longueur des opérandes.

### 2.3.2 Multiplieurs

La multiplication est l'une des opérations les plus complexes et les plus critiques ayant à être réalisées sur FPGA. Comparativement aux ASIC, les FPGA présentent l'avantage d'être reconfigurables, mais, pour plusieurs types de multiplieurs, ils sont beaucoup plus lents que des puces ITGE conçues sur mesure. Une spécialisation et une concurrence accrues sont donc nécessaires pour obtenir un quelconque gain de performance par rapport aux processeurs de signaux numériques (DSP) et aux ASICs [79]. Il existe cinq principales structures de multiplieurs :

*Décalage et addition* — Un opérande est décalé à gauche d'un bit par cycle et est appliqué à un additionneur lorsque le bit correspondant du second opérande est haut. Cette technique donne des mises en œuvre compactes, mais très lentes, nécessitant  $N$  cycles d'horloge pour se compléter, et ne permet pas le chevauchement des calculs.

*Arbre logique* — Chacun des bits résultants sont une fonction logique des bits associés de chaque opérande. Cela donne une grande structure à entrance élevée, envisageable jusqu'à 32 bits (Fig. 2.4).

FIG. 2.4 – Multiplieur 8 bits sous forme d’arbre d’additionneurs à propagation de retenues

*Structures en tableaux* – Des tableaux parallèles donnent des multiplieurs rapides, avec une délai minimum, mais donne des mises en œuvre coûteuses, une majeure partie de la logique étant inactive au cours d’un calcul.

*Tables de conversion* – Les opérandes sont appliqués comme adresses à une mémoire pré-programmée qui donne le résultat en sortie. Cette technique est l’une des plus rapides, mais son coût en espace est si élevé qu’elle est impraticable pour des multiplieurs plus grands que  $4 \times 4$ . Par exemple, une mise en œuvre  $16 \times 16$  nécessiterait une mémoire de  $2^{16} \times 2^{16} \times 32$  bits = 4 G × 32 bits. On peut, notamment, utiliser les blocs multiplieurs ITGE incorporés dans plusieurs FPGA récents. Lorsqu’ils sont disponibles, leur utilisation est parmi les manières les plus rapides d’effectuer des multiplications sur FPGA, et, de plus, elle n’utilise que peu d’éléments logiques.

### Multiplieurs à base de tables

Les premiers multiplieurs entiers à base de tables pour FPGA, rapides et relativement compacts, ont été introduits en 1993–94 par l’ingénieur de Xilinx K. Chapman, pour l’architecture XC4000 [28, 29]. La solution idéale proposée dans cette contribution était de nature hybride, et consistait à utiliser de petites tables de valeurs pour les produits

partiels et à combiner les résultats par addition. L'idée de base était de subdiviser le premier opérande en sections, à multiplier par consultation de table chacune des sections avec le second opérande au complet et d'utiliser un arbre d'additionneurs pour additionner les produits partiels.

Les multiplieurs à base de tables ont, par la suite, été étudiés dans plusieurs autres travaux, dont [48, 53, 70, 81, 98]. Il convient notamment de souligner la contribution de Miomo et al. [70] qui ont présenté, dans FPL 2000, un multiplieur très rapide, mais aussi de taille considérable, pour FPGA munis de LUT à 4 entrées. Ce concept utilise une méthode de compaction basée sur une représentation numérique redondante. Les auteurs en ont comparé une mise en œuvre 16 bits, avec compaction sur 4 bits, avec le plus récent multiplieur 16 bits fourni par Xilinx à l'époque et ont rapporté un gain en vitesse de trois fois celle obtenue par Xilinx, moyennant un accroissement par cinq de la surface du circuit.

### **Multiplieurs à coefficient constant**

Les multiplieurs à coefficient constant sont économiques sur FPGA, à la fois en espace et en temps. La multiplication par une constante se présente dans un grand nombre d'applications, incluant les fonctions d'amplification, les contrôleurs numérique, la conversion d'espaces de couleurs et le filtrage numérique. Un multiplieur à coefficient constant n'utilise généralement qu'un quart à un tiers de la taille d'un multiplieur optimisé pour l'espace et est au moins aussi rapide qu'un multiplieur optimisé pour la vitesse.

Le concept consistant à utiliser une structure spéciale pour la multiplication par une constante sur FPGA a été introduite pour la première fois chez Xilinx, en 1996, par K. Chapman [30] et des collègues [50].

Sur FPGA à base de LUTs, les mises en œuvre de multiplieurs à coefficient constant

FIG. 2.5 – Un multiplicateur 8 bits par une constante

bénéficient du fait que les LUTs peuvent être utilisées comme des mémoires à lecture seule. Une LUT à 4 entrées, par exemple, peut être utilisée comme une ROM  $16 \times 1$ . Steve Knapp (1998) a adapté cette approche pour maximiser l'utilisation des LUTs à 4 entrées en travaillant en hexadécimal (base 16) et en utilisant un arbre d'additionneurs pour des entrées plus larges [52].

Une méthode pour réduire le temps de conception de multiplieurs-additionneurs rapides à coefficient constant pour le traitement de signaux numériques a été décrite dans [53].

En 2002, Wiatr et Jamro ont présenté une étude comparative de deux techniques de multiplication à coefficient constant [48] : la multiplication sans multiplieur (à décalage addition/soustraction) (SM) utilisant une représentation numérique à chiffres signés canonique (CSC) et la multiplication à base de LUTs par table de conversion (ML). Cette étude a aussi introduit un nouvel algorithme pour la conversion de nombres en complément à deux en représentation CSC. Une représentation CSC contient approximativement 33 % moins de bits différents de zéro que sa contrepartie binaire, se traduisant par des gains du même pourcentage par coefficient. ML, en théorie, donne les mises en œuvre les plus rapides, étant donné qu'aucune arithmétique proprement dite n'est requise, mais la taille des tables de conversion croît rapidement à de grandes

dimensions avec la largeur des opérandes. En conséquence, les auteurs arrivent à la conclusion que ML est habituellement la structure la plus efficace lorsque la largeur des opérandes et des coefficients est petite (moins de 5) et que, dans tous les autres cas, SM est généralement plus économique. En 2001–2002, Jamro and Wiatr ont étendu leur étude à des structures de multiplicateurs à coefficient constant visant la réalisation de la convolution sur FPGA [46, 48].

### **Arithmétique distribuée**

L'*Arithmétique distribuée* (DA) a traditionnellement joué un rôle clé dans les systèmes de traitement de signaux numériques à base de FPGA, car elle fournit une méthode de conception à base de LUT sans multiplicateur, appelée DALUT. L'approche DA est spécifiquement destinée au calcul de la somme des produits (que l'on appelle aussi le produit point vectoriel) que l'on retrouve dans plusieurs fonctions de filtrage et de transformation [43]. L. Mintzer a été le pionnier de l'arithmétique distribuée sur FPGA. En 1992, il a montré que, combiné avec l'architecture à base de LUT Xilinx, l'algorithme DA produisait des concepts de filtres très efficaces [68].

En l'an 2000, avec l'avènement de la radio et des MODEM définis par logiciel sur FPGA, Mintzer a remarqué que, hormis avec l'approche DA, même le plus rapide multiplicateur réalisé sous forme de tableau configuré dans un FPGA n'arrivait pas à égaler le coût et la performance d'un processeur DSP peu coûteux [69]. Avec l'apparition récente de multiplicateurs matériels, de structures multiplicateur–accumulateur (MAC) dans des blocs DSP et de *RocketIOs™* ayant un débit de gigabits par seconde, intégrés à la fabrication, les FPGA modernes sont maintenant beaucoup plus performants que les autres dispositifs.

## Pipelining des multiplicateurs

Lorsque l'on utilise un outil de synthèse supportant le pipelinage, il est possible de décrire le pipelinage d'un multiplicateur de manière comportementale en faisant suivre sa description par autant de registres que le nombre de niveaux de pipeline désirés. L'outil de synthèse peut ainsi équilibrer le multiplicateur en utilisant les registres afin d'améliorer la fréquence d'horloge. Le code VHDL suivant demande 2 niveaux de pipeline.

```

process (CLK)

begin

if (CLK'event and CLK='1') then

Reg1 <= A * B;

Reg2 <= Reg1;

end if;

end process;

```

Plusieurs techniques de pipelinage de multiplicateurs pour FPGA ont été proposées [44, 57, 99]. Certains auteurs [50, 100] ont même eu recours à la reconfiguration dynamique pour mettre à jour le contenu des LUT afin de définir une nouvelle valeur de multiplicande.

Dans FPL'99, une étude, soumise par M. Wojko, a comparé, sur des FPGA Xilinx® XC4036EX-2 et Altera EPF10K70RC-2, la performance en pipeline de trois techniques de multiplication : par tableau parallèle, par addition parallèle à base de vecteurs, et de type Wallace à retenue conservée, et a décrit deux techniques de multiplication alternatives pour FPGA, utilisant une approche hybride à retenue conservée/propagée [99].

Dans une étude plus récente, Panato et al. [76] ont envisagé l'usage de pipelines très profonds pour les mises en œuvre sur FPGA, chaque étage de pipeline étant limité à une seul élément logique, et ont réalisé un multiplicateur-tableau en utilisant cette technique.

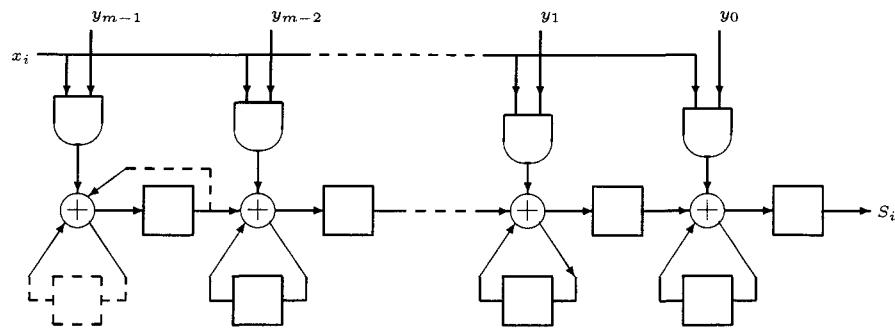

### 2.3.3 Multiplieurs bit-séries

Des modules de multiplication bit-séries ont fait l'objet de recherches approfondies dans la littérature de l'ITGE, en particulier pour le traitement de signal haute fréquence. Pour des applications, telles que le traitement d'images en temps réel et les opérations matricielles, où le plus grand nombre possible de multiplieurs doivent calculer en parallèle (calcul massivement parallèle), une « règle du pouce » suggère que le coût en cellules logiques d'un multiplieur ne devrait pas excéder cinq fois la longueur de ses opérandes.

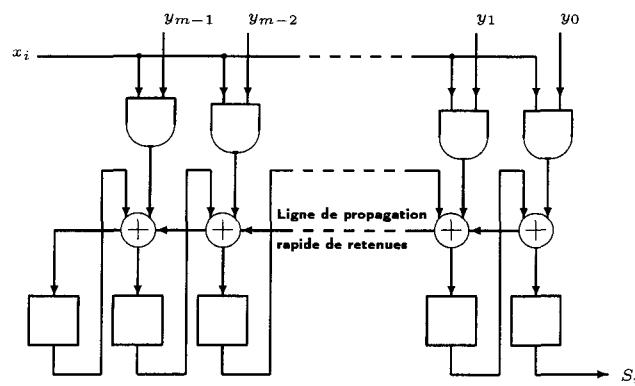

FIG. 2.6 – Multiplieur parallèle-série RCAD conventionnel

FIG. 2.7 – Multiplieur parallèle-série RPAD exploitant les lignes de propagation de retenues dédiées

La mise en œuvre la plus classique des multiplieurs sériels conventionnels (bit de

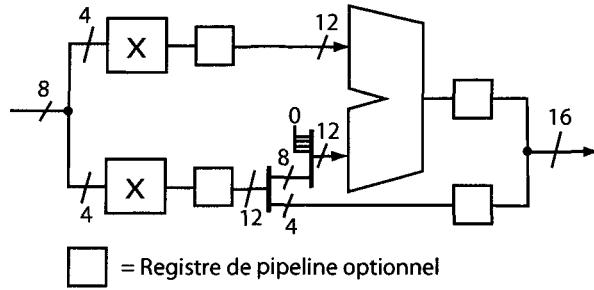

poids faible en tête), est la multiplication *série-parallèle* (Fig. 2.6 et 2.7), qui, comme son nom l'indique, accepte un opérande en série, l'autre en parallèle, et produit un résultat sériel. Ces multiplieurs ne sont basés que sur des additions et des décalages, et on en distingue deux variantes principales, selon que la retenue soit conservée (retenue conservée-addition-décalage – RCAD) (Fig. 2.6) ou propagée (retenue propagée-addition-décalage – RPAD) (Fig. 2.7) [9]. Comme il ne propage pas la retenue, un multiplieur RCAD peut fonctionner à très haute fréquence. Un multiplieur RPAD est beaucoup plus lent, mais, grâce à son exploitation des lignes de propagation de retenues dédiées, occupe deux fois moins d'espace qu'un multiplieur RCAD sur FPGA.

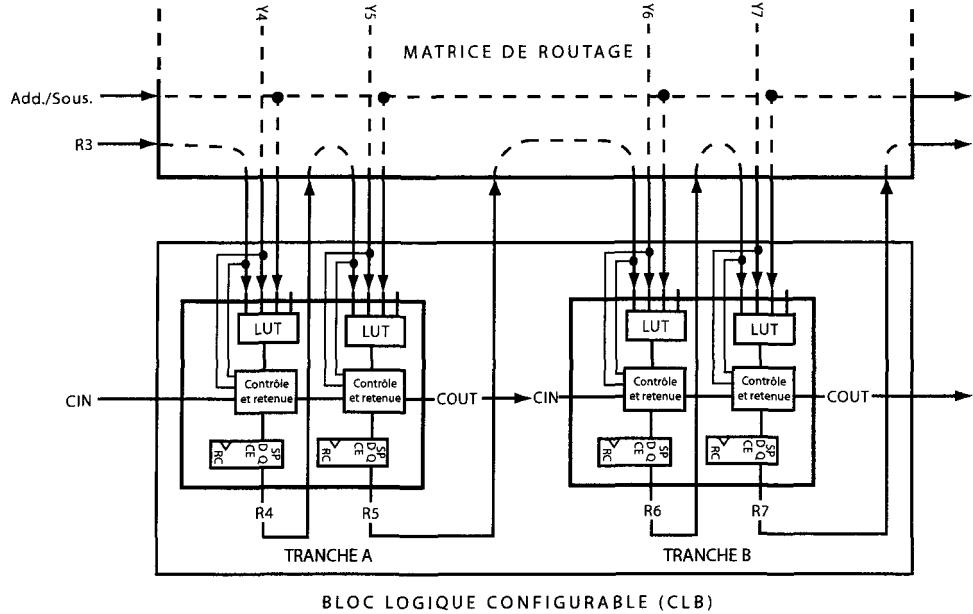

Hormis l'usage de multiplieurs ITGE embarqués ou de petits multiplieurs à base de table, la multiplication série-parallèle demeure la mise en œuvre la plus simple, la plus efficace, la moins coûteuse et la plus employée, autant pour FPGA que pour ASIC. Sur FPGA, elle peut être mise en correspondance directe avec l'architecture des tranches.

Valls et al. ont présenté, en 1998, une étude systématique de multiplieurs série-parallèles pour la réalisation de filtres numériques sur FPGA [95]. L'année suivante, cette étude a été enrichie d'autres multiplieurs série-parallèles chiffre-à-chiffre pipelinés, rapides et économiques [96]. En 2003, l'étude a été complétée par des résultats de réalisations optimisées pour FPGA à tables de vérité de 4 entrées, mais pouvant aussi se généraliser à d'autres tailles d'entrées [94]. Un guide de conception de plusieurs différents types de structures de multiplieurs série-parallèles, pour le traitement de signaux numériques, a été publié, en l'an 2000, par Ashour et Saleh [9].

Un concept de multiplieur reconfigurable, nommé DigiFAB, introduit en 2001 par Visavakul et al. [97], combine un type de multiplieur-tableau appelé Flexible Array Blocks (FABs) avec des techniques numériques pour produire des multiplieurs de taille arbitraire avec des ressources limitées.

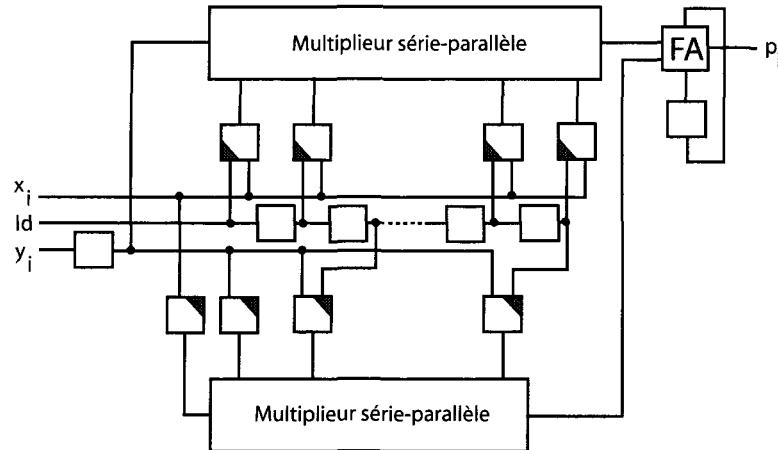

FIG. 2.8 – Un multiplieur série-série construit à partir de deux multiplieurs série-parallèle

FIG. 2.9 – Un multiplieur série-série utilisant un compteur parallèle

Les travaux consacrés à la réalisation de multiplieurs sériels conventionnels acceptant les deux opérandes en série sont plutôt rares, encore davantage pour FPGA. On peut en trouver des exemples dans [45] et [26] (Fig. 2.8 et 2.9).

Ces multiplieurs sont généralement plus lents que des multiplieurs série-parallèles, et leur mise en œuvre s'avère aussi plus coûteuse. Il est d'ailleurs possible d'adapter ces derniers au moyen d'un convertisseur série-parallèle pour l'opérande parallèle, et d'un

délai de durée appropriée pour l'opérande sériel. On peut utiliser l'architecture de la Fig. 2.8 pour doubler le débit.

FIG. 2.10 – Opérateur bit-sériel d'élévation au carré

La Fig. 2.10 présente une architecture similaire pour l'élévation au carré bit-sérielles.

### **Multiplieurs bit-séries constants**

Les multiplieurs bit-séries avec un opérande constant sont particulièrement utilisés dans les applications de traitement numérique du signal et le traitement vidéo, notamment pour la mise en œuvre en temps réel de la convolution pour le filtrage et des transformations telles que la FFT et la DCT.

De tels multiplieurs se construisent directement à partir d'un multiplicateur série-parallèle, en maintenant l'opérande parallèle constant. Le circuit peut être simplifié là où la constante comporte des zéros. Par ailleurs, une structure de multiplication constante offrant un compromis espace-temps optimal a été décrit par Dittmann et al. en 2003 [34].

### 2.3.4 Additionneurs et multiplieurs modulaires

L'arithmétique modulaire joue un rôle crucial dans les applications de traitement de signal qui profitent de l'arithmétique en système RNS et dans divers algorithmes cryptographiques à clé publique, tels que RSA, où le principal calcul est la modulation exponentielle  $c = m \bmod n$ .

FIG. 2.11 – Quelques additionneurs et multiplieurs modulaires

J.-L. Beuchat a été parmi les premiers à contribuer à l'addition et à la multiplication modulaire sur FPGA [20]. Avec J.-M. Muller, il a proposé une famille d'algorithmes en base 2 conçus pour les FPGA à LUT à 4 entrées et à lignes de propagation de retenues dédiées [21]. Quelques additionneurs et multiplieurs modulaires découlant des travaux de Beuchat et Muller sont montrés à la Fig. 2.11. Ces multiplieurs sont efficaces pour des moduli allant jusqu'à 32 bits.

Pour les grands opérandes, les additionneurs à retenue conservée sont cependant

beaucoup plus rapides [14]. On trouve aussi dans [7] une étude d'architectures matérielles efficaces pour la mise en œuvre de la multiplication modulaire sur FPGA.

### **Multiplieurs modulaires bit-séries**

Une architecture de multiplication modulaire haute-vitesse basée sur l'algorithme de multiplication de Montgomery a été présentée par W. P. Marnane, en 1998 [63].

#### **2.3.5 Opérateurs arithmétiques à base de petits blocs multiplieurs**

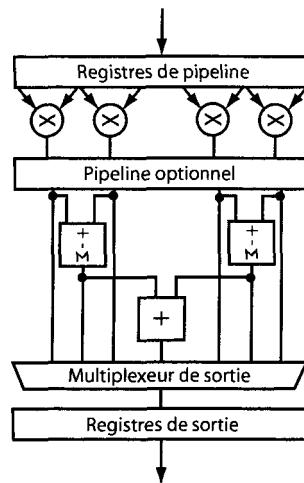

Plusieurs FPGA apparus sur le marché récemment contiennent de petits multiplieurs ITGE ultra-rapides incorporés, et comportant également d'autres caractéristiques architecturales dédiées à la réalisation de multiplieurs haute-performance (Fig. 2.12). Dans cette catégorie, on compte (en ordre alphabétique par nom de fabriquant) les : Cyclone<sup>TM</sup> II, Stratix®, Stratix GX et Stratix II d'Altera, [2,4–6] ; Spartan<sup>TM</sup>-3, Virtex-II, Virtex-II Pro, Pro X et Virtex-4 de Xilinx [104–107].

FIG. 2.12 – Multiplieur 18x18 embarqué

Altera et Xilinx ont publié des documents *application note* sur la mise en œuvre de multiplieurs haute performance dans ces FPGA [3, 102].

Certains des FPGA Altera intègrent des multiplieurs-accumulateurs (MACs) dans des blocs DSP, pouvant fonctionner à des débits de données supérieurs à 300 millions d'échantillons par seconde (MEPS) (Fig. 2.13). Chez Xilinx, les Virtex-4 contiennent des tranches XtremeDSP<sup>TM</sup>, incluant un multiplieur 18x18, des étages de pipeline optionnels et un accumulateur et additionneur/soustracteur intégrés. Les blocs de mémoire

FIG. 2.13 – Bloc DSP d'un FPGA Stratix d'Altera

TriMatrix™ d'Altera et les blocs RAM de Xilinx peuvent être utilisés comme des tables pour réaliser, notamment, des multiplicateurs haute-performance à largeur/profondeur variable pour des applications de traitement de signaux numériques à gros volume et à faible coût. Un exemple de multiplicateur de 36 bits réalisé au moyen de multiplicateurs 18x18 embarqués est montré à la Fig. 2.14.

FIG. 2.14 – Multiplieur de 36 bits réalisé au moyen de multiplicateurs 18x18 embarqués

Pour tirer profit des multiplicateurs intégrés, Beuchat et Tisserand ont présenté, en 2002, quelques opérateurs de multiplication et de division, en divers compromis espace-temps, basés sur les blocs multiplicateurs  $18 \times 18$  disponibles dans la famille Virtex-II de

Xilinx® (mais généralisables à n'importe quel FPGA comportant de tels blocs) [24]. Les opérateurs présentés conduisent à des améliorations de vitesse allant jusqu'à 18 % pour la multiplication et 40 % pour la division. Ces résultats ont encore été améliorés par une contribution similaire présentée l'année suivante par Lee et Burgess [56]. Cette nouvelle contribution couvre, de plus, l'élévation au carré et la division fractionnaire, tout en réalisant une économie d'espace de 20 % et une réduction du délai de 30 % dans le cas de la multiplication. Une économie d'espace pouvant aller jusqu'à 50 % peut ainsi être obtenue dans le cas de la division.

### 2.3.6 Diviseurs et extracteurs de racine carrée

Les algorithmes restaurant et non restaurant sont les méthodes de base de division et d'extraction de la racine carrée par récurrence. Elles produisent un nombre fixe de bits par itération. La division non restaurante conserve toujours la différence dans le registre du reste partiel, alors que la division restaurante utilise une étape de supplémentaire pour restaurer conditionnellement le reste partiel à sa valeur précédente dans le cas où la différence est négative. L'algorithme SRT est une modification de l'algorithme non restaurant permettant de calculer en grande base dans un but d'accélération.

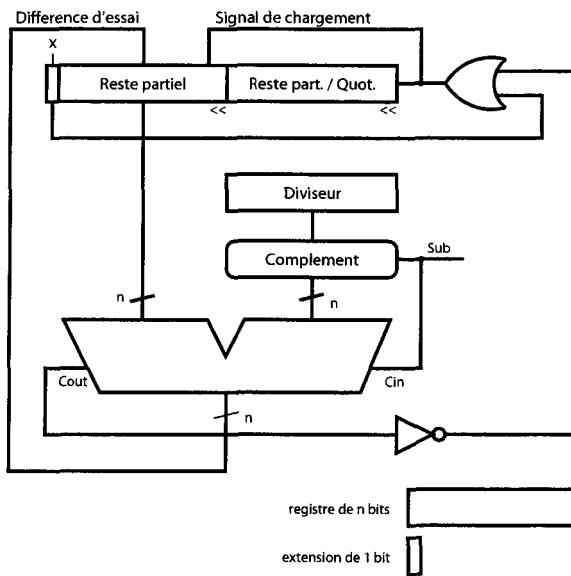

FIG. 2.15 – Diviseur séquentiel restaurant

FIG. 2.16 – Diviseur séquentiel non restaurant

La Fig. 2.15 montre un diviseur restaurant séquentiel, et la Fig. 2.16, un diviseur non restaurant séquentiel. On peut obtenir un diviseur pseudo-combinatoire ou un diviseur pipeliné en déroulant l'itération de base, mais la division demeure toujours un processus fondamentalement itératif, où chaque étape d'itération ne produit qu'un seul chiffre du

résultat. Il n'existe pas de réseau combinatoire pour la division tel qu'il en existe pour l'addition et la multiplication.

La division non-restorative en base  $2^n$  d'opérandes signés s'énonce comme suit :

$$\begin{array}{lll} x & \text{Dividende} & x_0x_1 \cdots x_{nm-n-1}x_{nm-n} \cdots x_{nm-2}x_{nm-1} \\ d & \text{Diviseur} & d_0d_1 \cdots d_{nm-n-1}d_{nm-n} \cdots d_{nm-2}d_{nm-1} \\ q & \text{Quotient} & q_0q_1 \cdots q_{nm-n-1}q_{nm-n} \cdots q_{nm-2}q_{nm-1} \\ w & \text{Reste} & w_0w_1 \cdots w_{nm-n-1}w_{nm-n} \cdots w_{nm-2}w_{nm-1} \end{array}$$

où  $q = x/d$ ,  $w = x - (d \times q)$ , sachant que  $x$  et  $d$  sont tous deux de  $m$  chiffres, où chaque chiffre comporte  $n$  bits, et  $x_0$  et  $d_0$  sont les chiffres de signe de  $x$  et  $d$ , respectivement, comportant chacun  $n$  bits. L'expression  $x - (d \times q)$  décrivant le reste  $w$  découle de l'équation de base de division  $x = (d \times q) + w$ . Cette équation, conjointement à la condition  $w < d$ , définit complètement la division entière. Le problème de la division binaire se réduit à soustraire du dividende  $x$  un ensemble de nombres, chacun étant soit 0 ou une version décalée du  $d$ .

$$Y = \begin{cases} 0 & \text{si positif} \\ 2^n - 1 & \text{si négatif} \end{cases}$$

Le quotient est obtenu en ajoutant un nombre de zéros à la suite du dividende  $z$ . La décision d'effectuer soit une addition, soit une soustraction à chaque étape de l'algorithme 1 est basée sur le chiffre de signe du reste partiel courant  $w_{m-1}$  ou sur le dividende,  $x_{m-1}$ .

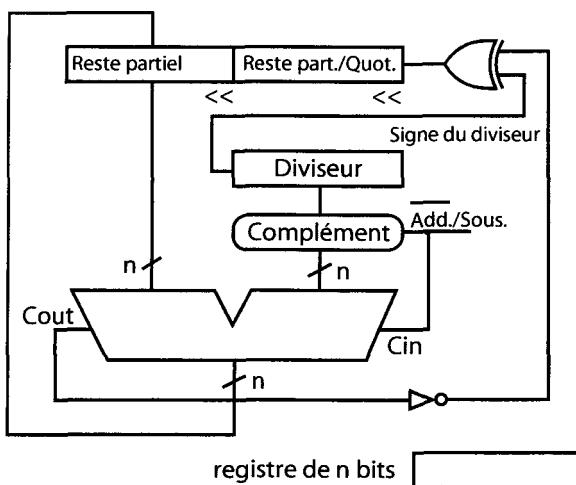

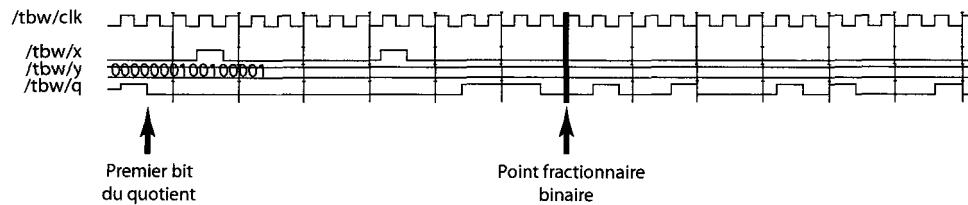

**Exemple 1** Une simulation avec les entrées :  $n = 16$ ,  $d = 289$  and  $x = 4128$  donnant pour résultat :  $q = (0000000000001110.010001010001\ldots)_2 = (14.283721923828125)_{10}$  est montrée à la figure 2.17.

FIG. 2.17 – Chronogramme de l'exemple 1

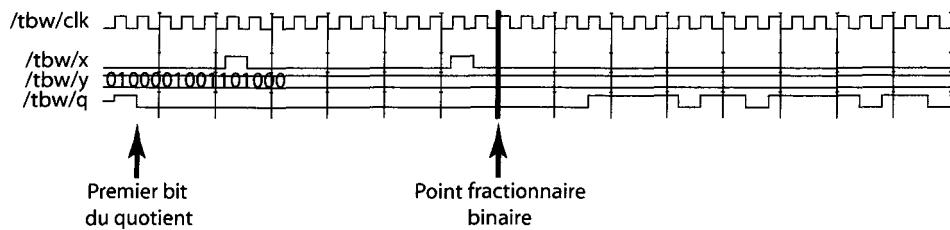

**Exemple 2** Une simulation avec les entrées :  $n = 16$ ,  $d = 17000$  et  $x = 1025$  donnant pour résultat :  $q = (0000000000001110.010001010001\dots)_2 = (14.283721923828125)_{10}$  est montrée à la figure 2.18.