# CONCEPTION D'UN CONVERTISSEUR ANALOGIQUE-NUMÉRIQUE À HAUTE PRÉCISION ET BASSE CONSOMMATION DE PUISSANCE AVEC LA TECHNOLOGIE CMOS 65 NM

### PAR ANTOINE VERREAULT

# MÉMOIRE PRÉSENTÉ À L'UNIVERSITÉ DU QUÉBEC À CHICOUTIMI EN VUE DE L'OBTENTION DU GRADE DE MAÎTRISE ÈS SCIENCES APPLIQUÉES (M. SC. A.) EN INGÉNIERIE

Jury:

Prof. Alexandre Robichaud, UQAC, directeur de recherche

Prof. Paul-Vahé Cicek, UQAM, codirecteur de recherche

Prof. Zakaria El Alaoui Ismaili, UQAM, examinateur externe

Prof. Dilip Sarkar, UQAC, président du jury

**QUÉBEC, CANADA**

© ANTOINE VERREAULT, 2025

### **RÉSUMÉ**

Ce mémoire propose une nouvelle architecture d'ADC  $\Delta\Sigma$  conçue pour répondre à des exigences strictes en matière de rapport signal sur bruit (SNR) sur une bande passante de plusieurs centaines de kilohertz. L'architecture repose sur la topologie sturdy MASH, dans laquelle le second étage est remplacé par un SAR à filtrage de bruit (NS-SAR). Grâce à la propriété de feedforward intrinsèque au NS-SAR, cette nouvelle topologie permet d'annuler efficacement le bruit de quantification du premier étage.

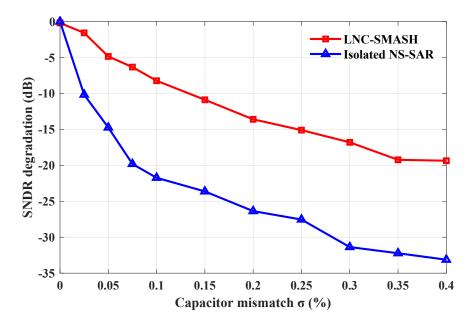

Le NS-SAR bénéficie aussi de contraintes de conception grandement simplifiées grâce à une amplitude d'entrée réduite et grâce au filtrage additionnel fourni par le premier étage, ce qui atténue les non-idéalités du circuit. Ces caractéristiques permettent une implémentation du NS-SAR à très faible consommation de puissance.

Au niveau circuit, un amplificateur dynamique innovant est proposé pour optimiser le compromis entre la consommation de puissance, l'encombrement et la capacité d'attaquer de grandes charges dans le premier intégrateur du circuit. D'autres techniques de conception contribuent également à maximiser l'efficacité du circuit comme l'utilisation d'un sommateur passif réutilisant les condensateurs du DAC du quantificateur SAR, éliminant ainsi le besoin d'un amplificateur dédié.

L'ADC a été implémenté avec la technologie CMOS 65 nm sur Cadence Virtuoso. Les résultats de simulations démontrent d'excellentes performances comparables à l'état de l'art des ADC à suréchantillonnage. Les spécifications atteintes sont un ratio signal sur bruit et distorsion de 90.3 dB, une bande passante de 500 kHz et une consommation de puissance de 1.633 mW, ce qui correspond à une  $FOM_{SC}$  de 175.2 dB.

# TABLE DES MATIÈRES

| RÉSUMÉ i                                                                                            |

|-----------------------------------------------------------------------------------------------------|

| LISTE DES TABLEAUX                                                                                  |

| LISTE DES FIGURES                                                                                   |

| LISTE DES ABRÉVIATIONS                                                                              |

| REMERCIEMENTS                                                                                       |

| AVANT-PROPOS                                                                                        |

| INTRODUCTION                                                                                        |

| CHAPITRE I - OVERSAMPLING ADC : A REVIEW OF RECENT DESIGN                                           |

| TRENDS                                                                                              |

| 1.1 RÉSUMÉ EN FRANÇAIS                                                                              |

| 1.2 ABSTRACT                                                                                        |

| 1.3 INTRODUCTION                                                                                    |

| 1.4 METHODOLOGY                                                                                     |

| 1.5 OVERVIEW OF OVERSAMPLING ADC STRATEGIES                                                         |

| 1.5.1 THE DISCRETE-TIME $\Delta\Sigma$ MODULATOR                                                    |

| 1.5.2 THE CONTINUOUS-TIME $\Delta\Sigma$ MODULATOR                                                  |

| 1.5.3 THE INCREMENTAL $\Delta\Sigma$ MODULATOR                                                      |

| 1.5.4 THE NOISE-SHAPING SAR TOPOLOGY                                                                |

| 1.5.5 THE ZOOM TOPOLOGY                                                                             |

| 1.5.6 THE TIME-DOMAIN $\Delta\Sigma$ MODULATOR                                                      |

| 1.6 STATUS OF THE STATE OF THE ART                                                                  |

| 1.6.1 COMPARISON WITH OLDER DESIGNS AND NYQUIST ADC 22                                              |

| 1.6.2 SELECTED OVERSAMPLING ADC                                                                     |

| 1.7 SYSTEM-LEVEL DESIGN TRENDS                                                                      |

| 1.7.1 DESIGN TRENDS IN THE CONVENTIONAL DISCRETE-TIME AND CONTINUOUS-TIME $\Delta\Sigma$ TOPOLOGIES |

| 1.7.2   | DESIGN TRENDS IN THE INCREMENTAL $\Delta\Sigma$ MODULATOR                             | 34 |

|---------|---------------------------------------------------------------------------------------|----|

| 1.7.3   | DESIGN TRENDS IN THE NOISE-SHAPING SAR TOPOLOGY                                       | 36 |

| 1.7.4   | DESIGN TRENDS IN THE ZOOM TOPOLOGY                                                    | 39 |

| 1.7.5   | DESIGN TRENDS IN THE TIME-DOMAIN $\Delta\Sigma$ MODULATOR $\ .\ .\ .\ .$              | 43 |

| 1.8 CIR | CUIT-LEVEL DESIGN TRENDS                                                              | 47 |

| 1.8.1   | AMPLIFIER AND LOOP FILTER DESIGN TRENDS                                               | 47 |

| 1.8.2   | NOISE MITIGATION TRENDS                                                               | 53 |

| 1.8.3   | DAC MISMATCH COMPENSATION DESIGN TRENDS                                               | 56 |

| 1.8.4   | INPUT SWING OPTIMISATION DESIGN TRENDS                                                | 60 |

| 1.8.5   | SILICON AREA MINIMISATION DESIGN TRENDS                                               | 63 |

| 1.8.6   | PROCESS SCALING MITIGATION DESIGN TRENDS                                              | 66 |

| 1.9 DIS | CUSSION                                                                               | 68 |

| 1.10 CO | NCLUSION                                                                              | 74 |

|         | E II – A LEAN NOISE-CANCELLING STURDY MASH DELTA-<br>C WITH A NOISE-SHAPING SAR STAGE | 76 |

|         | SUMÉ EN FRANÇAIS                                                                      |    |

|         | STRACT                                                                                |    |

|         |                                                                                       |    |

|         | RODUCTION                                                                             |    |

| 2.4 SYS | STEM OVERVIEW                                                                         | 79 |

| 2.4.1   | LIMITATIONS OF THE SMASH ARCHITECTURE                                                 | 79 |

| 2.4.2   | SYSTEM-LEVEL IMPLEMENTATION                                                           | 81 |

| 2.4.3   | PROOF-OF-CONCEPT DESIGN                                                               | 83 |

| 2.5 SIM | IULATION RESULTS                                                                      | 84 |

| 2.5.1   | SIMULATION OF IDEAL OUTPUT SQNR                                                       | 84 |

| 2.5.2   | SIMULATION OF MISMATCH EFFECT ON SNDR                                                 | 86 |

| 2.6 CO  | NCLUSION                                                                              | 88 |

| _          | III – A RAIL-TO-RAIL LOW-POWER DYNAMIC CMOS AM-<br>R SWITCHED-CAPACITOR FILTERS IN HIGH-PERFORMANCE |

|------------|-----------------------------------------------------------------------------------------------------|

| <b>ADC</b> |                                                                                                     |

| 3.1 RÉSU   | JMÉ EN FRANÇAIS                                                                                     |

| 3.2 ABST   | TRACT 90                                                                                            |

| 3.3 INTR   | ODUCTION                                                                                            |

| 3.4 PROP   | POSED AMPLIFIER TOPOLOGY                                                                            |

| 3.4.1 I    | DESIGN OVERVIEW                                                                                     |

| 3.4.2 H    | FIRST STAGE                                                                                         |

| 3.4.3 V    | VARIABLE CURRENT SOURCE                                                                             |

| 3.4.4      | OUTPUT STAGE                                                                                        |

| 3.4.5 S    | STABILITY AND SWITCHING COMPENSATION                                                                |

| 3.4.6 N    | NOISE CONSIDERATIONS                                                                                |

| 3.5 EXAM   | MPLE DESIGN IN CMOS 65 NM                                                                           |

| 3.5.1 I    | DESIGN 99                                                                                           |

|            | SIMULATION RESULTS AND COMPARISON WITH STATIC AMPLIFIER                                             |

| 3.6 CON    | CLUSION                                                                                             |

|            | IV - A 500 KHZ-BW, 90 DB-SNDR LEAN NOISE-CANCELING<br>TA-SIGMA ADC IN 65 NM CMOS                    |

| 4.1 RÉSU   | JMÉ EN FRANÇAIS                                                                                     |

| 4.2 ABST   | TRACT                                                                                               |

| 4.3 INTR   | ODUCTION                                                                                            |

| 4.4 SYST   | TEM OVERVIEW                                                                                        |

| 4.4.1 H    | HIGH-LEVEL OVERVIEW                                                                                 |

| 4.4.2      | CIRCUIT-LEVEL OVERVIEW                                                                              |

| 4.5 LOW-   | POWER RAIL-TO-RAIL DYNAMIC AMPLIFIER                                                                |

|            | DESIGN CONSTRAINTS FOR THE FIRST INTEGRATOR'S AMPLIFIER                                             |

| 4     | .5.2 PROPOSED DYNAMIC AMPLIFIER TOPOLOGY                             | 11  |

|-------|----------------------------------------------------------------------|-----|

| 4.6   | SIMULATION RESULTS                                                   | 13  |

| 4.7   | CONCLUSION                                                           | 5   |

|       | ITRE V – ROBUSTESSE AUX VARIATIONS ET COMPARAISON<br>L'ÉTAT DE L'ART | l 7 |

| 5.1   | ROBUSTESSE AUX VARIATIONS PVT                                        | 17  |

| 5.2   | COMPARAISON AVEC L'ÉTAT DE L'ART                                     | 20  |

| CONC  | LUSION                                                               | 23  |

| BIBLI | OGRAPHIE                                                             | 26  |

### LISTE DES TABLEAUX

| TABLEAU 1.1: | BEST OVERSAMPLING ADC DESIGNS RANKED ACCORDING               |    |

|--------------|--------------------------------------------------------------|----|

|              | TO VARIOUS FOM. BLUE (RED) SHADING INTENSITY IS RE-          |    |

|              | LATED TO HIGHER (LOWER) FOM <sub>Sc</sub> RANK FOR THIS SUB- |    |

|              | SET                                                          | 73 |

| TABLEAU 3.1: | COMPARISON OF THE PROPOSED DYNAMIC AMPLIFIER                 |    |

|              | WITH EQUIVALENT STATIC AMPLIFIER DESIGNS                     | 02 |

| TABLEAU 4.1: | PERFORMANCE SUMMARY AND COMPARISON WITH STATE-               |    |

|              | OF-THE-ART $\Delta\Sigma$ ADC                                | 16 |

## LISTE DES FIGURES

| FIGURE 1.1 –  | SCATTER PLOT ILLUSTRATING THE RELATIONSHIP BETWEEN SNDR AND BANDWIDTH FOR THE SELECTED OVERSAMPLING ADC AND THOSE FROM MURMANN'S DATABASE                                                        | 10 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 1.2 –  | BLOCK DIAGRAM OF THE DT $\Delta\Sigma$ ADC                                                                                                                                                       | 13 |

| FIGURE 1.3 –  | SIGNAL AND NOISE TRANSFER FUNCTION OF A TYPICAL $\Delta\Sigma$ ADC. THE SHADED REGION SHOWS THE TOTAL SHAPING OF THE QUANTIZATION NOISE FROM BOTH THE LOOP FILTER AND THE DECIMATION FILTER      | 15 |

| FIGURE 1.4 –  | SIMULATED TRANSIENT WAVEFORMS OF A 1ST-ORDER $\Delta\Sigma$ ADC WITH 9 QUANTIZER LEVELS FOR SIGNALS LABELLED IN FIG. 1.2                                                                         | 15 |

| FIGURE 1.5 –  | BLOCK DIAGRAM OF THE CT $\Delta\Sigma$ ADC                                                                                                                                                       | 16 |

| FIGURE 1.6 –  | BLOCK DIAGRAM OF THE INCREMENTAL $\Delta\Sigma$ ADC                                                                                                                                              | 18 |

| FIGURE 1.7 –  | BLOCK DIAGRAM OF THE NS-SAR ADC                                                                                                                                                                  | 19 |

| FIGURE 1.8 –  | BLOCK DIAGRAM OF THE ZOOM ADC                                                                                                                                                                    | 20 |

| FIGURE 1.9 –  | BLOCK DIAGRAM OF A TYPICAL TD $\Delta\Sigma$ ADC                                                                                                                                                 | 22 |

| FIGURE 1.10 - | SCATTER PLOT ILLUSTRATING THE TRADE-OFF BETWEEN CONVERSION EFFICIENCY AND RESOLUTION FOR THE SELECTED OVERSAMPLING ADC AND THOSE FROM MURMANN'S DATABASE.                                        | 23 |

| FIGURE 1.11 - | SCATTER PLOT SHOWCASING THE ENERGY/RESOLUTION TRADE-OFF FOR THE SELECTED ADC WITH THEIR RESPECTIVE ARCHITECTURES HIGHLIGHTED. DESIGNS WITH THE HIGHEST FIGURES OF MERIT ARE LABELLED ON THE PLOT | 25 |

| FIGURE 1.12 - | SCATTER PLOT ILLUSTRATING THE $FOM_{Sc}$ OF THE SELECTED ADC IN TERMS OF BANDWIDTH WITH THEIR RESPECTIVE ARCHITECTURES HIGHLIGHTED.                                                              | 26 |

| FIGURE 1.13 | – SCATTER PLOT INDICATING ENOB AND BANDWIDTH FOR THE TOP SIXTY SELECTED ADC ( $FOM_{Sc} > 172$ DB). THE ZONE OF OPTIMAL OPERATION FOR EACH ARCHITECTURE FAMILY IS HIGHLIGHTED | 27 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 1.14 | – BLOCK DIAGRAM OF THE MULTI-STAGE NOISE-SHAPING (MASH) AND THE STURDY MULTI-STAGE NOISE-SHAPING (SMASH) $\Delta\Sigma$ ADC ARCHITECTURES                                     | 29 |

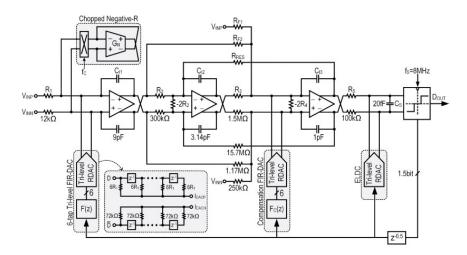

| FIGURE 1.15 | – CONTINUOUS-TIME $\Delta\Sigma$ MODULATOR WITH A NEGATIVE-R ASSISTED FIRST INTEGRATOR                                                                                        | 33 |

| FIGURE 1.16 | BLOCK DIAGRAM OF THE EXTENDED-COUNTING ADC                                                                                                                                    | 35 |

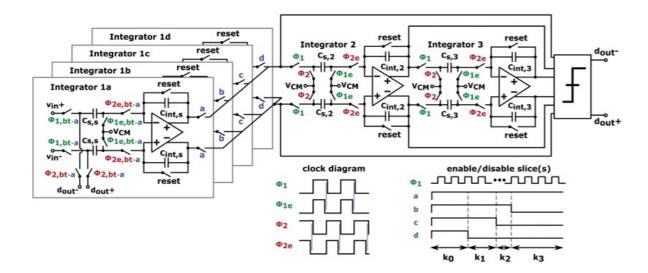

| FIGURE 1.17 | – INCREMENTAL $\Delta\Sigma$ MODULATOR IMPLEMENTING THE SLICE-BASED INTEGRATOR                                                                                                | 36 |

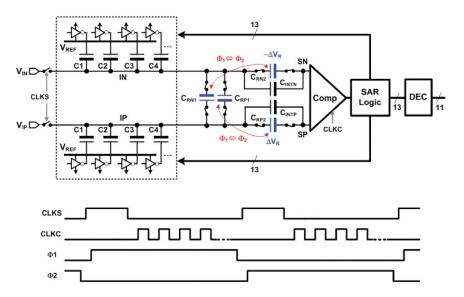

| FIGURE 1.18 | NOISE-SHAPING SAR ADC WITH THE CAPACITOR STACKING TECHNIQUE                                                                                                                   | 38 |

| FIGURE 1.19 | - DYNAMIC ZOOM ADC WITH ANALOG FEEDFORWARD PATH<br>REDUCING THE FUZZ ISSUE                                                                                                    | 41 |

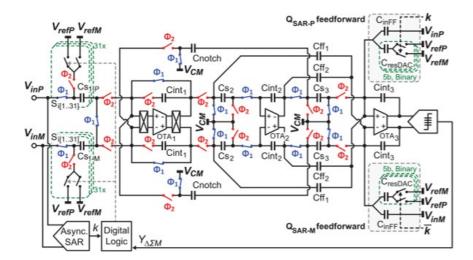

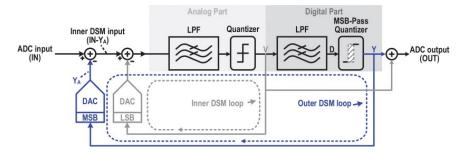

| FIGURE 1.20 | – ARCHITECTURE OF THE NESTED $\Delta\Sigma$ MODULATOR                                                                                                                         | 43 |

| FIGURE 1.21 | BLOCK DIAGRAM OF A SIMPLE IMPLEMENTATION OF THE VCO-COUNTER OVERSAMPLING ADC                                                                                                  | 43 |

| FIGURE 1.22 | – TIME-DOMAIN $\Delta\Sigma$ MODULATOR WITH VCO QUANTIZER AND $G_MC$ INTEGRATOR                                                                                               | 44 |

| FIGURE 1.23 | - ARCHITECTURE OF THE DESIGN ACHIEVING THE HIGHEST FOM                                                                                                                        | 47 |

| FIGURE 1.24 | SCHEMATIC AND TIMING DIAGRAM OF THE SOURCE FOLLOWER INTEGRATOR                                                                                                                | 50 |

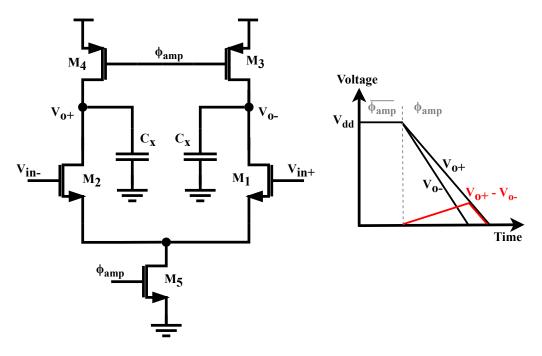

| FIGURE 1.25 | SCHEMATIC OF THE CHARGE-STEERING DYNAMIC AMPLIFIER AND ITS SIMPLIFIED OUTPUT WAVEFORMS                                                                                        | 51 |

| FIGURE 1.26 | SCHEMATIC OF THE FLOATING INVERTER DYNAMIC AMPLIFIER AND ITS SIMPLIFIED WAVEFORMS                                                                                             | 52 |

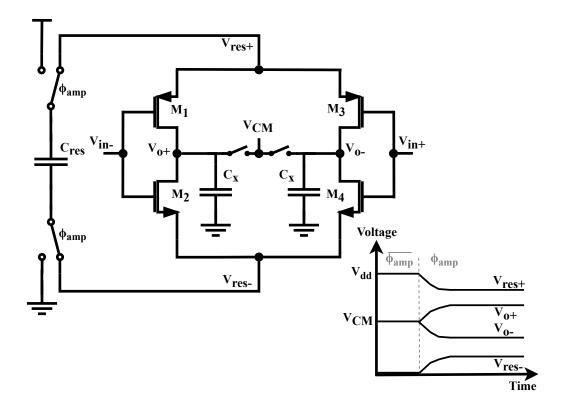

| FIGURE 1.27 | NOISE CANCELLATION CIRCUIT INSIDE A FIA-BASED LOOP FILTER WITH TIMING DIAGRAM                                                                                                 | 55 |

| FIGURE 1.28 – | TION OF THE DAC ERRORS                                                                                                                                                                            | 57 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

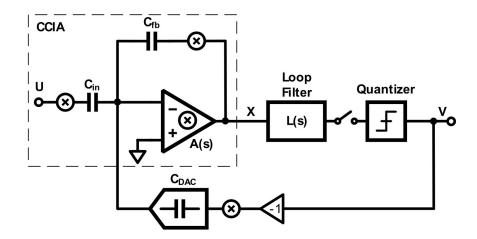

| FIGURE 1.29 - | -CAPACITIVELY COUPLED INSTRUMENTATION AMPLIFIER REDUCING THE INPUT DRIVING REQUIREMENTS OF THE CT $\Delta\Sigma$ ADC                                                                              | 62 |

| FIGURE 1.30 - | -AREA- AND POWER-EFFICIENT 3RD-ORDER DT $\Delta\Sigma$ ADC LEVERAGING PSEUDO-PSEUDO-DIFFERENTIAL AMPLIFIERS                                                                                       | 66 |

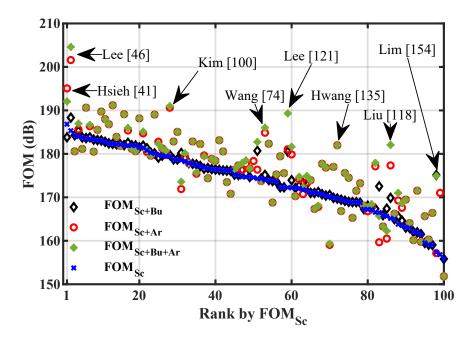

| FIGURE 1.31 – | FOUR ALTERNATE FOM WITH DIFFERENT CORRECTION FACTORS APPLIED, ORDERED BY $FOM_{Sc}$ RANK                                                                                                          | 72 |

| FIGURE 2.1 –  | DIAGRAM OF (A) THE SMASH ARCHITECTURE AND (B) THE NOVEL LNC-SMASH ARCHITECTURE                                                                                                                    | 80 |

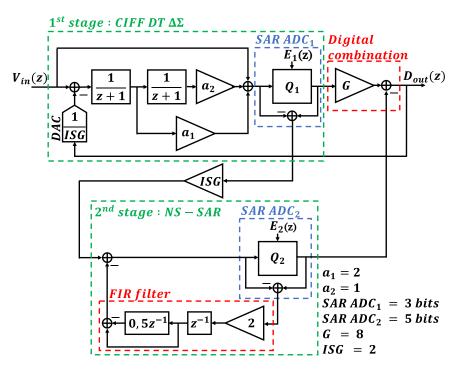

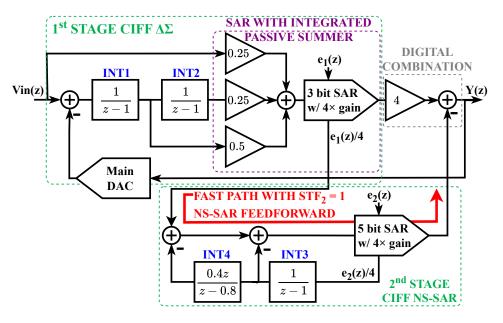

| FIGURE 2.2 –  | DIAGRAM OF THE PROPOSED LNC-SMASH WITH NS-SAR STAGE                                                                                                                                               | 82 |

| FIGURE 2.3 –  | SIMULATED OUTPUT POWER SPECTRUM DENSITY OF THE PROPOSED ADC                                                                                                                                       | 85 |

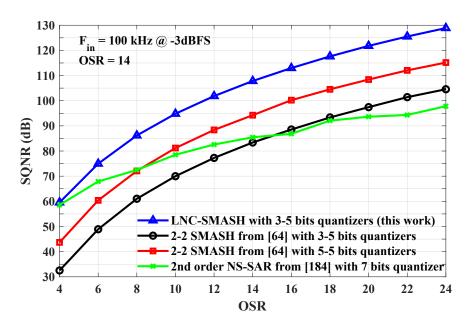

| FIGURE 2.4 –  | COMPARISON OF THE SQNR FOR THE LNC-SMASH OF THIS WORK WITH A 2-2 SMASH AND AN NS-SAR WITH EQUIVALENT CAPACITOR AREA                                                                               | 85 |

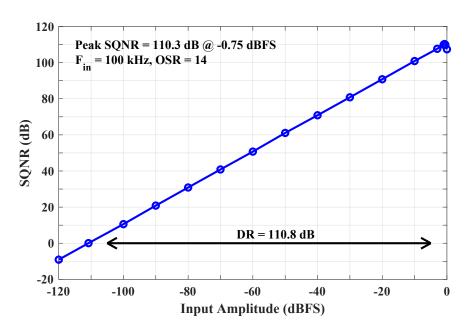

| FIGURE 2.5 –  | SIMULATED SQNR WITH VARYING INPUT AMPLITUDE                                                                                                                                                       | 86 |

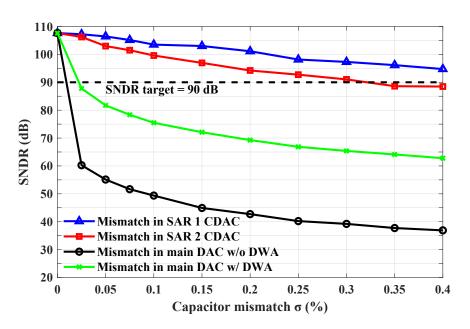

| FIGURE 2.6 –  | MONTE CARLO SIMULATION OF THE SNDR DEGRADATION FROM THE CAPACITOR MISMATCH IN THE NS-SAR STAGE'S CDAC FOR THE PROPOSED LNC-SMASH VS THE ISOLATED NS-SAR SECOND STAGE WITH 10KHZ -3DBFS SINE INPUT | 87 |

| FIGURE 2.7 –  | MONTE CARLO SIMULATION OF THE SNDR OF THE PROPOSED LNC-SMASH FOR DIFFERENT CAPACITOR MISMATCH SOURCES WITH 10KHZ -3DBFS SINE INPUT                                                                | 88 |

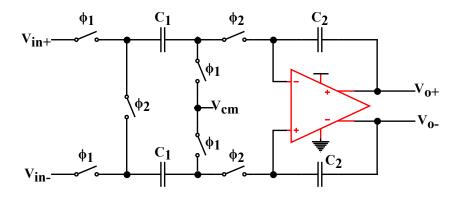

| FIGURE 3.1 –  | SCHEMATIC OF THE SWITCHED-CAPACITOR INTEGRATOR TARGETED BY THE AMPLIFIER DESIGN                                                                                                                   | 92 |

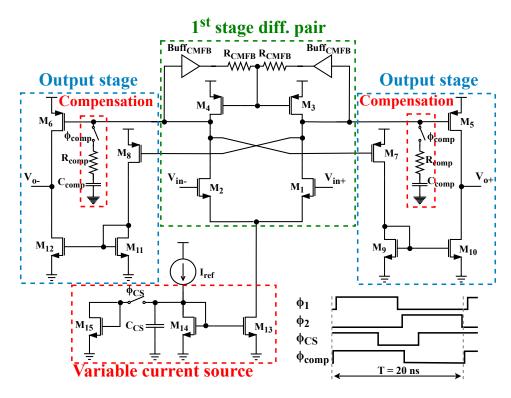

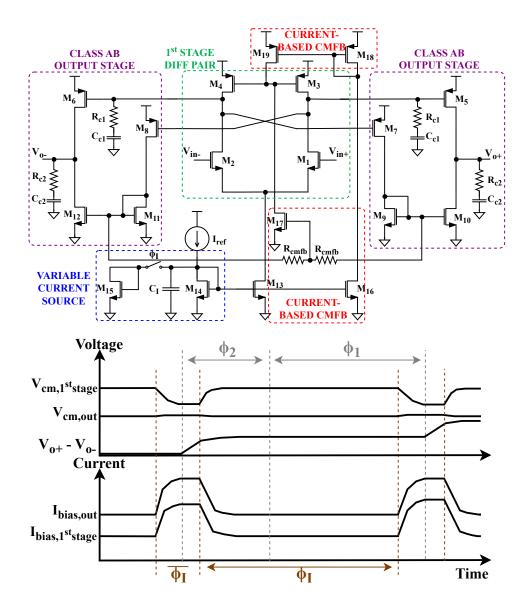

| FIGURE 3.2 –  | SCHEMATIC AND CLOCK DIAGRAM OF THE PROPOSED LOW-POWER RAIL-TO-RAIL DYNAMIC AMPLIFIER. THE COMMON-MODE FEEDBACK OF THE OUTPUT STAGE IS OMITTED FOR CLARITY                                         | 93 |

|               |                                                                                                                                                                                                   |    |

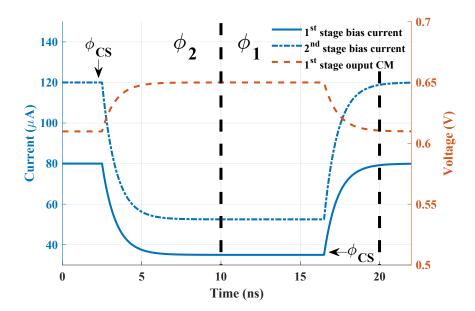

| FIGURE 3.3 – | IDEAL WAVEFORM OF THE BIASING CURRENT DURING AM-<br>PLIFICATION ( $\phi_2$ ) AND SAMPLING ( $\phi_1$ ) PHASES, HIGHLIGH-<br>TING THE CHANGE IN COMMON MODE VOLTAGE BETWEEN<br>THE TWO STAGES CAUSED BY CURRENT VARIATION IN THE<br>FIRST STAGE                                                                                                                           |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

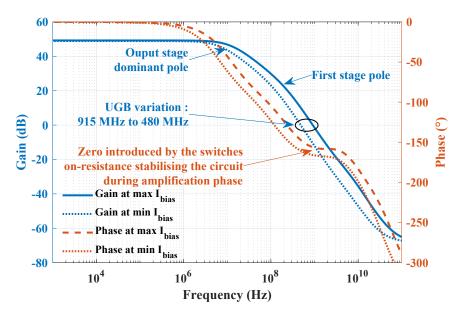

| FIGURE 3.4 – | SIMULATION RESULTS OF THE AC RESPONSE OF THE PROPOSED AMPLIFIER DURING THE AMPLIFICATION PHASE FOR THE HIGHEST AND THE LOWEST VARYING BIAS CURRENT 97                                                                                                                                                                                                                    |

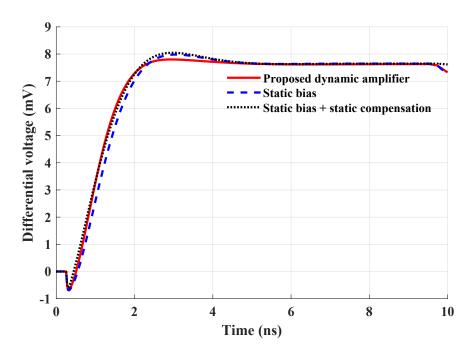

| FIGURE 3.5 – | STEP RESPONSE COMPARISON BETWEEN THE PROPOSED DYNAMIC AMPLIFIER AND AN EQUIVALENT STATIC-CURRENT AND STATIC-COMPENSATION AMPLIFIER DURING THE AMPLIFICATION PHASE. THE RESPONSE IS SIMILAR, YET THE PROPOSED AMPLIFIER CUT THE POWER CONSUMPTION IN MORE THAN HALF IN COMPARISON WITH THE STATIC COMPENSATION CASE AND FURTHER IMPROVES BY 20% FROM THE STATIC BIAS CASE |

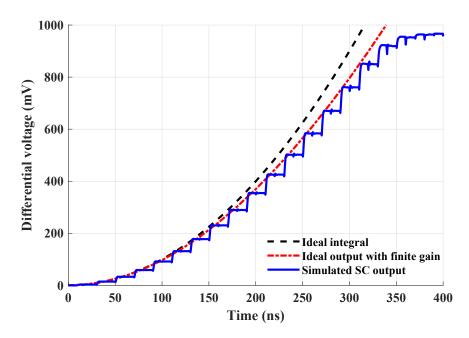

| FIGURE 3.6 – | RAMP INPUT TRANSIENT RESPONSE OF THE SC INTEGRATOR INCORPORATING THE PROPOSED DYNAMIC AMPLIFIER. THE MAXIMUM OUTPUT SWING REACHES 975 MV ON A 1 V SUPPLY                                                                                                                                                                                                                 |

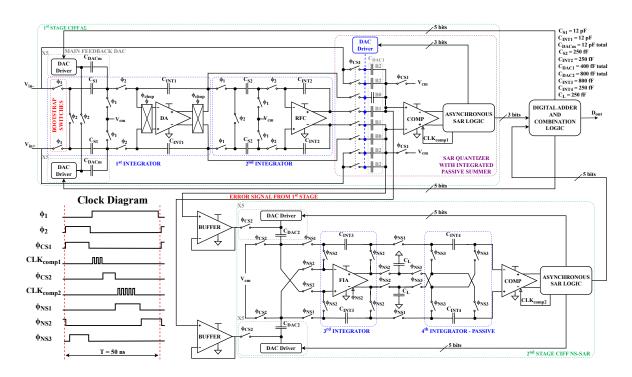

| FIGURE 4.1 – | BLOCK DIAGRAM OF THE PROPOSED LNC-SMASH $\Delta\Sigma$ ADC 107                                                                                                                                                                                                                                                                                                           |

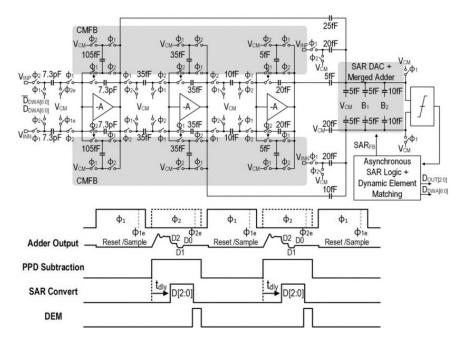

| FIGURE 4.2 – | SCHEMATIC OF THE SIMPLIFIED IMPLEMENTATION OF THE PROPOSED LNC-SMASH $\Delta\Sigma$ ADC WITH CLOCK TIMING DIAGRAM                                                                                                                                                                                                                                                        |

| FIGURE 4.3 – | SCHEMATIC OF THE PROPOSED RAIL-TO-RAIL DYNAMIC AMPLIFIER WITH SIMPLIFIED WAVEFORMS. OUTPUT VOLTAGE CMFB OMITTED FOR CLARITY                                                                                                                                                                                                                                              |

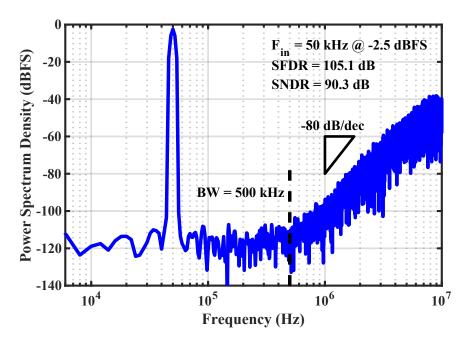

| FIGURE 4.4 – | SIMULATED POWER SPECTRUM DENSITY OF THE PROPOSED ADC                                                                                                                                                                                                                                                                                                                     |

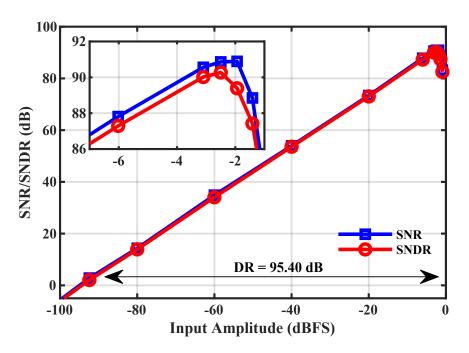

| FIGURE 4.5 – | SIMULATED SNR AND SNDR AS FUNCTIONS OF INPUT AMPLITUDE FOR AN INPUT SIGNAL OF 50 KHZ                                                                                                                                                                                                                                                                                     |

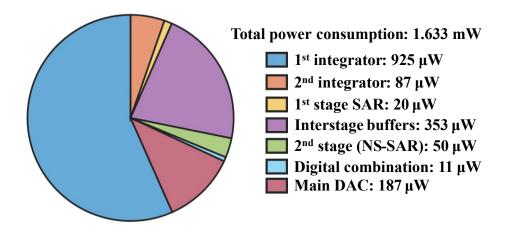

| FIGURE 4.6 – | POWER DISTRIBUTION FOR THE STAGES OF THE PROPOSED ADC (SIMULATED)                                                                                                                                                                                                                                                                                                        |

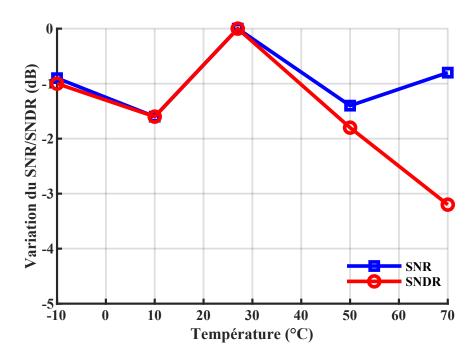

| FIGURE 5.1 – | SIMULATION DE LA VARIATION DU SNR ET DU SNDR EN FONCTION DE LA TEMPÉRATURE                                                                                                                     | 118   |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

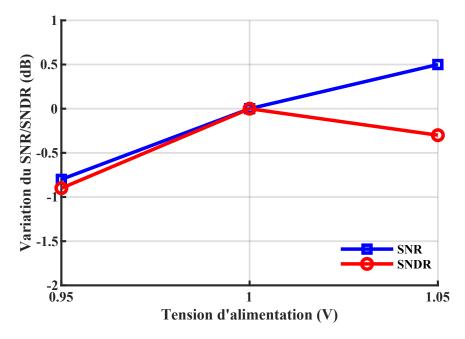

| FIGURE 5.2 – | SIMULATION DE LA VARIATION DU SNR ET DU SNDR EN FONCTION DE LA TENSION D'ALIMENTATION                                                                                                          |       |

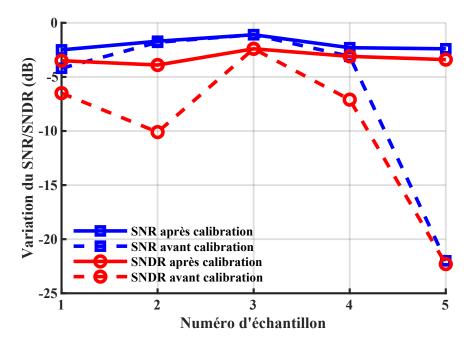

| FIGURE 5.3 – | SIMULATION DE LA VARIATION DU SNR ET DU SNDR POUR 5<br>ÉCHANTILLONS INCLUANT DES VARIATIONS DE PROCÉDÉ<br>ALÉATOIRES                                                                           |       |

| FIGURE 5.4 – | NUAGE DE POINTS MONTRANT LE COMPROMIS EFFICACITÉ<br>ÉNERGÉTIQUE/RÉSOLUTION POUR LES ADC SÉLECTIONNÉS<br>DANS LA REVUE DE LITTÉRATURE. L'ADC LNC-SMASH PRO-<br>POSÉ EST AJOUTÉ PARMI LES POINTS | . 121 |

| FIGURE 5.5 – | NUAGE DE POINTS MONTRANT L'ENOB EN FONCTION DE LA BANDE PASSANTE POUR LES 60 MEILLEURS DESIGNS ÉTUDIÉS ( $FOM_{Sc} > 172$ DB). L'ADC LNC-SMASH PROPOSÉ EST AJOUTÉ PARMI LES POINTS             |       |

### LISTE DES ABRÉVIATIONS

**ADC** Analog-to-Digital Converter

**BW** Bandwidth

**CCIA** Capacitively Coupled Instrumentation Amplifier

**CCO** Current-Controlled Oscillator

**CDAC** Capacitive DAC

**CEF** Cost Effectiveness Factor

**CIFF** Cascade of Integrators with Feedforward

**CMFB** Common-Mode Feedback

**CMOS** Complementary Metal Oxide Semiconductor

CT Continuous Time

DA Dynamic Amplifier

**DAC** Digital-to-Analog Converter

**DR** Dynamic Range**DT** Discrete Time

**DWA** Data Weight Averaging

**EF** Error Feedback

ENOB Effective Number of Bits

FFT Fast Fourrier Transform

FIA Floating Inverter Amplifier

FIR Finite Impulse Response

FOMFigure Of Merit $FOM_{Sc}$ Schreier's FOM $FOM_{Wa}$ Walden's FOM

**HDL** Hardware Description Language

IA Intelligence ArtificielleIIR Infinite Impulse Response

IoT Internet-of-Things

ISG Interstage Gain

**ISI** Intersymbol Interference

LNC-SMASH Lean Noise-Canceling SMASH

**LUT** Lookup Table

MASH Multi-Stage Noise ShapingMES Mismatch Error ShapingNC-SMASH Noise-Canceling SMASH

NS-SAR Noise-Shaping SAR

NTF Noise Transfer Function

OSR Oversampling Ratio

OTA Operational Transconductance Amplifier

PLL Phase-Locked Loop

**PSD** Power Spectrum Density

**PVT** Process, Voltage and Temperature

PWM Pulse-Width ModulationRFC Recycling Folded Cascode

**SAR** Successive Approximation Register

SC Switched Capacitors

**SFDR** Spurious-Free Dynamic Range

S/H Sample and Hold SMASH Sturdy MASH

**SNDR** Signal-to-Noise and Distortion Ratio

**SNR** Signal-to-Noise Ratio

**SoC** System-on-Chip

**SQNR** Signal-to-Quantization-Noise Ratio

**STF** Signal Transfer Function

**TD** Time Domain

VCDL Voltage-Controlled Delay LineVCO Voltage-Controlled OscillatorWSN Wireless Sensor Network

### **REMERCIEMENTS**

Je tiens avant tout à remercier mes directeurs de recherche prof. Alexandre Robichaud et prof. Paul-Vahé Cicek. En plus de prendre le temps de suivre l'évolution de mon projet avec attention et de fournir de précieux conseils et encouragements, ils ont aussi été d'excellents guides dans ma carrière de jeune chercheur. Travailler avec eux est à la fois enrichissant, instructif, motivant et même amusant. J'ai déjà hâte de poursuivre l'aventure au doctorat.

J'aimerais aussi remercier mes parents. Ma mère qui m'a toujours encouragé et motivé de manière indéfectible. Mon père pour son support, ses encouragements et les soupers du samedi pendant lesquels il s'est probablement tapé le contenu en entier de ce mémoire une semaine à la fois.

Finalement, je remercie le CRSNG et le FRQNT pour l'appui financier, ainsi que CMC Microsystems pour l'accès aux outils de conception et aux technologies de fabrication CMOS.

### **AVANT-PROPOS**

Le présent travail de recherche est structuré sous forme d'un mémoire par articles. Chaque chapitre du mémoire correspond à un article ou un acte de conférence publié dans le cadre du projet de recherche.

Le premier chapitre présente une revue de littérature couvrant l'ensemble des architectures de convertisseurs analogiques-numériques à suréchantillonnage.

Le second chapitre couvre la principale innovation du projet de recherche, soit l'élaboration de la nouvelle architecture d'ADC  $\Delta\Sigma$  à un haut niveau d'abstraction. Le principe de l'annulation de bruit reposant sur la propriété de feedforward intrinsèque au NS-SAR est introduit avec des simulations haut niveau démontrant le fonctionnement de l'innovation.

Le chapitre suivant constitue le point de départ de la conception du circuit électronique implémentant la nouvelle architecture d'ADC. Ce chapitre se concentre sur le premier intégrateur du circuit. Il s'agit du bloc de circuit ayant les contraintes de conception les plus sévères en raison du bruit thermique. Ainsi, un nouvel amplificateur dynamique hybride permettant d'optimiser l'opération statique et dynamique pour limiter la consommation de puissance est proposé.

L'implémentation du reste du circuit électronique de l'ADC est présentée dans le chapitre quatre. Le circuit de l'ADC  $\Delta\Sigma$  complet y est détaillé avec des simulations niveau transistor montrant les performances atteintes.

Le cinquième et dernier chapitre ne provient pas d'un article publié et inclut les derniers résultats de simulation présentant la robustesse du circuit aux variations de procédé, de température et de tension d'alimentation. Les performances de l'ADC conçu dans ce projet de recherche sont aussi comparées à celles de l'état de l'art dans ce chapitre.

### INTRODUCTION

# PROBLÉMATIQUE DE RECHERCHE

Grâce aux avancées fulgurantes de la microélectronique au cours des dernières décennies, on assiste à un déploiement massif des technologies embarquées, notamment avec l'intelligence artificielle (IA) en périphérie, l'Internet des objets (IoT) et les réseaux de capteurs [1, 2, 3]. Les exigences technologiques actuelles sont particulièrement élevées : les systèmes doivent être toujours plus rapides, plus performants, plus compacts, et surtout plus économiques. Par ailleurs, les circuits doivent être très économes en puissance pour préserver la durée de vie des batteries. Dans ce contexte, les spécifications attendues pour les circuits électroniques explosent, portées par une demande croissante pour des produits de haute technologie.

Le rétrécissement constant des noeuds de fabrication des dés de silicium permet d'améliorer les performances des circuits numériques années après année [4]. Par contre, les circuits analogiques peinent à suivre la cadence puisqu'ils bénéficient beaucoup moins des avantages inhérents aux nouvelles technologies [5]. Les nouveaux noeuds *deep submicron* permettent notamment de réduire l'encombrement des circuits, d'augmenter la fréquence de commutation des transistors numériques et de limiter la consommation de puissance grâce à une réduction des capacités parasites et de la tension d'alimentation. Or, bien que les circuits analogiques puissent bénéficier d'une part de la réduction d'espace et des capacités parasites, il est souvent nécessaire d'augmenter la taille des transistors bien au-delà du minimum technologique pour atteindre des transconductances, des résistances de sortie, et un matching conformes aux spécifications. Aussi, la diminution des tensions d'alimentation limite la plage de tension disponible dans les circuits analogiques, ce qui complique l'empilement des transistors, réduit

la marge de fonctionnement pour maintenir les transistors en saturation et limite l'amplitude maximale des signaux, les rendant plus sensibles au bruit [5].

Ainsi, d'une part, les spécifications explosent, et d'autre part, les nouvelles technologies de fabrication offrent peu d'avantages, voire nuisent aux performances des circuits analogiques. Il n'est donc pas surprenant que la majorité du traitement du signal soit aujourd'hui entièrement réalisé de manière numérique [6]. Cela renforce d'autant plus l'importance des ADC, car de nombreux blocs fonctionnels, historiquement implémentés en électronique analogique, sont désormais réalisés à l'aide de microprocesseurs ou de circuits numériques dédiés. Dans ces architectures, l'ADC devient souvent le seul et dernier maillon analogique du système [5, 6]. L'évolution des techniques et des architectures d'ADC est donc cruciale pour permettre aux circuits modernes d'atteindre les performances attendues. En l'absence de solutions architecturales adaptées, les ADC deviennent rapidement le facteur limitant des systèmes électroniques, tant en termes de consommation de puissance que de précision et de bande passante. Cette tendance ne fera que s'accentuer avec la poursuite du développement des technologies CMOS, qui favorisent toujours davantage les implémentations purement numériques.

Un des cas critiques de cette problématique concerne les applications nécessitant une haute précision, c'est-à-dire un rapport signal sur bruit et distorsion (SNDR) élevé. Dans les ADC, l'augmentation de la précision passe par l'augmentation du nombre de bits, ce qui complexifie les circuits électroniques. Aussi, les contraintes de bruit thermique doivent être resserrées, forçant l'utilisation de grands condensateurs d'échantillonnage. Ces deux facteurs contribuent à une augmentation significative de la consommation de puissance et à une réduction de la bande passante, dégradant ainsi les performances globales de l'ADC.

Dans l'état de l'art, parmi les différentes topologies d'ADC, l'architecture  $\Delta\Sigma$  est le choix privilégié pour les applications à haute précision. En effet, le filtrage du bruit de quanti-

fication et le suréchantillonnage caractéristiques de cette topologie permettent de relâcher les contraintes de conception des circuits analogiques, tout en atténuant les exigences liées au bruit thermique [7]. Ainsi, les efforts de ce projet de recherche se concentreront l'amélioration des architectures et des circuits des ADC à suréchantillonnage afin de répondre aux spécifications particulièrement exigeantes des applications émergentes. On vise également de permettre aux interfaces analogiques de suivre le rythme rapide des progrès en électronique numérique, tout en atténuant l'impact limitant des ADC sur les performances globales des circuits intégrés modernes.

### **OBJECTIFS**

Le projet de recherche est défini par un objectif principal se déclinant en plusieurs objectifs secondaires. L'objectif principal du projet de recherche est de développer une nouvelle architecture d'ADC  $\Delta\Sigma$  permettant d'atteindre les hautes performances requises par les applications embarquées modernes. On recherche un convertisseur de haute précision permettant de reproduire avec fidélité les données des capteurs tout en maintenant une bande passante intéressante et une faible consommation de puissance.

Les objectifs secondaires permettant de remplir cet objectif principal sont :

- Effectuer une revue de littérature sur l'état de l'art des ADC à suréchantillonnage.

S'inspirer des résultats de la revue de littérature pour générer de nouvelles idées;

- 2. Concevoir une nouvelle architecture d'ADC  $\Delta\Sigma$  fonctionnelle à un haut niveau d'abstraction. On recherche une nouvelle structure de boucle présentant un bon potentiel pour atteindre de hautes performances et améliorer l'état de l'art actuel;

- 3. Développer un ensemble de circuits électroniques permettant d'implémenter la nouvelle architecture d'ADC au niveau transistor avec la technologie CMOS 65 nm. Les circuits

conçus doivent être innovants et adaptés au besoin de l'ADC pour maximiser les performances et minimiser la consommation de puissance;

4. Atteindre des spécifications supérieures ou comparables aux ADC de l'état de l'art.

### **CONTRIBUTIONS**

Les principales contributions à la recherche de ce mémoire par articles sont les suivantes :

1. Une revue de littérature des récentes tendances en conception d'ADC à suréchantillonnage

Une revue de littérature élaborée des dernières avancées en matière d'ADC à suréchantillonnage a été effectuée. L'accent a été mis sur les techniques de conception utilisées dans les cinq dernières années dans toute la gamme des architectures d'ADC à suréchantillonnage :  $\Delta\Sigma$  à temps discret,  $\Delta\Sigma$  à temps continu, SAR à filtrage de bruit, zoom, incrémental, et  $\Delta\Sigma$  dans le domaine temporel. Une comparaison en profondeur de ces topologies est présentée, mettant en lumière les techniques donnant les meilleures performances. De plus, les tendances au niveau de la conception des circuits, en particulier les amplificateurs et les structures de filtre de boucle sont explorés. De nouvelles conclusions sont tirées démontrant les limitations des conceptions actuelles et les tendances anticipées pour le futur. Ces nouvelles conclusions permettront de guider les chercheurs et les concepteurs du domaine pour pousser la recherche sur les ADC à suréchantillonnage vers de nouveaux horizons. Cette contribution a été publiée dans une revue scientifique :

[8] A. Verreault, P.-V. Cicek, et A. Robichaud, "Oversampling ADC: A review of recent design trends," *IEEE Access*, vol. 12, pp. 121753–121779, 2024.

### 2. Un ADC $\Delta\Sigma$ SMASH à annulation de bruit avec un étage SAR à filtrage de bruit

Cette contribution introduit une nouvelle architecture d'ADC ΔΣ SMASH qui annule le bruit de quantification grâce à la propriété de feedforward inhérente au SAR à filtrage de bruit (NS-SAR) utilisé comme deuxième étage. De plus, les erreurs de mismatch engendrées par l'étage NS-SAR sont filtrées par le premier étage, contournant le besoin d'une calibration additionnelle. L'élimination des circuits de calibration et d'annulation de bruit de même qu'une implémentation efficace du NS-SAR rendent cette nouvelle topologie très peu encombrante. Des simulations haut niveau démontrent le bon fonctionnement de la topologie avec un SQNR de 107.7 dB à un OSR de 14. La contribution a été présentée dans une conférence scientifique internationale :

[9] A. Verreault, P.-V. Cicek, et A. Robichaud, "A lean noise-cancelling sturdy MASH delta-sigma ADC with a noise-shaping SAR stage," dans 2023 30th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2023, pp. 1–4.

# 3. Un amplificateur CMOS rail-à-rail dynamique basse puissance pour les filtres à condensateurs commutés dans les ADC hautes performances

Un nouvel amplificateur dynamique optimisé pour les filtres à temps discret dans les ADC a été développé. L'architecture proposée inclut une compensation RC parallèle commutée qui est activée stratégiquement durant la phase d'échantillonnage pour minimiser la consommation de courant de l'amplificateur. La polarisation dynamique de l'amplificateur diminue d'autant plus la consommation d'énergie en diminuant les courants de slew rate durant la phase de convergence linéaire. Les simulations en CMOS 65 nm démontrent une réduction par 3.2 de la consommation de puissance par rapport à un amplificateur statique équivalent. Cette contribution a aussi été présentée dans une conférence scientifique internationale :

[10] A. Verreault, P.-V. Cicek, et A. Robichaud, "A rail-to-rail low-power dynamic CMOS amplifier for switched-capacitor filters in high-performance ADC," dans 2024 IEEE

67th International Midwest Symposium on Circuits and Systems (MWSCAS), 2024, pp. 1230–1234.

# 4. Un ADC $\Delta\Sigma$ SMASH à annulation de bruit en CMOS 65 nm atteignant 500 kHz de bande passante et 90 dB de SNDR

Une implémentation en CMOS 65 nm de la nouvelle architecture d'ADC  $\Delta\Sigma$  à annulation de bruit est proposée. L'étage du NS-SAR bénéficie d'un relâchement significatif des contraintes de conception par le filtrage de bruit additionnel apporté par le premier étage, permettant de maximiser l'efficacité en puissance. Une amélioration de l'amplificateur dynamique innovant est proposée pour optimiser le compromis taille/consommation de puissance dans le premier intégrateur du circuit. La réutilisation judicieuse des condensateurs du SAR du premier étage avec un ajustement de la tension de référence permet aussi d'implémenter un sommateur passif réduisant d'autant plus la consommation de puissance sans dégrader les performances. Les résultats de simulation démontrent d'excellentes spécifications avec une bande passante de 500 kHz et un SNDR de 90.3 dB à une consommation de puissance de 1.633 mW. Cette contribution a été acceptée pour présentation orale à la conférence internationale NEWCAS de L'IEEE qui aura lieu sous peu :

[11] A. Verreault, P.-V. Cicek, et A. Robichaud, "A 500 kHz-BW, 90 dB-SNDR lean noise-canceling SMASH delta-sigma ADC in 65 nm CMOS," dans 2025 23rd IEEE Interregional NEWCAS Conference (NEWCAS), in press.

### **CHAPITRE I**

### OVERSAMPLING ADC: A REVIEW OF RECENT DESIGN TRENDS

Antoine Verreault<sup>1</sup>, Paul-Vahé Cicek<sup>2</sup> et Alexandre Robichaud<sup>1</sup>

Département des Sciences appliquées, Université du Québec à Chicoutimi (UQAC), Chicoutimi, Canada

Département d'Informatique, Université du Québec à Montréal (UQAM), Montréal, Canada

Article publié dans la revue « IEEE Access » en août 2024.

## 1.1 RÉSUMÉ EN FRANÇAIS

Les convertisseurs analogiques-numériques à suréchantillonnage constituent la base des interfaces de données haute performance et haute précision en raison de leur remarquable capacité à filtrer le bruit de quantification. Cette caractéristique en fait le choix privilégié pour les applications nécessitant un rapport signal sur bruit (SNR) élevé et une bande passante modérée, tout en offrant une grande flexibilité de conception. Cet article propose une revue approfondie des avancées récentes en matière d'ADC à suréchantillonnage dédié à ces applications. Spécifiquement, la revue de littérature se concentre sur les techniques de conception utilisées au courant des 5 dernières années en couvrant toute la gamme des architectures d'ADC à suréchantillonnage :  $\Delta\Sigma$  à temps discret,  $\Delta\Sigma$  à temps continu, SAR à filtrage de bruit, zoom, incrémental, et  $\Delta\Sigma$  dans le domaine temporel. Une comparaison détaillée de ces différentes topologies est présentée, mettant en lumière les designs qui atteignent les meilleures figures de mérite. De plus, ce papier explore les tendances de conception au niveau circuit qui sont utilisées dans ces architectures, avec une attention particulière aux amplificateurs et aux structures de filtre de boucle. De nouvelles conclusions sont tirées démontrant les limitations de la plupart des travaux de recherche dans le contexte de l'implémentation d'ADC dans des

systèmes complets, tout en donnant un aperçu des tendances anticipées qui façonneront le domaine dans le futur.

### 1.2 ABSTRACT

Oversampling ADC serve as the backbone of high-performance, high-precision data interfaces, owing to their remarkable ability to filter out quantization noise. This attribute makes them the preferred choice for applications requiring high signal-to-noise ratio (SNR) and moderate bandwidth, with great design flexibility. This paper provides an extensive survey of the latest advancements in oversampling ADC tailored for such applications as documented in recent literature. Specifically focusing on design techniques employed within the last five years, the survey encompasses various oversampling ADC architectures, including discrete-time and continuous-time  $\Delta\Sigma$ , noise-shaping SAR, zoom, incremental, and time-domain modulators. A thorough performance comparison between these different topologies is presented, highlighting designs that achieve the best figures-of-merit. Furthermore, the paper explores circuit-level design trends commonly shared among these architectures, with particular attention given to amplifier designs for loop filters. Conclusions drawn highlight the limitations of much of the research works in the context of implementing ADC within complete systems, while also providing insight into the expected future trends that will shape the field moving forward.

### 1.3 INTRODUCTION

The relentless advance of semiconductor technology has brought in an era of increasingly efficient digital signal processing as CMOS technology nodes continue to shrink. This progression has led to remarkable improvements in computational power, speed, and energy efficiency, making signal processing in the digital domain the preferred approach in modern

electronic systems. Nevertheless, the physical world operates in the analog domain, necessitating cutting-edge analog interfaces to fully leverage the benefits of digital signal processing. Consequently, analog-to-digital converters (ADC) can quickly become bottlenecks in the signal chain if they are not specified and designed with great care.

To meet the demands of modern electronic systems, research on improving ADC circuits in terms of resolution, power efficiency, noise reduction, speed, accuracy, and miniaturization is relentless. Among all the proposed solutions and topologies, the delta-sigma ( $\Delta\Sigma$ ) configuration is of particular interest. By cleverly combining feedback error correction and oversampling to push quantization noise outside of the signal band, the  $\Delta\Sigma$  architecture allows for very high precision using electronic blocks with looser specifications than with alternate ADC topologies.

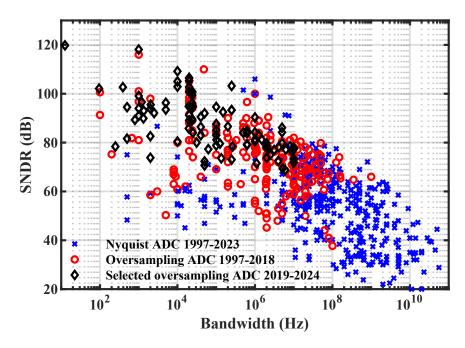

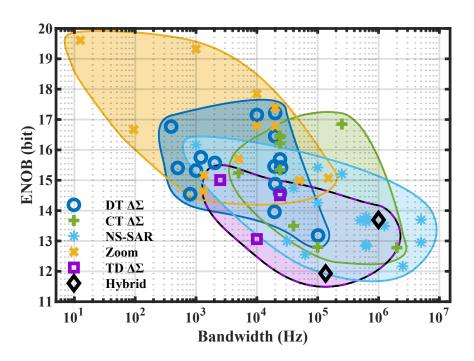

Although the original concepts of  $\Delta\Sigma$  modulation date back to the early 1960s [12, 13, 14],  $\Delta\Sigma$  converters (and oversampling ADC in general) remain a primary research focus for high signal-to-noise-and-distortion ratio (SNDR) applications. The prevalence of oversampling converters among designs with a SNDR above 80 dB, as illustrated in Fig. 1.1, underscores their critical role in achieving high precision and high performance in ADC design, especially in recent years. The ADC data points are sourced from Murmann's database[15] which comprises data from the International Solid-State Circuits Conference (ISSCC) and the IEEE VLSI Technology Symposium from 1997 to 2023. The black diamond datapoints on the figure represent the ADC designs studied in this review paper, all of them oversampling topologies gathered from various IEEE journals and conferences published in the past 5 years.

With such a clear trend, it should be no surprise that oversampling ADC stand out as the go-to in high-precision, low-bandwidth applications. For instance, high-performance  $\Delta\Sigma$  ADC are often used in wireless sensor nodes, precision industrial and research process

FIGURE 1.1: Scatter plot illustrating the relationship between SNDR and bandwidth for the selected oversampling ADC and those from Murmann's database.

instrumentation or high-fidelity audio processing. However, such applications demand not only high SNDR, but also low power consumption (given that many of these systems are battery-powered) and cost effectiveness (to facilitate widespread adoption). Satisfying these requirements imposes strict design constraints, which have been the focus of numerous research endeavors. Hence, this review paper aims to explore recent trends in oversampling ADC where research emphasis lies not on maximizing bandwidth, but rather on enhancing SNDR at minimal cost and power overhead.

The paper is structured as follows. Firstly, section 1.4 presents the methodology. Section 1.5 then provides a concise review of  $\Delta\Sigma$  modulation and an introduction to the different oversampling ADC topologies. Next, section 1.6 offers an overview of the current state of the art, including a comparison of key figures-of-merit (FOM) and performance metrics. Subsequently, sections 1.7 and 1.8 explore in depth system-level and circuit-level design trends, respectively. Section 1.9 discusses system-on-chip (SoC) implementation and ADC

benchmarking, shedding light on FOM limitations. Finally, section 1.10 summarizes the main findings and presents future perspectives.

### 1.4 METHODOLOGY

To ascertain the prevailing trends in oversampling ADC design tailored for high-precision applications, an exhaustive review was conducted throughout prominent IEEE journals and conferences spanning the past five years. Only oversampling ADC designs deemed suitable for high-precision and moderate bandwidth applications were considered, discarding those with an effective number of bits (ENOB) below 11 bits and those with a bandwidth in excess of 10 MHz. Numerous applications require ADC performance within these specifications[7, 16, 17, 18, 19]. For instance, sensor data acquisition in Internet of things (IoT), sensor nodes and industrial process instrumentation demands high precision, often well over 11 bits. Depending on the nature of the signals involved, bandwidth can vary from a few hertz for temperature or humidity detection to megahertz for ultrasound imaging. Signal processing in audio and biomedical monitoring applications is also notable for requiring high accuracy, but moderate bandwidth. Furthermore, low-bandwidth, low-power communication protocols benefit from such specifications with highly efficient oversampling ADC.

The lower cutoff ENOB limit of 11 bits is selected since simpler Nyquist ADC are able to achieve ENOB up to 10 to 12 bits with standard manufacturing process matching. Beyond this precision level, calibration or other special design techniques are required to improve accuracy, enhancing the attractiveness of the oversampling ADC alternative. This survey focuses on energy efficiency enhancement and implementation cost reduction, rather than bandwidth boosting, which is not a critical factor for the target applications considered.

The scrutinized publications include the Journal of Solid-State Circuits (JSSC), IEEE Transactions on Circuits and Systems I & II (TCAS I & II), IEEE Transactions on VLSI Systems, Solid-State Circuit Letters, as well as the International Solid-State Circuits Conference (ISSCC) and Custom Integrated Circuits Conference (CICC). Additionally, five papers sourced from Murmann's database [15] were considered, despite dating from more than five years, since their performance still rivals even the latest state-of-the-art designs. Each selected paper presents a physical tape-out implementation and corresponding measurement results.

The analysis and discussion in this survey revolve around the design techniques used in the selected works, which are grouped by topology, with the main innovations and design trends identified. All techniques discussed have been used in some of the selected state-of-the-art designs.

### 1.5 OVERVIEW OF OVERSAMPLING ADC STRATEGIES

This section will cover the basics of oversampling ADC. The principle of operation of this ADC category will be demonstrated using the quintessential oversampling topology, the discrete-time (DT)  $\Delta\Sigma$  ADC. Following this, we will introduce and discuss the various other oversampling ADC topologies featured in this review.

The principle of operation of oversampling ADC is to convert numerous successive low bit-count samples into a single high-resolution output, thus earning its designation as an *oversampling* ADC. By incorporating the quantizer component within an error-correcting feedback loop, precision can be significantly enhanced.

For readers new to this field, some excellent textbooks offer more in-depth insight into the inner workings of this ADC family [7, 20].

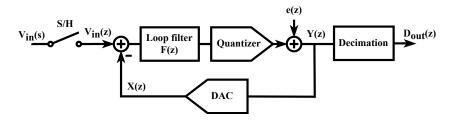

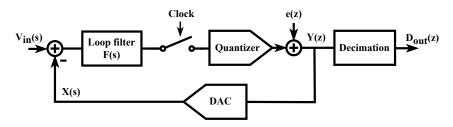

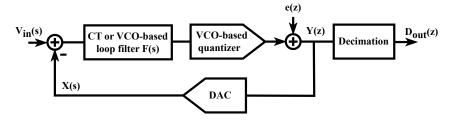

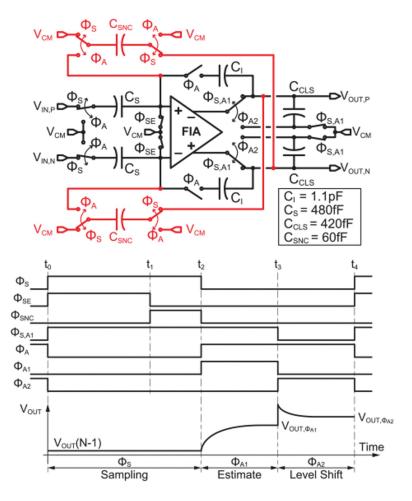

### 1.5.1 THE DISCRETE-TIME $\Delta\Sigma$ MODULATOR

Fig. 1.2 depicts the block schematic of the DT version of the  $\Delta\Sigma$  ADC. The conversion process begins with the sample-and-hold (S/H) stage, which discretizes the analog input signal in time. Subsequently, the signal undergoes low-pass filtering through the loop filter F(z). This circuit block serves as the error correction element in the feedback loop and is commonly implemented using a switched-capacitor integrator circuit. Following this, the signal enters a quantizer, typically a flash ADC[21] with a low bit-count (1 to 4 bits). The feedback path features a digital-to-analog converter (DAC) allowing for the subtraction of the digital output of the quantizer Y(z) from the analog input  $V_{in}(z)$ . This DAC is one of the most critical blocs in the architecture as any error or distortion it introduces are not shaped by the error-correcting loop due to its placement in the feedback path. The high-frequency digitized data stream Y(z) is finally converted into a lower frequency, high bit-count output data  $D_{out}(z)$  by means of a decimation filter. The ratio of decimation, equal to the sampling frequency ratio between Y(z) and  $D_{out}(z)$ , is known as the oversampling ratio (OSR). All things being equal, increasing OSR enhances ADC precision. However, this represents a key trade-off in  $\Delta\Sigma$  ADC design, as higher OSR improves SNDR but reduces bandwidth for the same power consumption.

The low bit-count quantizer, due to its coarse voltage steps, introduces substantial errors termed quantization noise and denoted e(z) in Fig. 1.2. Classic feedback theory can be applied

FIGURE 1.2 : Block diagram of the DT  $\Delta\Sigma$  ADC.

to derive ADC transfer functions for both input  $V_{in}(z)$  and quantization noise e(z), designated respectively as signal transfer function

$$STF(z) = \frac{Y(z)}{V_{in}(z)} = \frac{F(z)}{1 + F(z)} = z^{-1}$$

(1.1)

and noise transfer function

$$NTF(z) = \frac{Y(z)}{e(z)} = \frac{1}{1 + F(z)} = 1 - z^{-1},$$

(1.2)

where

$$F(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{1.3}$$

is the transfer function of an ideal integrator loop filter.

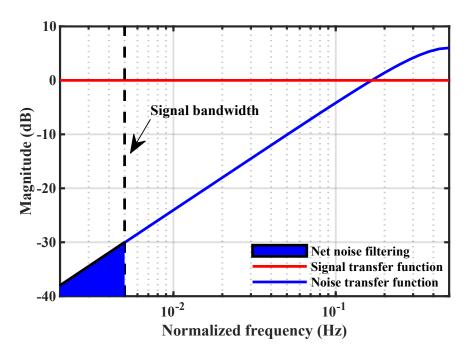

With these equations plotted in Fig. 1.3, it becomes clear that the error signal undergoes strong filtration, while the input signal is unaffected. As highlighted with the blue shading, the remaining noise in the signal band is significantly attenuated by high-pass filtering through the feedback loop, an effect commonly referred to as noise shaping. Indeed, at the ADC output, the decimation filter acts as a sharp low-pass filter, effectively removing residual noise above the signal band. To achieve sharper noise shaping, a higher-order loop filter may be used, which can be performed simply by cascading additional switched-capacitor integrators. Higher-order noise shaping may reduce the OSR required to meet specific SNDR requirements, albeit at the cost of critical stability challenges.

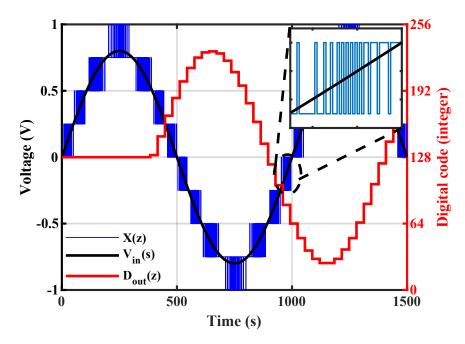

Fig. 1.4 illustrates the transient waveforms of a 1st-order DT  $\Delta\Sigma$  ADC. Both sampling frequency and amplitude are normalized to 1 Hz and  $\pm 1$  V, respectively. Input  $V_{in}(s)$  is a sinusoid with a frequency one-thousandth that of the sampling frequency. OSR is set to 32 and the quantizer has 9 levels. Modulator output Y(z), prior to decimation, presents a rapidly

FIGURE 1.3 : Signal and noise transfer function of a typical  $\Delta\Sigma$  ADC. The shaded region shows the total shaping of the quantization noise from both the loop filter and the decimation filter.

FIGURE 1.4 : Simulated transient waveforms of a 1st-order  $\Delta\Sigma$  ADC with 9 quantizer levels for signals labelled in Fig. 1.2.

varying low-resolution digital stream, which, for visual convenience, is illustrated through DAC output X(z) on the figure. The error-correcting loop ensures that the mean value of X(z) closely tracks input  $V_{in}(s)$ . Notably, upon zooming into the rising slope of the input sinusoid, it becomes evident that bits are predominantly low at the onset and tend to shift high more often later since the amplitude of the input has risen. After decimation, output  $D_{out}(z)$  yields a slower, high-resolution digital code.

One notable limitation of  $\Delta\Sigma$  ADC, clearly depicted in the figure, is the substantial delay imposed by the decimation filter before the high-resolution sample is accessible at the output. A solution for this latency issue, which will be covered in detail in a subsequent section, is to use an incremental  $\Delta\Sigma$  architecture. In such a structure, the memory elements of the integrators and of the decimation filter are reset after each conversion, eliminating the conversion latency.

### 1.5.2 THE CONTINUOUS-TIME $\Delta\Sigma$ MODULATOR

Fig. 1.5 illustrates the continuous time (CT) variant of the  $\Delta\Sigma$  ADC. Unlike its DT counterpart, the input remains in the analog domain and is not sampled before entering the loop. Nevertheless, sampling still needs to take place within the quantizer, which requires clocking. In this configuration, the loop filter typically takes the form of an active RC filter. A significant advantage of this setup is its intrinsic anti-aliasing property, a consequence of

FIGURE 1.5 : Block diagram of the CT  $\Delta\Sigma$  ADC.

the filtering operation preceding the sampling. Detailed discussions about this phenomenon and the derivation of loop filter equations can be found in [7]. The CT  $\Delta\Sigma$  modulator is easier to drive because its input impedance is resistive, unlike the switched-capacitor input stage of the DT  $\Delta\Sigma$ . As for noise shaping, it occurs analogously to the DT case. However, the CT architecture is not devoid of drawbacks, including sensitivity to process variations. Indeed, in the CT architecture, the integration constants depend on the RC time constant, which is more liable to be affected by fabrication variations compared to the easily matchable capacitor ratios used in the DT architecture. Additionally, the CT nature of the circuit heightens sensitivity to jitter and DAC waveform symmetry.

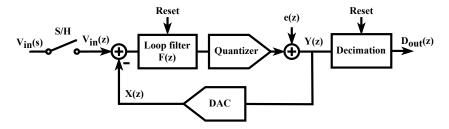

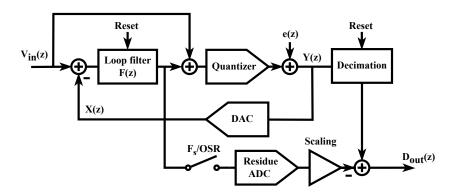

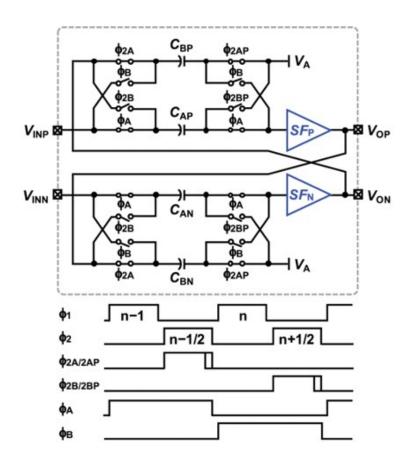

### 1.5.3 THE INCREMENTAL $\Delta\Sigma$ MODULATOR

The incremental  $\Delta\Sigma$  ADC, initially proposed with a current-mode input in [22] and further refined in [23], is a variant of the conventional  $\Delta\Sigma$  architecture. In this topology, the memory elements of the loop filter and the decimation filter are reset for each conversion as depicted in Fig. 1.6, resulting in a Nyquist rate ADC. This resetting of memory elements eliminates output delays, facilitates multiplexing of inputs from an array of sensors and enables implementation of sleep mode between acquisition periods. The formation of idle tones with DC input is also alleviated [7]. Moreover, the decimation filter in the incremental variant is implemented as a simple finite impulse response (FIR) filter instead of the usual infinite impulse response (IIR) filter. Optimal filtration is achieved by weighting the filter more heavily with the first samples and less with the last ones. Indeed, this weighting is optimal because the quantization noise from the last few samples is not shaped by subsequent samples which will serve for the next conversion[7]. However, it is worth noting that the reduced weighting in the incremental variant leads to inferior thermal noise performance compared to conventional  $\Delta\Sigma$  ADC. While conventional  $\Delta\Sigma$  ADC benefit from a thermal noise reduction by a factor of OSR,

FIGURE 1.6 : Block diagram of the incremental  $\Delta\Sigma$  ADC.

the incremental variant experiences a less pronounced reduction, especially with higher-order modulators [18]. Consequently, to meet a given SNR specification, the incremental modulator consumes more power, as higher capacitive loads are required to mitigate thermal noise. Detailed noise analysis and design considerations for incremental  $\Delta\Sigma$  ADC are provided in [24, 25, 26].

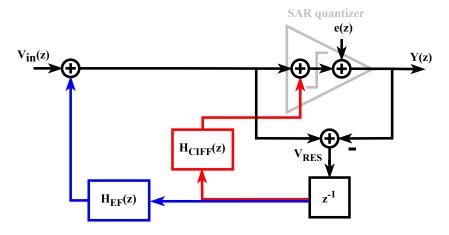

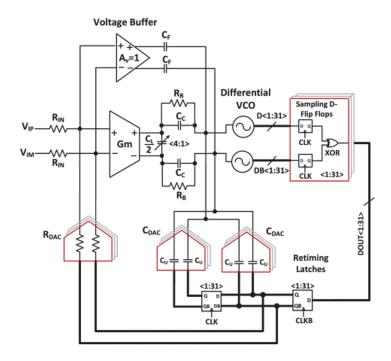

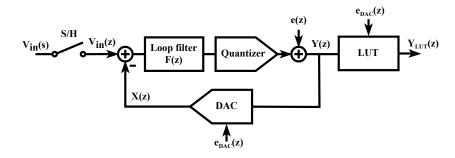

### 1.5.4 THE NOISE-SHAPING SAR TOPOLOGY

The successive approximation (SAR) ADC[21] is a Nyquist ADC which performs a binary search algorithm to discretize signals. It reutilizes the same comparator for every successive comparison, with one comparison per output bit. The SAR ADC is highly efficient, especially in its typical implementation with a capacitive DAC (CDAC). However, at higher precision, the capacitive loading and the area occupied by the CDAC increase significantly, as the capacitor size doubles with each additional bit. Additionally, maintaining low comparator noise becomes more challenging, often requiring a power-hungry preamplifier before the comparator to achieve the necessary accuracy.

An approach to improve the SAR ADC precision without excessive comparator and capacitor requirements is to use it in an oversampling topology: the noise-shaping SAR (NS-SAR). This topology is a relatively recent oversampling ADC architecture introduced

in 2012 [27]. It differs from traditional  $\Delta\Sigma$  ADC in several key ways. Its unique features include: 1) the direct sampling and quantization of the input signal by the SAR quantizer, which typically uses a higher bit-count than conventional  $\Delta\Sigma$  designs; 2) the precise extraction of the residue error at the end of the SAR conversion, which is determined from the remaining voltage on the SAR CDAC array; and 3) the feedback mechanism that conveys only the residue error instead of the full modulator output[28]. High bit-count quantization, as well as only needing to process the residue error, allow the linear blocks of the filter to handle signals with very low swing, significantly easing design constraints.

Fig. 1.7 illustrates the two main NS-SAR topologies: error feedback (EF)[29] and cascaded integrator feed-forward (CIFF)[27]. The fundamental distinction between these architectures lies in the feedback return path: the EF structure feeds back into the CDAC array, while the CIFF structure feeds back into the comparator as an additional offset. This difference affects noise shaping to yield two alternate transfer functions:

$$NTF_{EF}(z) = 1 - H_{EF}(z)z^{-1},$$

(1.4)

FIGURE 1.7: Block diagram of the NS-SAR ADC.

$$NTF_{CIFF}(z) = \frac{1}{1 + H_{CIFF}(z)z^{-1}}.$$

(1.5)

In (1.4), the EF case,  $H_{EF}(z)$  appears in the numerator, facilitating its implementation through a straightforward FIR filter to achieve the desired noise shaping. However,  $NTF_{EF}(z)$  is sensitive to gain variation, as filter coefficients may drift and degrade performance. Conversely, in (1.5), the CIFF case,  $H_{CIFF}(z)$  resides in the denominator, necessitating the use of an integrator or IIR filter to achieve a proper high-pass filter  $NTF_{CIFF}(z)$ , increasing circuit complexity. However, while a sufficiently high gain is required, it need not be precisely tuned, thus relaxing matching constraints compared to the EF case [28]. Combined implementations of both EF and CIFF filter structures have been proposed [30], resulting in a total NTF derived from the multiplication of (1.4) and (1.5).

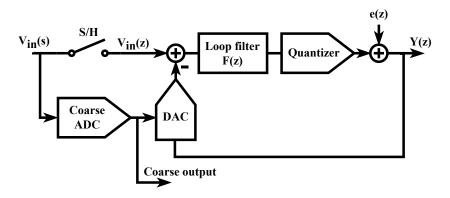

### 1.5.5 THE ZOOM TOPOLOGY

The zoom topology, pioneered by Souri and Makinwa in the early 2010s [31, 32], stands out as the ideal architecture for achieving high precision in low-bandwidth applications. Illustrated in Fig. 1.8, this architecture closely resembles the two-step ADC[21]. Initially, a Nyquist ADC performs coarse quantization, typically using a SAR ADC of 4 to 6 bits.

FIGURE 1.8: Block diagram of the zoom ADC.

Subsequently, a fine quantization stage employs an incremental  $\Delta\Sigma$  in which the feedback DAC output range is dynamically adjusted based on the coarse quantization results. This significantly reduces the resolution requirement of the  $\Delta\Sigma$  stage as the feedback DAC range narrows within a few coarse LSB of the input signal. Hence, selecting a single-bit quantizer is a common design choice due to its inherent linearity. Furthermore, the loop filter is subjected to a minimal input swing thanks to the output of the feedback DAC being zoomed in close proximity to the input level, facilitating simple and power-efficient loop filter amplifier design. A key distinction from conventional two-step ADC is the absence of explicit residue signal computation, which typically introduces offset, gain, and linearity errors through amplification and subtraction circuitry before the fine quantization stage [32].

#### 1.5.6 THE TIME-DOMAIN $\Delta\Sigma$ MODULATOR

In the context of this survey, a *time-domain* (TD)  $\Delta\Sigma$  modulator refers to a  $\Delta\Sigma$  ADC where all or part of the signal processing occurs in the time domain instead of the conventional voltage amplitude domain. The time-encoded information can be represented as frequency, phase, or pulse-width modulation (PWM). The primary objective of this configuration is to achieve a digital-like design that leverages advancements in technology scaling for improved speed and power efficiency. This approach can prove particularly advantageous in deep submicron technology nodes where maintaining accuracy in voltage domain quantizers and filters becomes more challenging at low supply voltage, whereas time-domain accuracy improves due to reduced transition times. However, the typical voltage-controlled oscillators (VCO) used for processing data in the time domain are nonlinear, often requiring the use of calibration and/or linearization techniques[33].

Fig. 1.9 illustrates a typical configuration of TD  $\Delta\Sigma$  ADC. The loop filter can be implemented either using a classical CT integrator or a VCO-based TD integrator. The

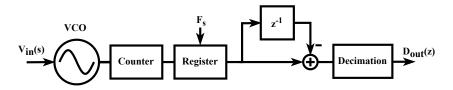

FIGURE 1.9 : Block diagram of a typical TD  $\Delta\Sigma$  ADC.

quantizer is VCO-based and often also contains a digital backend, which includes a counter and additional processing. Accumulating the VCO output in a counter provides intrinsic signal integration, resulting in inherent first-order noise shaping to complement the noise shaping of the loop filter. An overview of different TD  $\Delta\Sigma$  ADC architectures is presented in [34] while detailed exploration of the recent state-of-the-art design trends is covered in later sections of this paper.

# 1.6 STATUS OF THE STATE OF THE ART

## 1.6.1 COMPARISON WITH OLDER DESIGNS AND NYQUIST ADC

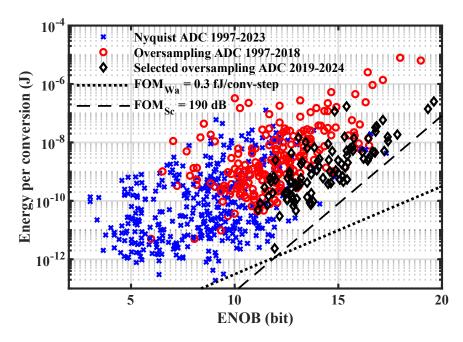

The oversampling ADC targeted in this review paper are compared with various Nyquist and older oversampling ADC designs from Murmann's database [15] in Fig. 1.10. The scatter plot relates energy per conversion to ENOB, visually illustrating the trade-offs between ADC resolution and conversion efficiency.

Trade-offs can also be quantified using FOM, taking into account key performance metrics such as SNDR, bandwidth, and power consumption. Among the most commonly used FOM for oversampling ADC are Schreier's [7]:

$$FOM_{Sc} = SNDR + 10\log\frac{BW}{P},\tag{1.6}$$

FIGURE 1.10: Scatter plot illustrating the trade-off between conversion efficiency and resolution for the selected oversampling ADC and those from Murmann's database.

and Walden's [35, 36]:

$$FOM_{Wa} = \frac{P}{2^{ENOB}F_s},\tag{1.7}$$

where

$$ENOB = \frac{SNDR - 1.76}{6.02},\tag{1.8}$$

BW is the ADC bandwidth, P is the power consumption and  $F_s$  is the Nyquist sampling frequency. Isolating the energy as  $P/F_s$  in (1.6) and (1.7) allows for the plotting of the corresponding slopes in Fig. 1.10. Consequently, we observe that the most optimal designs, exhibiting the highest FOM, tend to cluster towards the lower right corner of the scatter plot along the slopes of the FOM. Indeed, the state-of-the-art frontier closely follows the slope of  $FOM_{Sc}$  at high ENOB and  $FOM_{Wa}$  at lower ENOB, suggesting that these FOM effectively encapsulate relevant design trade-offs. Furthermore, the figure highlights that oversampling

ADC feature superior precision due to their inherent noise-shaping capabilities. The selected designs clearly rank among the top performers.

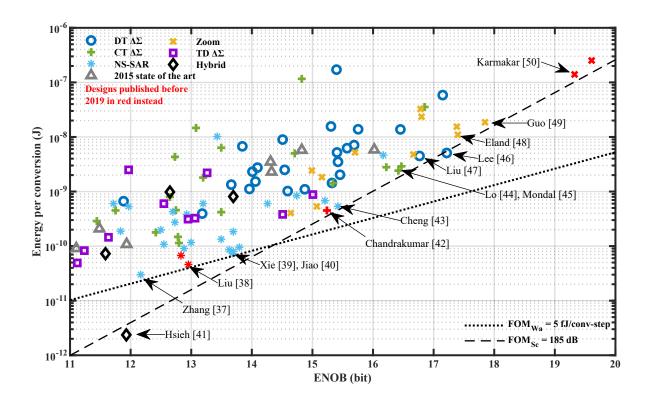

# 1.6.2 SELECTED OVERSAMPLING ADC

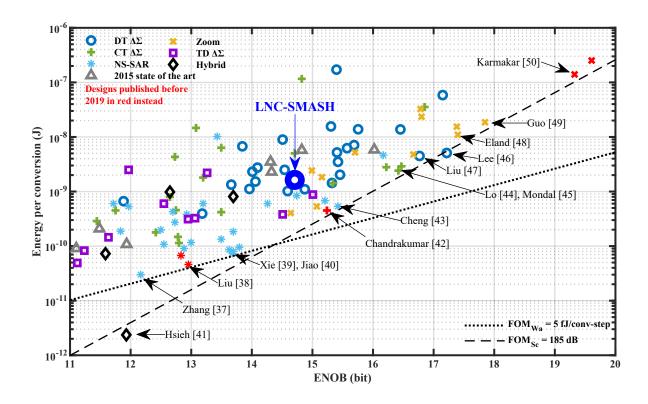

Fig. 1.11 dives deeper into the selected ADC from the previous figure, specifying their topologies: DT  $\Delta\Sigma$ , CT  $\Delta\Sigma$ , NS-SAR, TD  $\Delta\Sigma$  and hybrid designs incorporating both voltage-domain and time-domain stages. The five data points depicted in red, as opposed to the usual color, represent older designs sourced from Murmann's database that are still competitive with the state of the art of the last 5 years and are thus selected for analysis in this paper. Also, gray triangles represent state-of-the-art designs identified in a previous survey from 2015 [16].

Remarkably, there has been a significant enhancement in energy efficiency over the past decade. Many recent designs consume less than a tenth of the energy per conversion while maintaining similar precision compared to state-of-the-art designs from 2015. The designs boasting the highest FOM are identified in the figure, featuring either or both of  $FOM_{Wa}$  below 6.5 fJ/conv-step [37, 38, 39, 40, 41] and  $FOM_{Sc}$  in excess of 183 dB [41, 42, 43, 44, 45, 46, 47, 48, 49, 50].

From a system-level perspective, NS-SAR designs are the top performers at low ENOB. This is demonstrated by the cluster of stars along the  $FOM_{Wa}$  slope between ENOB of 12 and 14 bits in the figure. Between ENOB of 14 and 17 bits, various topologies compete for supremacy. Interestingly, the designs by Lee [46] and Liu [47] stand out as the only DT  $\Delta\Sigma$  converters offering truly cutting-edge performance. For designs requiring precision beyond ENOB of 17 bits, the zoom architecture emerges as the clear leader.

FIGURE 1.11: Scatter plot showcasing the energy/resolution trade-off for the selected ADC with their respective architectures highlighted. Designs with the highest figures of merit are labelled on the plot.

TD  $\Delta\Sigma$  converters exhibit comparatively mediocre power efficiency, as no design comes close to the FOM boundaries shown in the figure. Additionally, the nonlinearity issues of the VCO commonly used in this topology prevent these converters from achieving an ENOB higher than 15 bits. In contrast, every other topology features designs with resolutions exceeding this threshold. Nevertheless, the TD topology remains of interest because it holds significant potential for improvement with recent and upcoming technology nodes, given its compatibility with digital-friendly circuits. Furthermore, hybrid designs including a TD stage are already demonstrating impressive results with Hsieh's highly efficient design[41].

An important piece of information missing from Fig. 1.11 and the prior discussion is bandwidth performance. Focusing solely on the precision vs. energy per conversion tradeoff

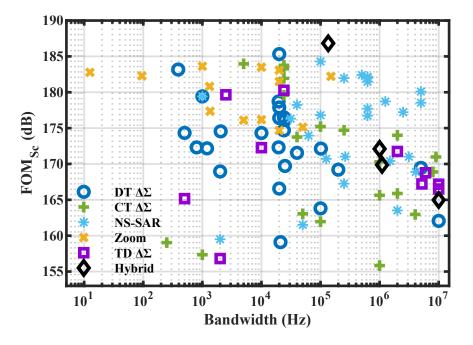

disregards the value of faster designs, as techniques for higher-speed circuits are generally expected to be more complex, thus to consume more power and require a larger area footprint. Hence, Fig. 1.12 presents architecture performance relative to conversion speed, by displaying  $FOM_{Sc}$  of all the designs in Fig. 1.11, but according to bandwidth as the x-axis.

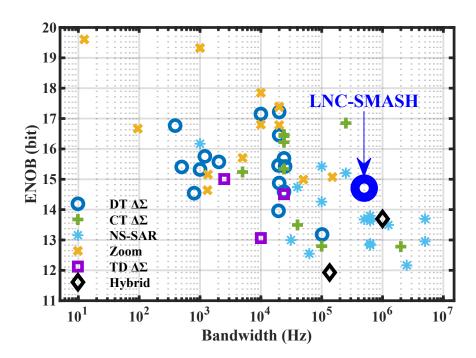

Similarly, Fig. 1.13 presents the bandwidth and ENOB specifications of the top sixty designs that surpass a  $FOM_{Sc}$  of 172 dB. The highlighted areas indicate the design space occupied by each topology, illustrating the trade-offs between bandwidth and precision for each family.

Some clear trends emerge by inspecting these three figures. For higher bandwidth, ranging from 100 kHz up to the 10 MHz limit of this survey, NS-SAR designs dominate performance, particularly at moderate ENOB. As anticipated, the fastest designs exhibit a

FIGURE 1.12 : Scatter plot illustrating the  $FOM_{Sc}$  of the selected ADC in terms of bandwidth with their respective architectures highlighted.

FIGURE 1.13 : Scatter plot indicating ENOB and bandwidth for the top sixty selected ADC  $(FOM_{Sc} > 172 \text{ dB})$ . The zone of optimal operation for each architecture family is highlighted.

slight reduction in peak  $FOM_{Sc}$ , with only Liu's design[38] managing to surpass 180 dB above 1 MHz. In the intermediate bandwidth range of 5 kHz to 100 kHz, top performance is shared between CT and DT  $\Delta\Sigma$ , as well as zoom architectures. While zoom architectures excel in achieving high ENOB, DT and CT  $\Delta\Sigma$  designs lead the moderate to high ENOB space, with CT designs generally demonstrating higher bandwidth. Finally, for bandwidths below 5 kHz, zoom architectures clearly dominate, aside from the DT  $\Delta\Sigma$  design by Liu[47], which presents state-of-the-art performance in this range.

Once more, most TD  $\Delta\Sigma$  and their hybridization with other topologies lag slightly behind in terms of performance. However, their ability to reach high bandwidth due to their TD digital-like processing circuit is clearly illustrated by the group of purple squares and black diamonds on the far right of Fig. 1.12. Maturation of these budding approaches can be expected to yield more competitive performance in the future.

The subsequent sections of the paper delve into the analysis of the design trends studied in the ADC implementations of Fig. 1.11 and Fig. 1.12, starting with a system-level perspective and thereafter honing in on circuit-level techniques.

#### 1.7 SYSTEM-LEVEL DESIGN TRENDS

# 1.7.1 DESIGN TRENDS IN THE CONVENTIONAL DISCRETE-TIME AND CONTINUOUS-TIME $\Delta\Sigma$ TOPOLOGIES

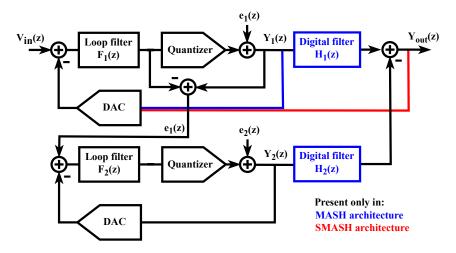

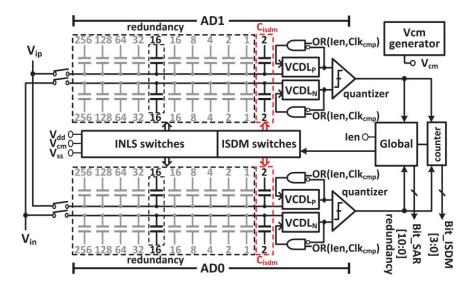

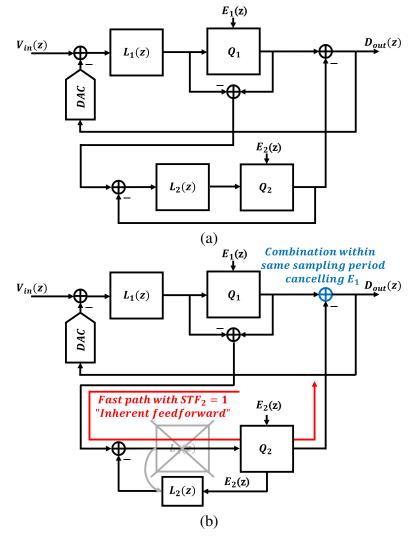

# THE MULTI-STAGE NOISE-SHAPING TECHNIQUE

The primary design considerations in a conventional  $\Delta\Sigma$  architecture revolve around the power/precision trade-off for a given bandwidth constrained by OSR. To benefit from a more favorable trade-off, many designs opt to increase the modulator's noise-shaping order, allowing for a reduction in OSR while maintaining SNDR. However, at higher order, stabilizing the feedback loop becomes increasingly challenging, as the modulator may exhibit instability at high input amplitudes, limiting the practical input range[7]. Addressing this challenge, a clever technique known as multi-stage noise shaping (MASH) was introduced in [51]. This approach involves cascading multiple noise-shaping loops to achieve high-order noise shaping without encountering stability issues. In this method, the quantization error from the first stage is fed into a second noise-shaping modulator stage. The digitized error is ultimately subtracted from the output of the first stage, as depicted in Fig. 1.14. Additional digital filters are required before the subtraction to ensure proper quantization noise filtration. The resulting transfer function is expressed as:

$$Y_{out}(z) = H_1 Y_1 - H_2 Y_2. (1.9)$$

FIGURE 1.14 : Block diagram of the multi-stage noise-shaping (MASH) and the sturdy multi-stage noise-shaping (SMASH)  $\Delta\Sigma$  ADC architectures.

Replacing  $Y_1$  and  $Y_2$  for the noise and signal transfer functions gives :

$$Y_{out}(z) = H_1 ST F_1 V_{in}(z) + H_1 NT F_1 e_1(z) - H_2 ST F_2 e_1(z) - H_2 NT F_2 e_2(z).$$

(1.10)

Designing digital filters  $H_1$  and  $H_2$  to meet the condition

$$H_1NTF_1 = H_2STF_2 \tag{1.11}$$

yields:

$$Y_{out}(z) = STF_1STF_2V_{in}(z) - NTF_1NTF_2e_2(z).$$

(1.12)

As a result, MASH effectively nullifies the error from the initial stage,  $e_1$ , leaving behind solely the error introduced by the second stage quantizer,  $e_2$ , which undergoes substantial attenuation by both NTF. Despite its inception in the 1980s, contemporary designs frequently adopt this strategy, amalgamating stages based on diverse architectures such as NS-SAR, TD, and conventional CT / DT  $\Delta\Sigma$  modulators [40, 52, 53, 54, 55, 56, 57, 58, 59, 60, 61, 62]. Leveraging this approach incorporating a Nyquist converter as either the first stage (0-Xth order modulator) or the second stage (X-0th order modulator) can also be a great technique to improve performance. On one hand, the use of a 0-X MASH narrows the input range of the  $\Delta\Sigma$