UNIVERSITÉ DU QUÉBEC

MÉMOIRE

PRÉSENTÉ À

L'UNIVERSITÉ DU QUÉBEC À CHICOUTIMI

COMME EXIGENCE PARTIELLE

DE LA MAÎTRISE EN INGÉNIERIE

PAR

JEAN-GABRIEL MAILLOUX

PROTOTYPAGE RAPIDE DE LA COMMANDE VECTORIELLE

SUR FPGA À L'AIDE DES OUTILS SIMULINK - SYSTEM GENERATOR

MARS 2008

## *Mise en garde/Advice*

Afin de rendre accessible au plus grand nombre le résultat des travaux de recherche menés par ses étudiants gradués et dans l'esprit des règles qui régissent le dépôt et la diffusion des mémoires et thèses produits dans cette Institution, **l'Université du Québec à Chicoutimi (UQAC)** est fière de rendre accessible une version complète et gratuite de cette œuvre.

Motivated by a desire to make the results of its graduate students' research accessible to all, and in accordance with the rules governing the acceptance and diffusion of dissertations and theses in this Institution, the **Université du Québec à Chicoutimi (UQAC)** is proud to make a complete version of this work available at no cost to the reader.

L'auteur conserve néanmoins la propriété du droit d'auteur qui protège ce mémoire ou cette thèse. Ni le mémoire ou la thèse ni des extraits substantiels de ceux-ci ne peuvent être imprimés ou autrement reproduits sans son autorisation.

The author retains ownership of the copyright of this dissertation or thesis. Neither the dissertation or thesis, nor substantial extracts from it, may be printed or otherwise reproduced without the author's permission.

## RÉSUMÉ

Avec la mécatronique, la recherche effectuée dans ce domaine touche nécessairement à plusieurs disciplines. Cela engendre des problèmes de recherche applicationnels très diversifiés. C'est pourquoi il est important d'établir une plateforme de travail à l'aide d'outils académiques modulaires qui permet de passer d'un algorithme ou d'un problème d'application vers un prototype fonctionnel à tester en laboratoire sur FPGA. Une méthodologie intégrant des outils comme Xilinx System Generator, SimPowerSystems et GAPP offre un environnement de développement organique qui peut évoluer avec la direction de la recherche, tout en évitant les coûts d'une solution commerciale intégrée. De plus, l'accessibilité de ces outils et l'élaboration de cette méthode permettent d'éviter les coûts et le temps de formation du personnel nécessaire avec des outils commerciaux plus complexes. Dans un cadre académique, cela facilite l'intégration de nouveaux étudiants dans un projet de recherche.

La méthode de prototypage rapide est développée afin d'offrir à l'usager de la plateforme de développement une procédure optimale de conception, de validation, de co-simulation et d'optimisation du modèle. Une application de commande vectorielle des moteurs à induction devant répondre à des conditions d'exécution sévères (un court temps de réponse, une taille sur FPGA décente, etc.) est ici proposée afin de développer et tester cette méthode de conception. Les temps de développement sont évalués et la précision des résultats est analysée afin de confirmer la viabilité de cette méthode de prototypage.

## REMERCIEMENTS

C'est avec plaisir que je prends ces quelques lignes, si peu nombreuses, afin de remercier les personnes qui m'ont soutenu durant ce projet de recherche.

De façon spéciale, je tiens à remercier mon directeur M. Rachid Beguenane qui a cru en moi et m'a permis de faire ce projet au sein de l'équipe de recherche en micro-électronique et traitement informatique des signaux (ERMETIS). Son support, son professionnalisme et surtout, sa disponibilité ont rendu possible la réalisation de ce travail. Également, je veux remercier mon collègue Stéphane Simard qui a dû répondre à un nombre incalculable de questions. Sans son savoir et sa connaissance des ressources d'information disponibles, la réalisation de ce travail eût été bien difficile.

Je remercie aussi ma charmante et jolie conjointe, qui ne cesse jamais d'être une source de réconfort et d'encouragement.

## Table des matières

|                                                                                  |     |

|----------------------------------------------------------------------------------|-----|

| Résumé .....                                                                     | ii  |

| Remerciements .....                                                              | iii |

| Table des matières .....                                                         | iv  |

| Table des figures.....                                                           | ix  |

| Liste des tableaux .....                                                         | xii |

| CHAPITRE 1 .....                                                                 | 13  |

| Introduction et problématique .....                                              | 13  |

| 1.1    Introduction générale .....                                               | 14  |

| 1.2    Contexte et revue bibliographique .....                                   | 14  |

| 1.3    Problématique.....                                                        | 16  |

| 1.4    Objectifs et méthodologie de recherche .....                              | 19  |

| CHAPITRE 2 .....                                                                 | 22  |

| Algorithme et plateforme utilisé .....                                           | 22  |

| 2.1    Introduction et schématisation de l'algorithme .....                      | 23  |

| 2.1.1    Contrôle vectoriel.....                                                 | 23  |

| 2.1.2    Survol du portillonnage (délais d'activation et temps de maintien)..... | 24  |

| 2.1.3    Lecture de vitesse provenant d'un encodeur optique.....                 | 27  |

| 2.2    Référence Matlab de l'algorithme .....                                    | 28  |

| 2.2.1    Contrôle Vectoriel .....                                                | 29  |

| 2.2.2    Portillonnage (délai d'activation et temps de maintien) .....           | 30  |

| 2.2.3    Moteur et électronique de puissance .....                               | 30  |

| 2.3    Collecte des données de la référence .....                                | 32  |

| 2.4    Platerforme Amirix.....                                                   | 36  |

| CHAPITRE 3 .....                                                                 | 37  |

| Modèle System Generator .....                                                    | 37  |

|                                                          |                                                                           |    |

|----------------------------------------------------------|---------------------------------------------------------------------------|----|

| 3.1                                                      | Brève description .....                                                   | 38 |

| 3.2                                                      | Méthode de développement .....                                            | 38 |

| 3.2.1                                                    | Développement de bloc individuel et validation de premier niveau.....     | 39 |

| 3.2.2                                                    | Développement d'ensemble, liaisons et validation de deuxième niveau ..... | 45 |

| 3.3                                                      | Contrôle vectoriel.....                                                   | 46 |

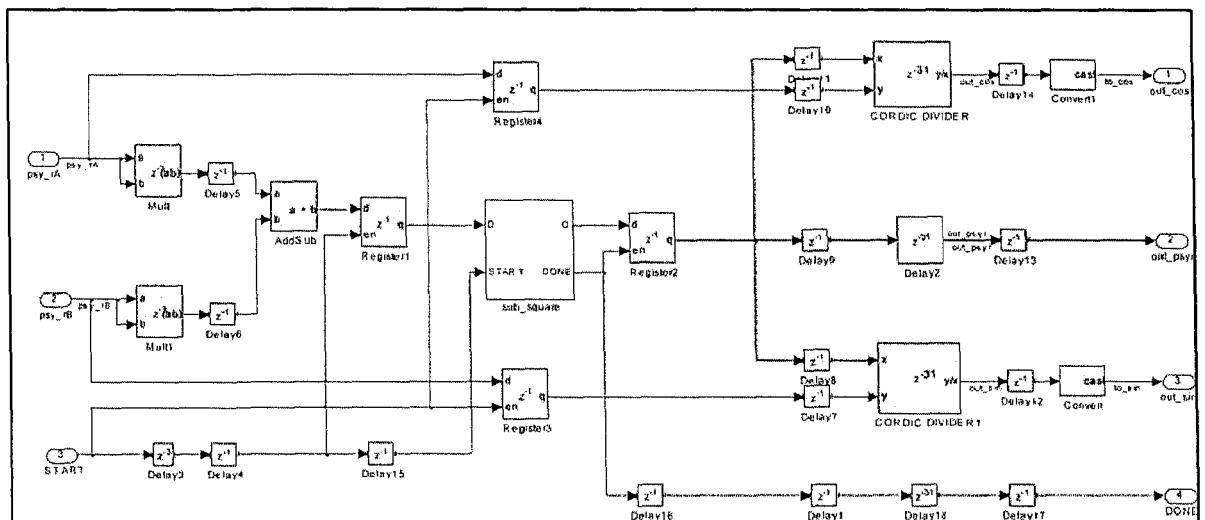

| 3.4                                                      | Division et Racine carrée.....                                            | 48 |

| 3.5                                                      | Portillonnage (délai d'activation et temps de maintien) .....             | 49 |

| 3.6                                                      | Lecture de vitesse provenant d'un encodeur optique .....                  | 54 |

| CHAPITRE 4 .....                                         |                                                                           | 55 |

| Le rôle de GAPPY et des outils de vérification XSG ..... |                                                                           | 55 |

| 4.1                                                      | Introduction à GAPPY .....                                                | 56 |

| 4.2                                                      | Premier niveau – Pre-XSG .....                                            | 56 |

| 4.2.1                                                    | Scripts.....                                                              | 56 |

| 4.2.2                                                    | Migration vers Matlab/XSG.....                                            | 58 |

| 4.3                                                      | Deuxième Niveau – Post-XSG.....                                           | 62 |

| 4.3.1                                                    | Optimisation de bloc individuel .....                                     | 62 |

| 4.3.2                                                    | Validation de premier niveau et de deuxième niveau .....                  | 63 |

| 4.4                                                      | Analyse temporelle (Outil XSG).....                                       | 64 |

| 4.4.1                                                    | Analyse de bloc individuel.....                                           | 66 |

| 4.4.2                                                    | Analyse d'ensemble .....                                                  | 68 |

| 4.5                                                      | Comparaison à AccelDSP .....                                              | 69 |

| 4.6                                                      | Introduction à la co-simulation (XSG) .....                               | 69 |

| 4.7                                                      | Co-simulation de modèles avec attente .....                               | 70 |

| 4.8                                                      | Test sur matériel .....                                                   | 73 |

| 4.9                                                      | FPGA-in-the-loop; co-simulation avec SimPowerSystems .....                | 74 |

|                                                                          |           |

|--------------------------------------------------------------------------|-----------|

| 4.10 Résultats de profils simulés.....                                   | 77        |

| <b>CHAPITRE 5.....</b>                                                   | <b>81</b> |

| Résumé de la méthode, travaux futurs et conclusion .....                 | 81        |

| 5.1 Schématisation de l'algorithme .....                                 | 82        |

| 5.2 Référence Matlab et collecte de données .....                        | 82        |

| 5.3 Création des scripts GAPP (Pre-XSG) en pire cas possible (PCP) ..... | 82        |

| 5.4 Création du fichier d'initialisation Matlab .....                    | 82        |

| 5.5 Création du modèle System Generator .....                            | 82        |

| 5.6 Optimisation avec GAPP (Post-XSG) .....                              | 82        |

| 5.7 Co-simulation en boucle fermée (FPGA-in-the-loop) .....              | 82        |

| 5.8 Instanciation du projet XSG sur la plateforme Amirix.....            | 82        |

| 5.9 Travaux futurs et ajouts intéressants à la méthode .....             | 83        |

| 5.10 Possibilités futures et applications.....                           | 84        |

| 5.11 Conclusion .....                                                    | 85        |

| Bibliographie .....                                                      | 87        |

| Annexe A .....                                                           | 90        |

| Équations du contrôle vectoriel .....                                    | 90        |

| Annexe B.....                                                            | 94        |

| Plateforme Amirix .....                                                  | 94        |

| 6.1 Connectivité .....                                                   | 95        |

| 6.1.1 AIO.....                                                           | 95        |

| 6.1.2 FPGA.....                                                          | 96        |

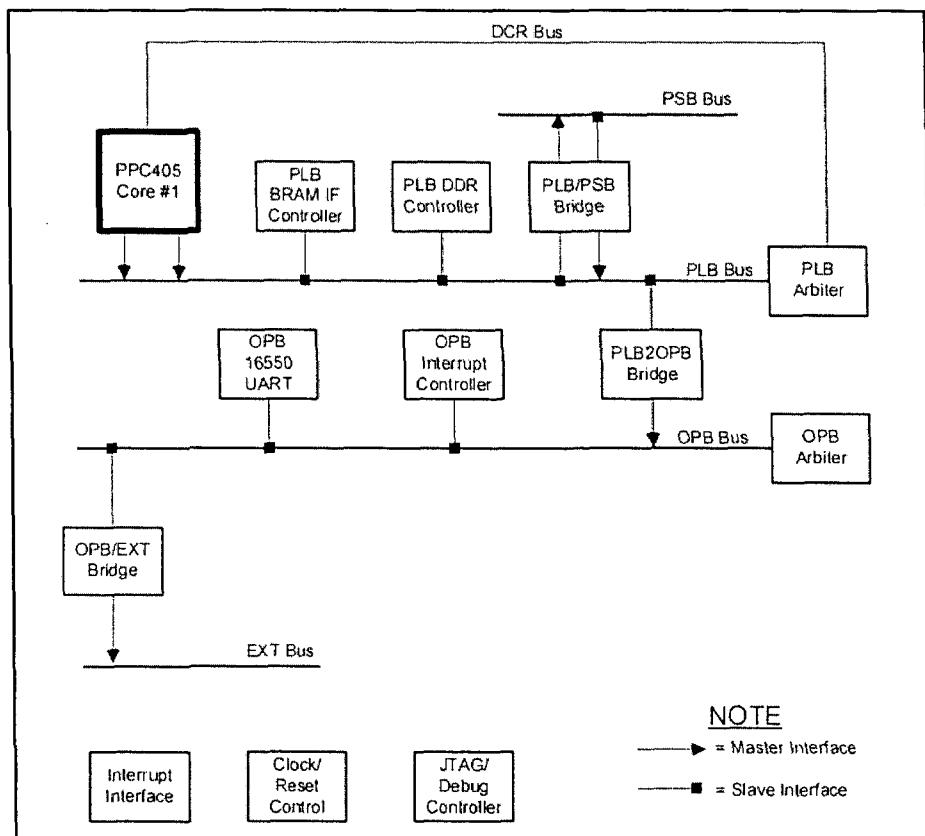

| 6.2 Logique matérielle .....                                             | 97        |

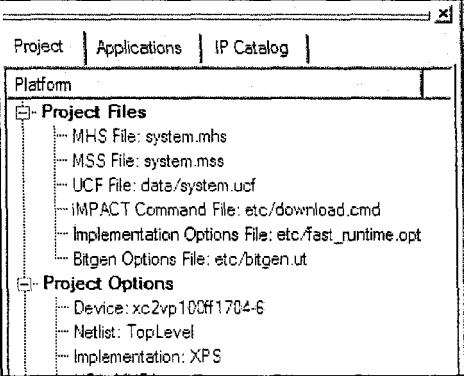

| 6.2.1 Le Project Xilinx Platform Studio (XPS) .....                      | 97        |

| 6.2.2 Software / User Logic interaction .....                            | 100       |

| 6.2.3 Le modèle esclave de lecture des registres .....                   | 101       |

|                                                   |                                                            |     |

|---------------------------------------------------|------------------------------------------------------------|-----|

| 6.2.4                                             | La machine d'état.....                                     | 102 |

| 6.2.5                                             | Intégration de fichiers NGC.....                           | 104 |

| 6.2.6                                             | Génération de fichier BIN et configuration sur Amirix..... | 105 |

| 6.3                                               | Logiciel et pilotes.....                                   | 106 |

| 6.3.1                                             | Opérations de préparation logicielle .....                 | 106 |

| Annexe C.....                                     |                                                            | 107 |

| Code Embedded du portillonnage .....              |                                                            | 107 |

| Annexe D .....                                    |                                                            | 110 |

| Script Autohotkey pour Amirix.....                |                                                            | 110 |

| Annexe E .....                                    |                                                            | 114 |

| Blocs individuels du contrôle vectoriel XSG ..... |                                                            | 114 |

| Annexe F .....                                    |                                                            | 124 |

| Schémas de racine carrée et division .....        |                                                            | 124 |

| Annexe G .....                                    |                                                            | 126 |

| Scripts GAPPA .....                               |                                                            | 126 |

| # Optimisation de Clark.....                      |                                                            | 127 |

| # Optimisation de current_pi .....                |                                                            | 128 |

| # Optimisation de decoupling 1 .....              |                                                            | 129 |

| # Optimisation de decoupling 2 .....              |                                                            | 130 |

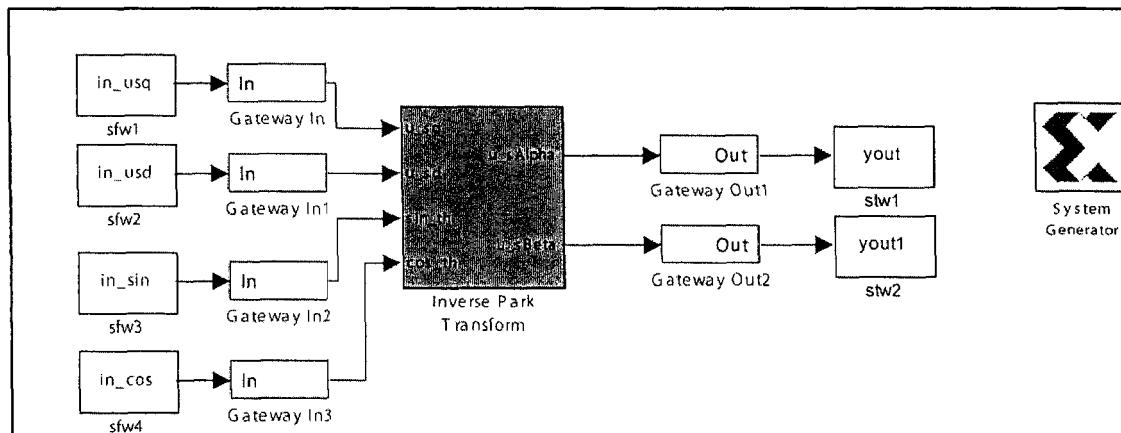

| # Optimisation de Inverse de Park .....           |                                                            | 131 |

| # Optimisation de Park Transform .....            |                                                            | 132 |

| # Optimisation de psy_sB .....                    |                                                            | 133 |

| # Optimisation de psy_SA.....                     |                                                            | 134 |

| # Optimisation de psy_RB .....                    |                                                            | 135 |

| # Optimisation de psy_RA .....                    |                                                            | 136 |

| # Optimisation de fluxpi .....                    |                                                            | 137 |

| # Optimisation de w_est .....                     |                                                            | 138 |

|                                         |     |

|-----------------------------------------|-----|

| # Optimisation de Speed_pi .....        | 138 |

| # Optimisation de rotor1.....           | 139 |

| Annexe H .....                          | 142 |

| Module de puissance et Moteur SPS ..... | 142 |

| Annexe I.....                           | 144 |

| Articles acceptés.....                  | 144 |

## Table des figures

|                                                                                              |    |

|----------------------------------------------------------------------------------------------|----|

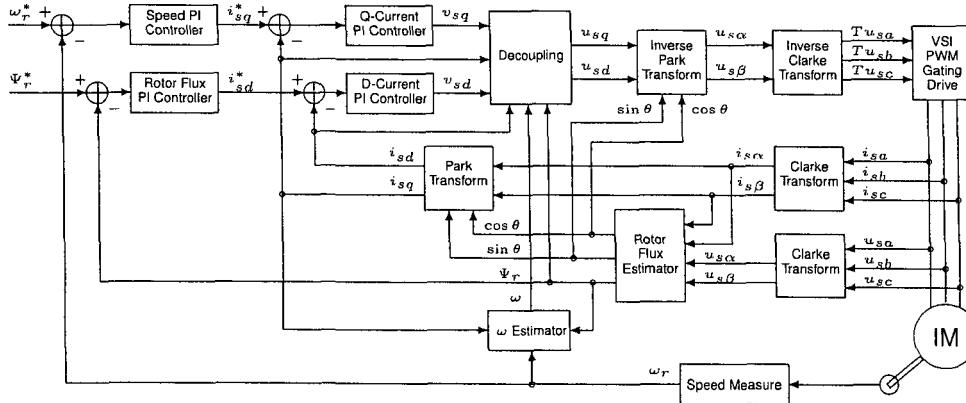

| figure 1 - Contrôle vectoriel .....                                                          | 24 |

| figure 2 - Portillonnage PWM asymétrique.....                                                | 26 |

| figure 3 - Fils de l'encodeur optique.....                                                   | 27 |

| figure 4 - Interface du contrôle Simulink (référence).....                                   | 29 |

| figure 5 - Calcul des délais d'activation et portillonnage (embedded Matlab functions) ..... | 30 |

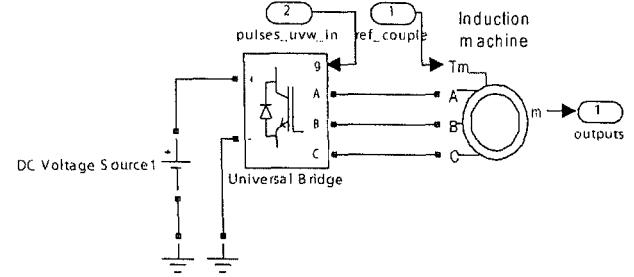

| figure 6 - Module de puissance et moteur à induction (SPS).....                              | 31 |

| figure 7 - Collecte des données de référence (Contrôle Simulink) .....                       | 34 |

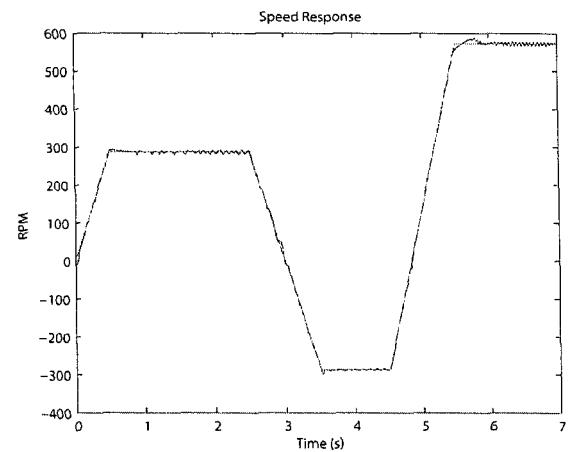

| figure 8 - Collecte des données de référence (réponse du moteur).....                        | 35 |

| figure 9 - méthode simultanée (bloc individuel) .....                                        | 42 |

| figure 10 - méthode de la sainte croyance.....                                               | 43 |

| figure 11 - Estimateur de flux rotorique (bloc complexe).....                                | 45 |

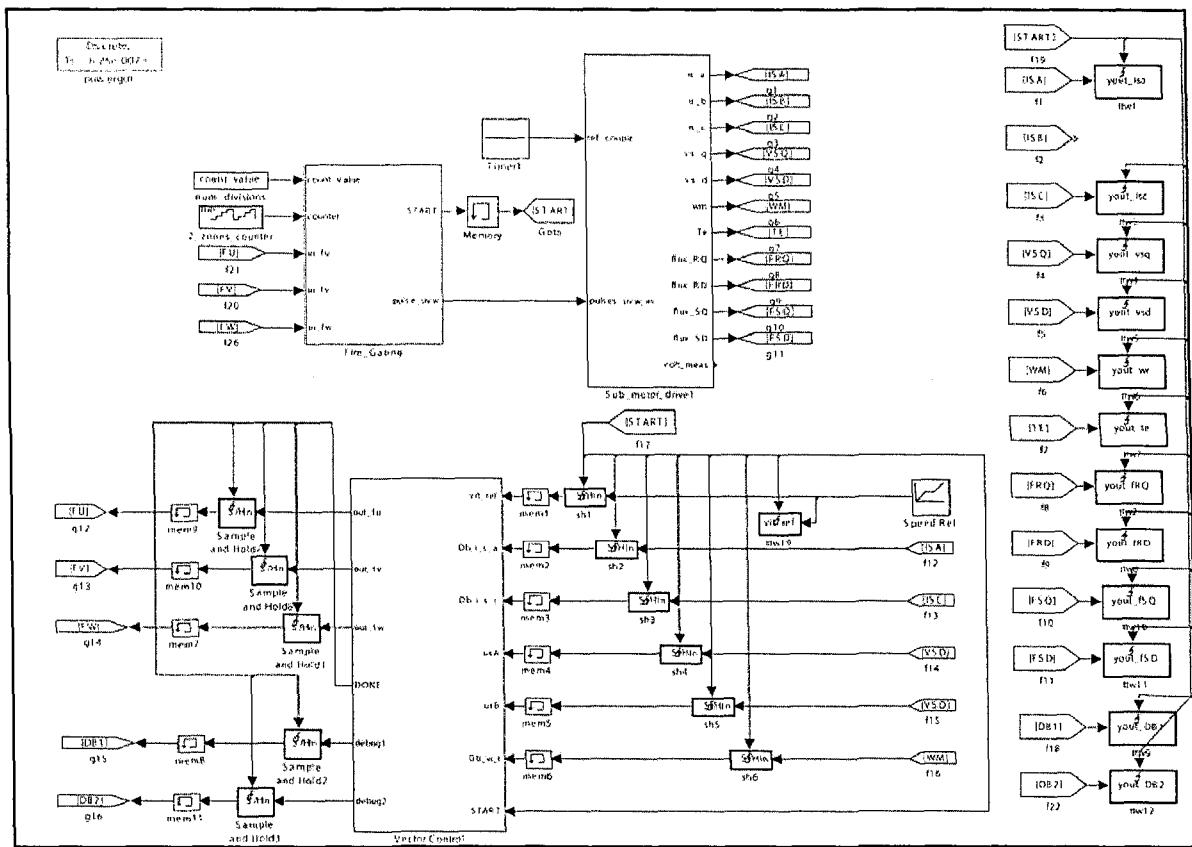

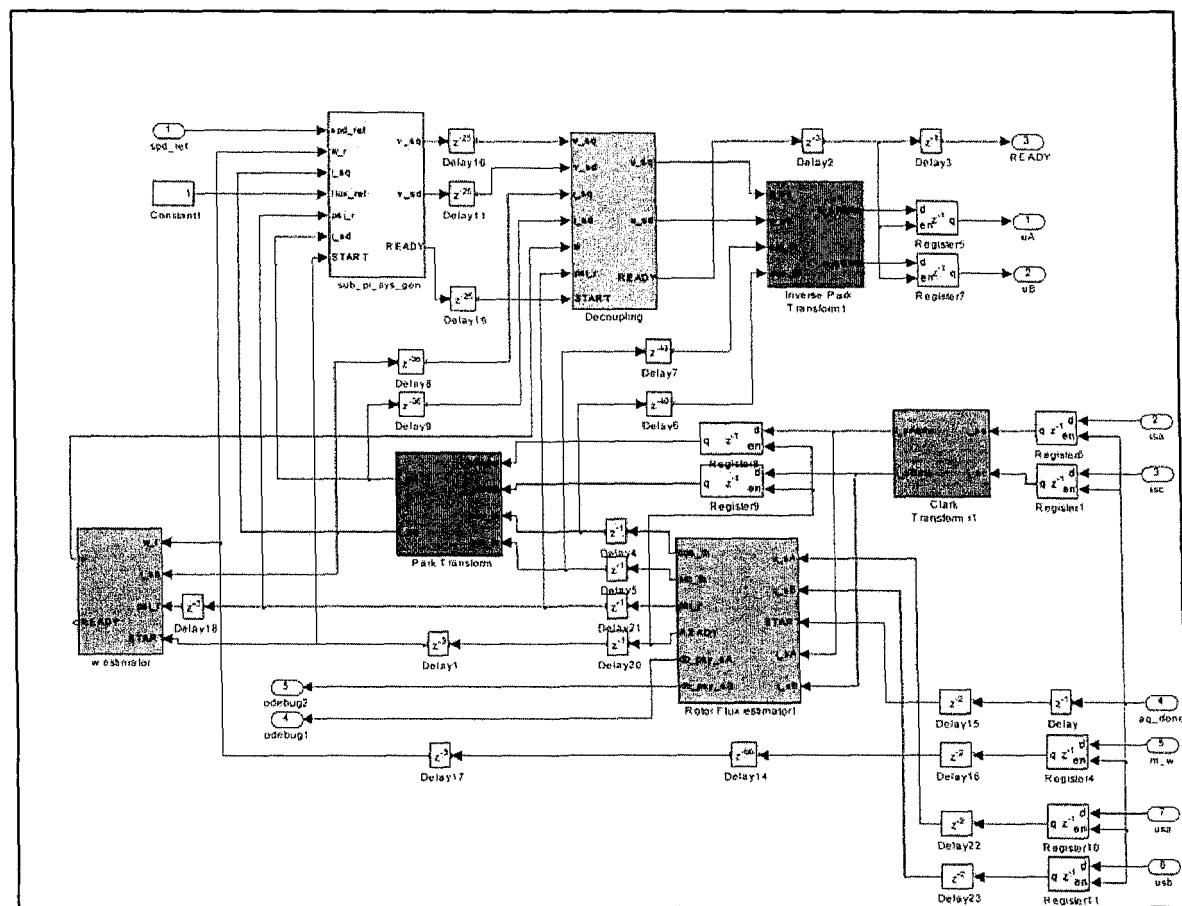

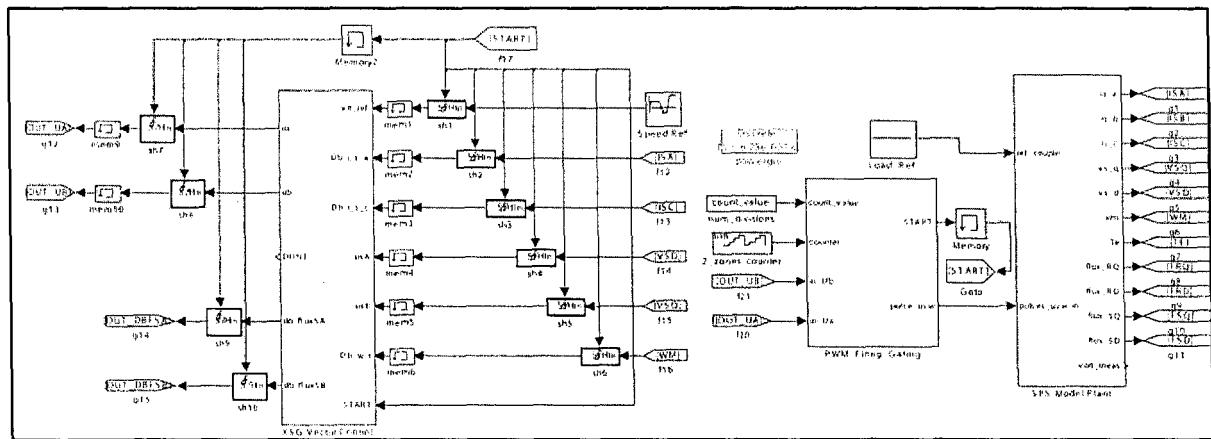

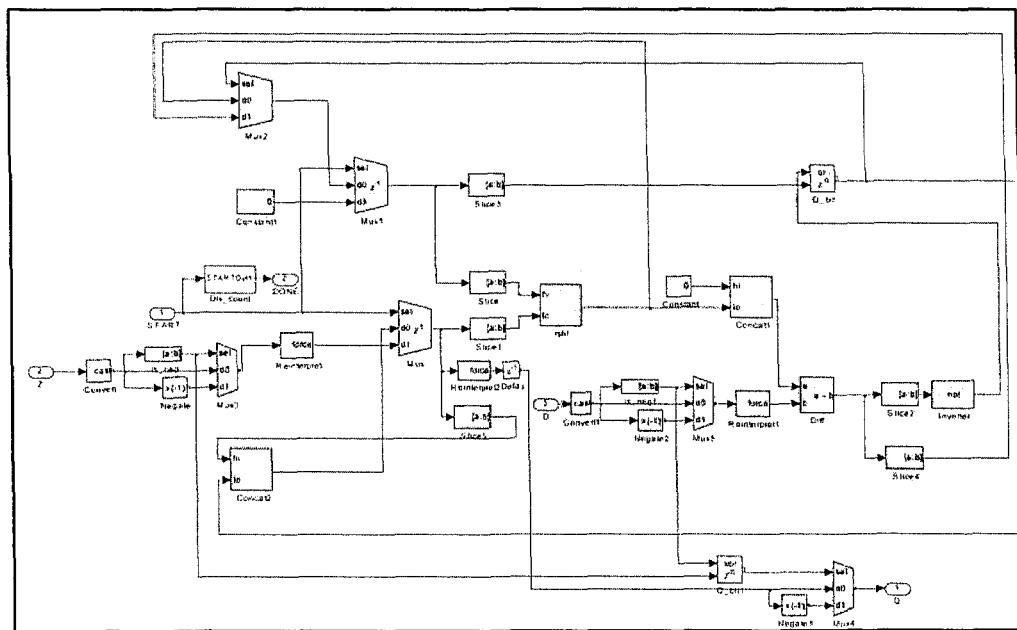

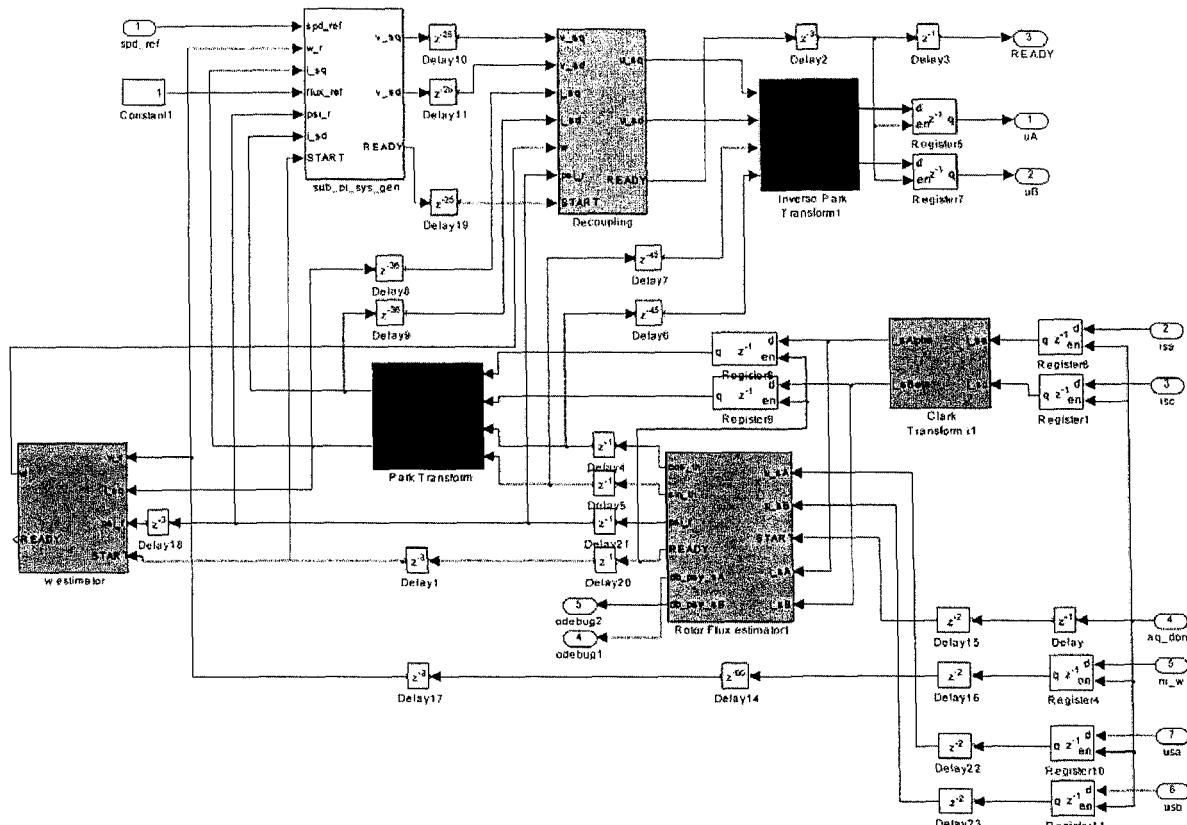

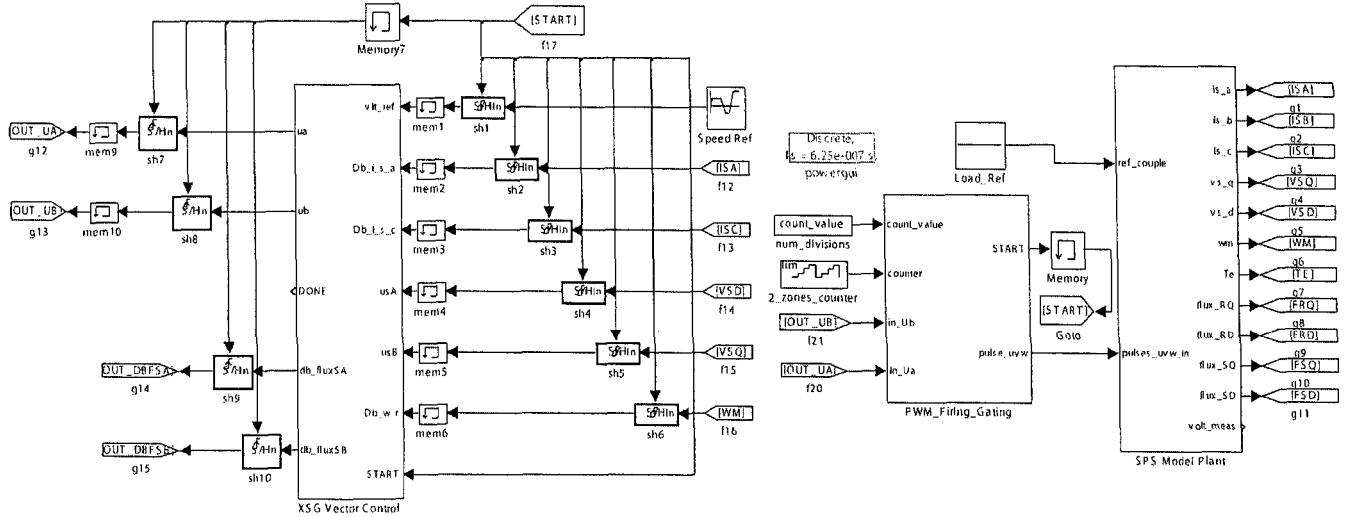

| figure 12 - Contrôle vectoriel complet XSG .....                                             | 46 |

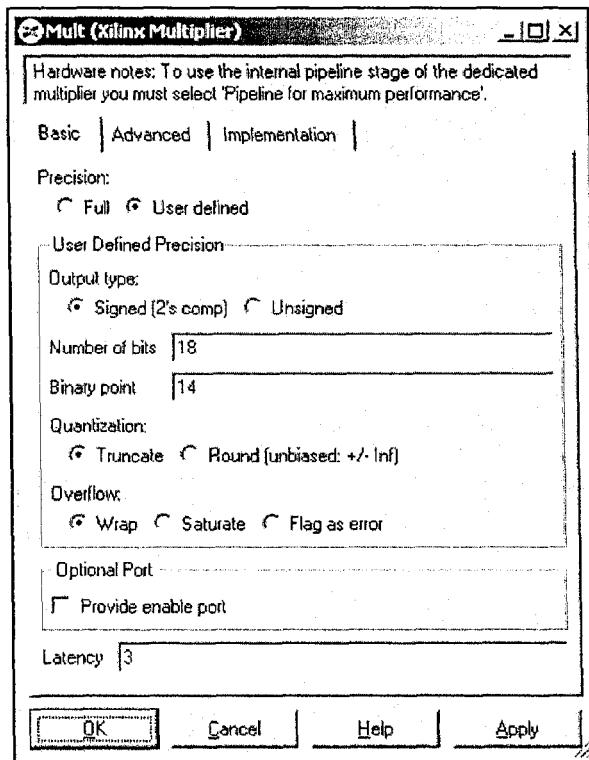

| figure 13 - propriétés d'un bloc XSG .....                                                   | 47 |

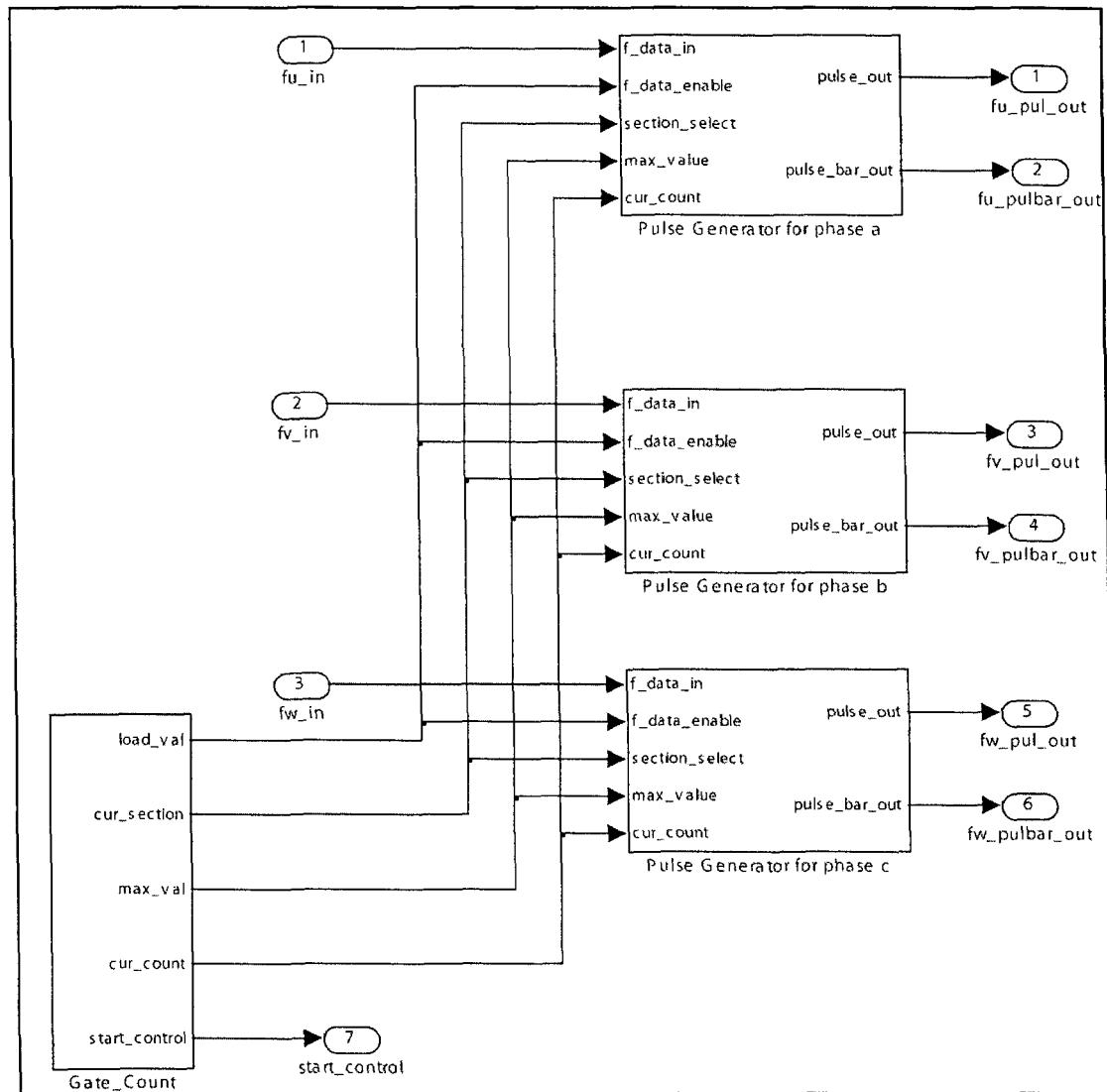

| figure 14 - Portillonnage.....                                                               | 50 |

| figure 15 - Calcul des délais d'activation .....                                             | 51 |

| figure 16 - Calcul du temps mort.....                                                        | 51 |

| figure 17 - Courants, vitesse et torque du moteur avec simulation du portillonnage XSG ..... | 52 |

| figure 18 - Courants, vitesse et torque du moteur avec simulation du portillonnage XSG ..... | 53 |

| figure 19 - Lecture de vitesse d'un encodeur optique (modèle simple) .....                   | 54 |

| figure 20 - Résultat de l'exécution GAPP.....                                                | 60 |

| figure 21 - Précision variable dans un bloc XSG .....                                        | 61 |

| figure 22 - Résultat d'exécution XSG .....                                                   | 61 |

| figure 23 - Analyse temporelle (vitesse maximum).....                                        | 65 |

| figure 24 - Analyse temporelle (détails des délais) .....                                    | 65 |

| figure 25 - Analyse temporelle (identification des délais sur le modèle XSG) .....           | 66 |

| figure 26 - Bloc XSG avant analyse temporelle .....                                          | 67 |

| figure 27 - Bloc XSG après analyse temporelle.....                                           | 67 |

|                                                                                            |     |

|--------------------------------------------------------------------------------------------|-----|

| figure 28 - Simple synchronisation d'un bloc XSG co-simulé .....                           | 72  |

| figure 29 - Carte de co-simulation Xilinx ML402 .....                                      | 73  |

| figure 30 - Co-simulation avec portillonnage, moteur et module de puissance.....           | 74  |

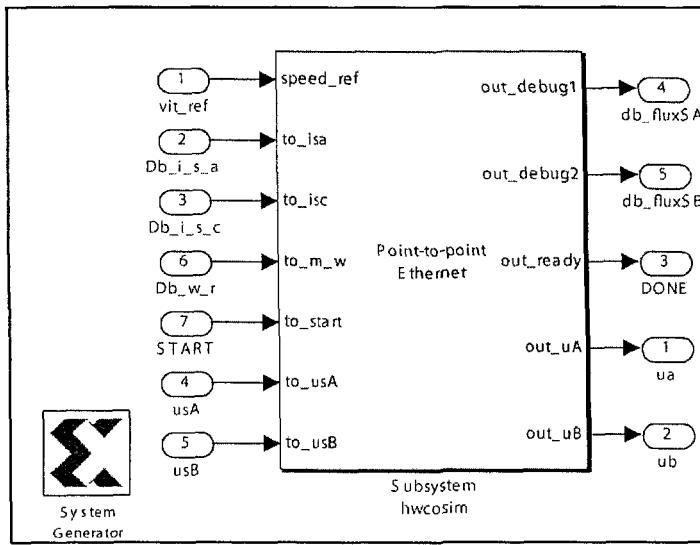

| figure 31 - Interface du bloc XSG co-simulé .....                                          | 75  |

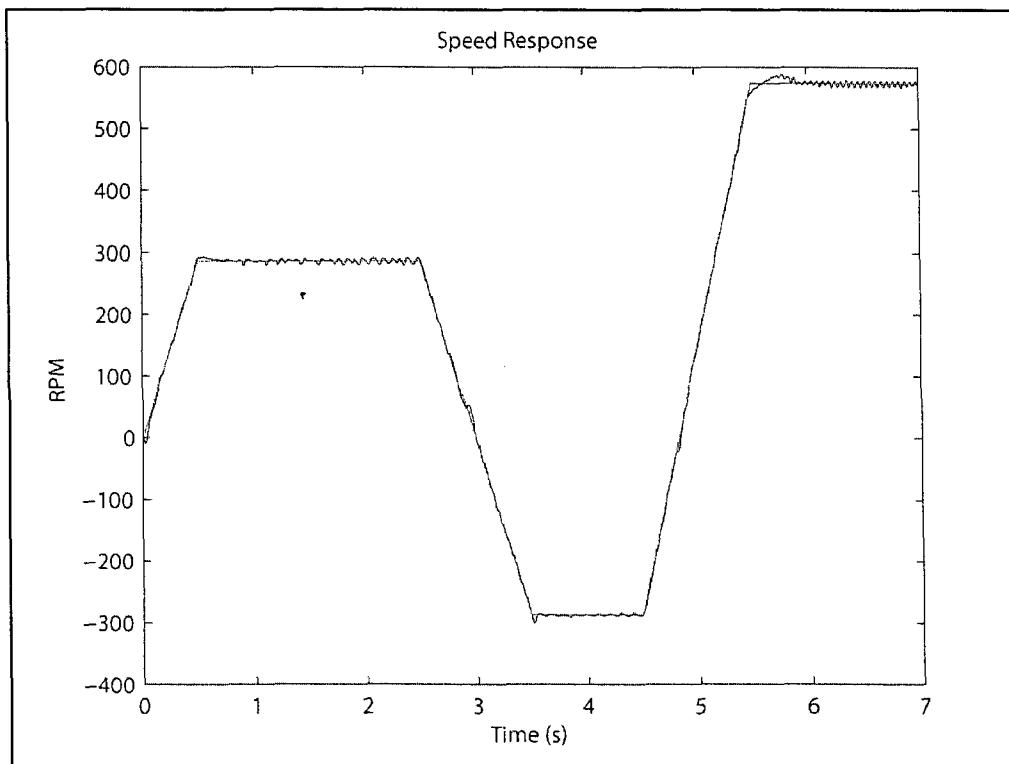

| figure 32 - Réponse du système XSG co-simulé (rouge, lisse = profil, bleu = réponse) ..... | 76  |

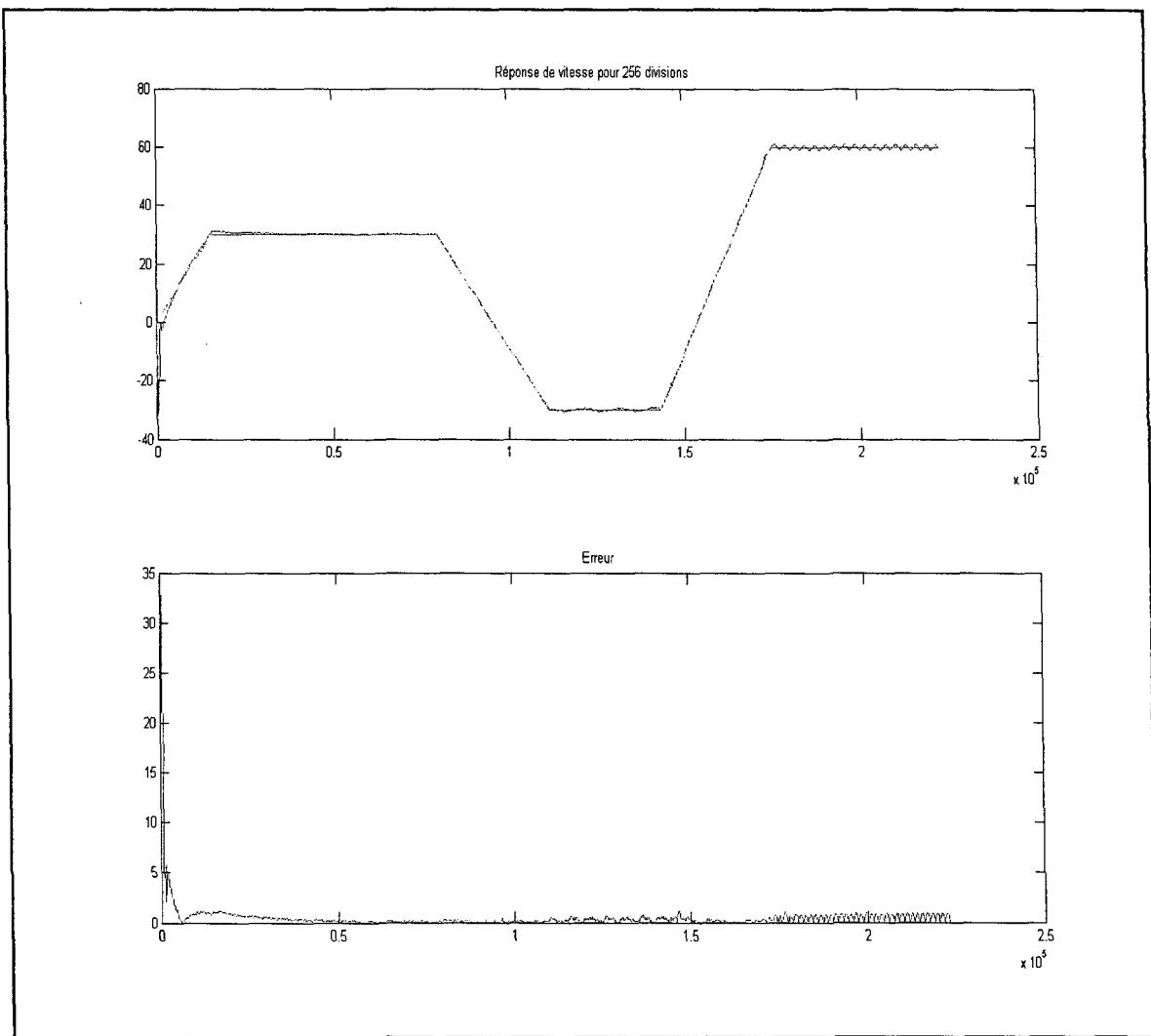

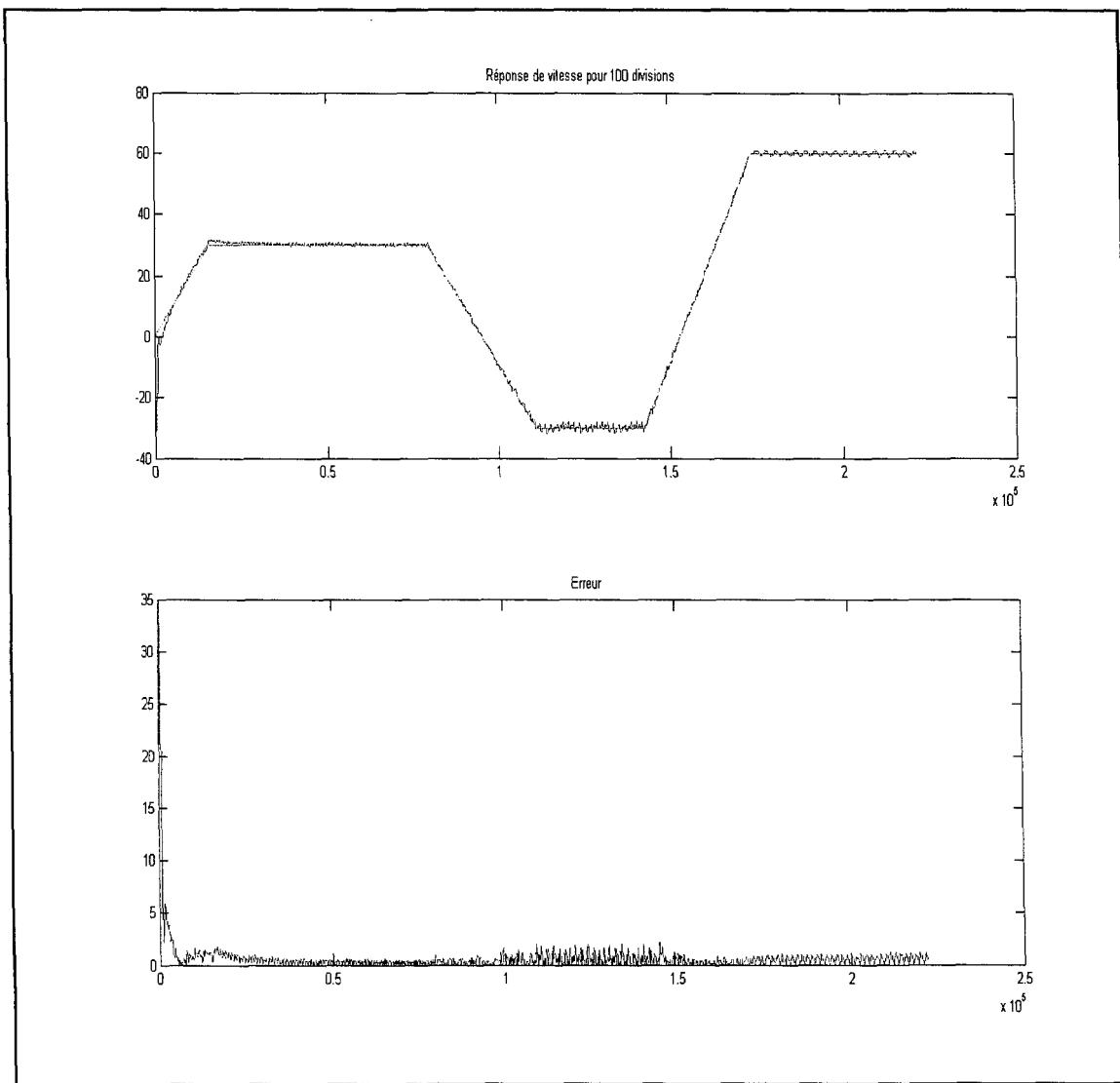

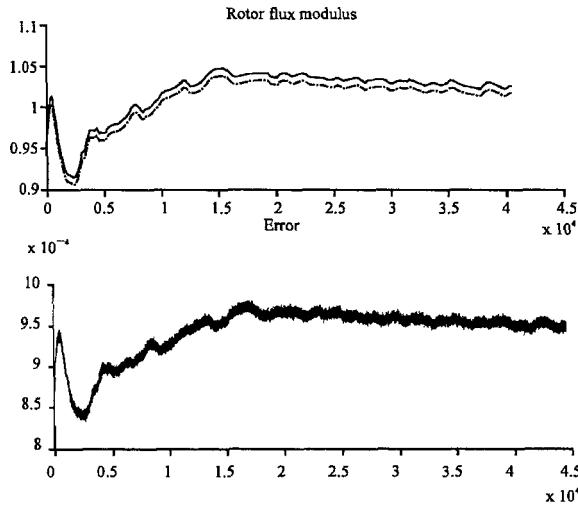

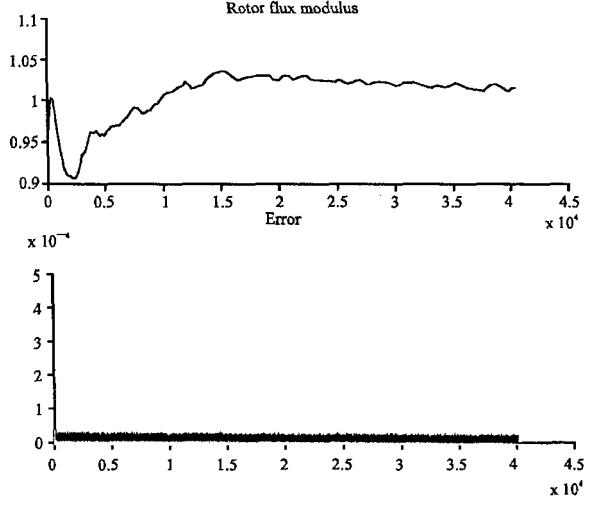

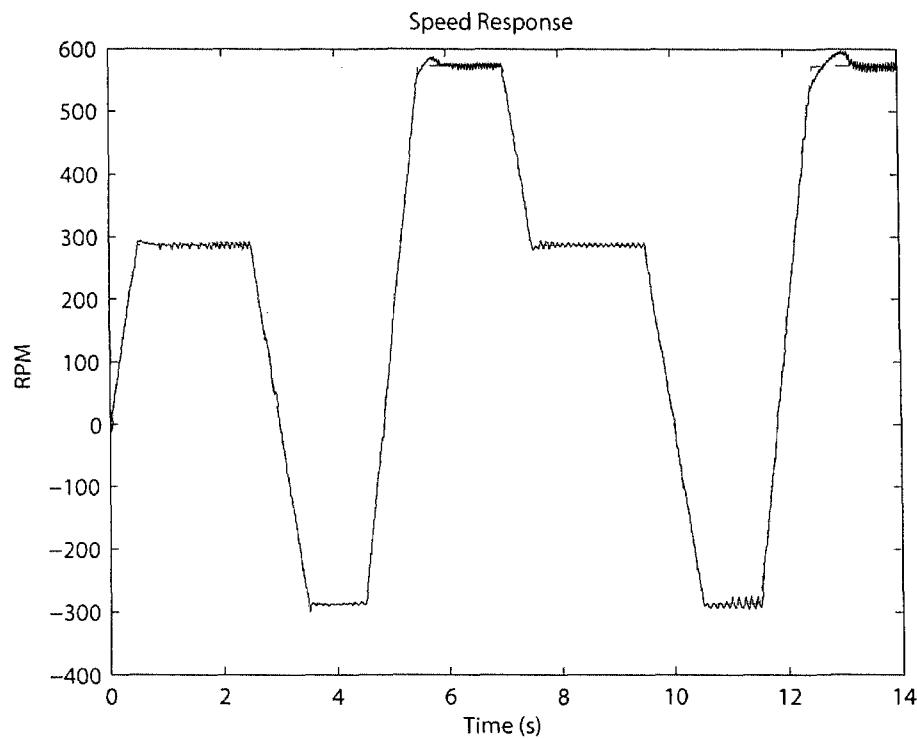

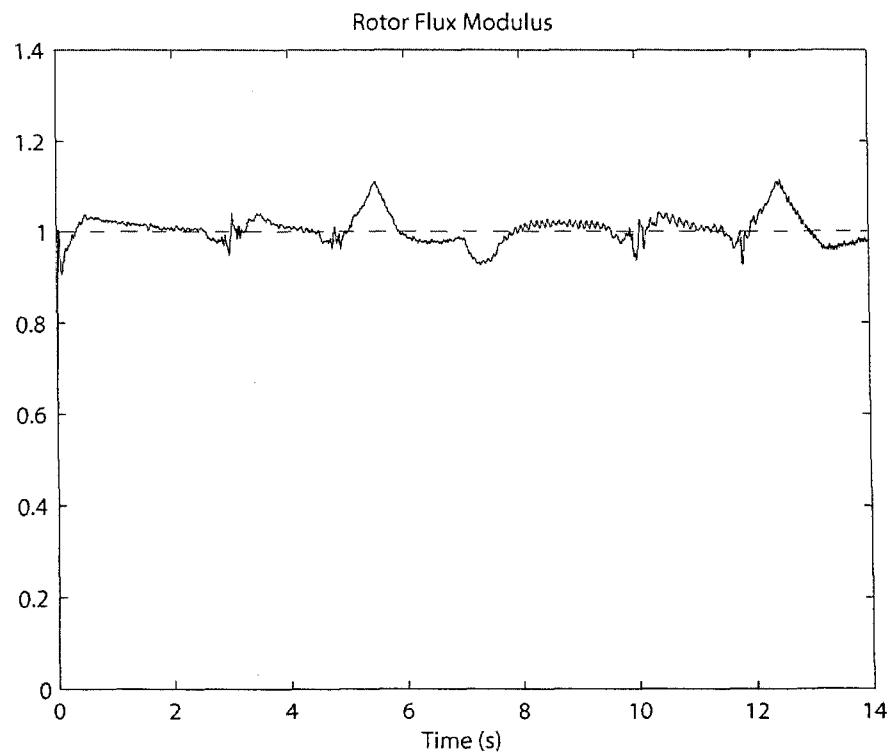

| figure 33 - Réponse de vitesse - 256 divisions - Filtre 5000 Hz .....                      | 78  |

| figure 34 - Réponse de vitesse - 100 divisions - Filtre 5000 Hz .....                      | 79  |

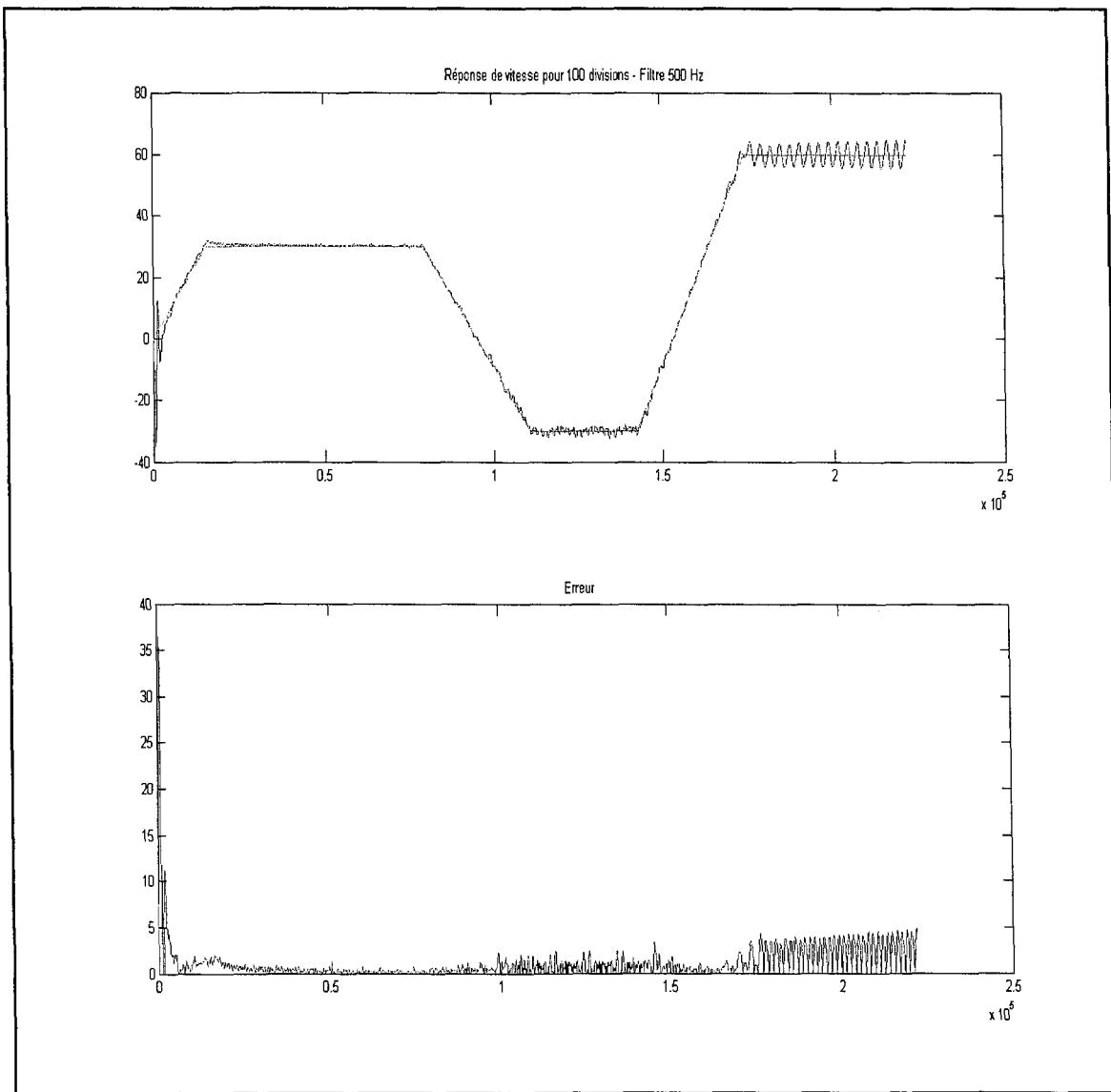

| figure 35 - Réponse de vitesse - 100 divisions - Filtre 500 Hz .....                       | 80  |

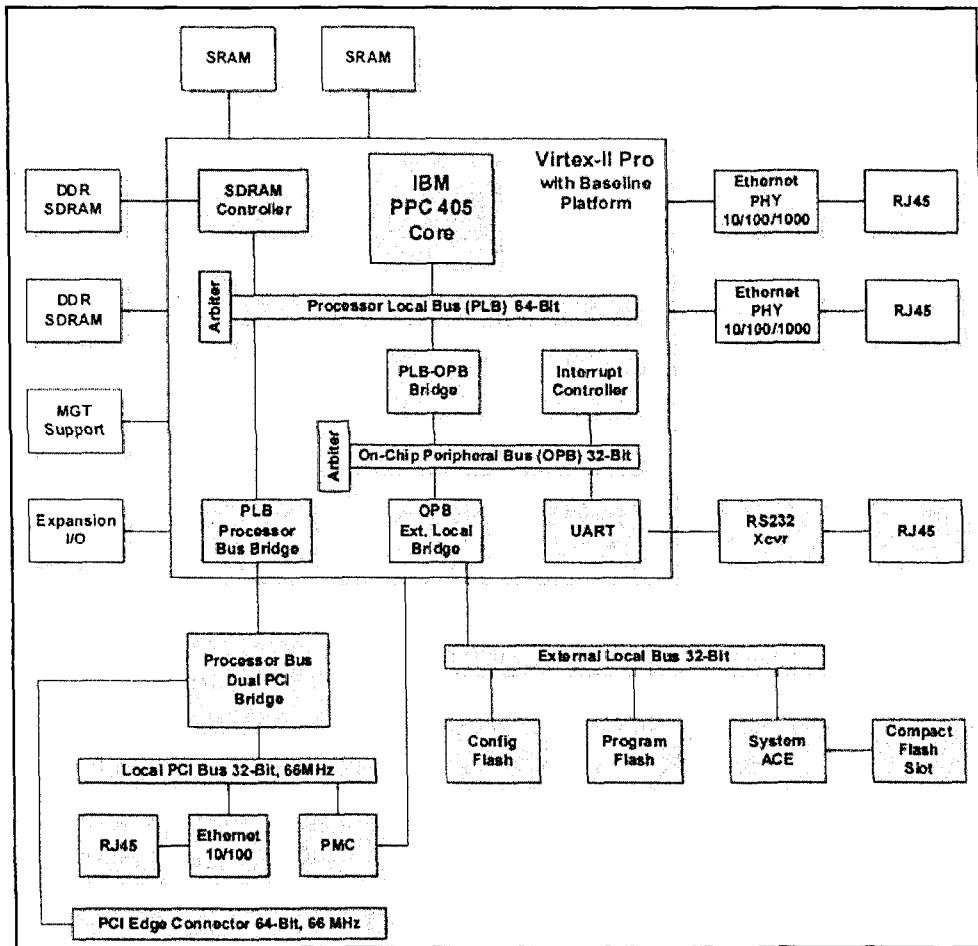

| figure 36 - Plateforme Amirix AP1000.....                                                  | 96  |

| figure 37 - Instance de hw_math dans le Baseline Amirix .....                              | 98  |

| figure 38 - Configuration des bus à l'intérieur du FPGA (AP1000) .....                     | 99  |

| figure 39 - fichier d'options d'implémentation (etc/fast_runtime.opt).....                 | 100 |

| figure 40 – C_BASEADDR+0x0 : Registre de contrôle et statut (CSR) .....                    | 101 |

| figure 41 - MUX du modèle esclave des registres (hw_math) .....                            | 102 |

| figure 42 – Contrôle vectoriel, vue extérieure .....                                       | 115 |

| figure 43 – Contrôle vectoriel, vue intérieure .....                                       | 115 |

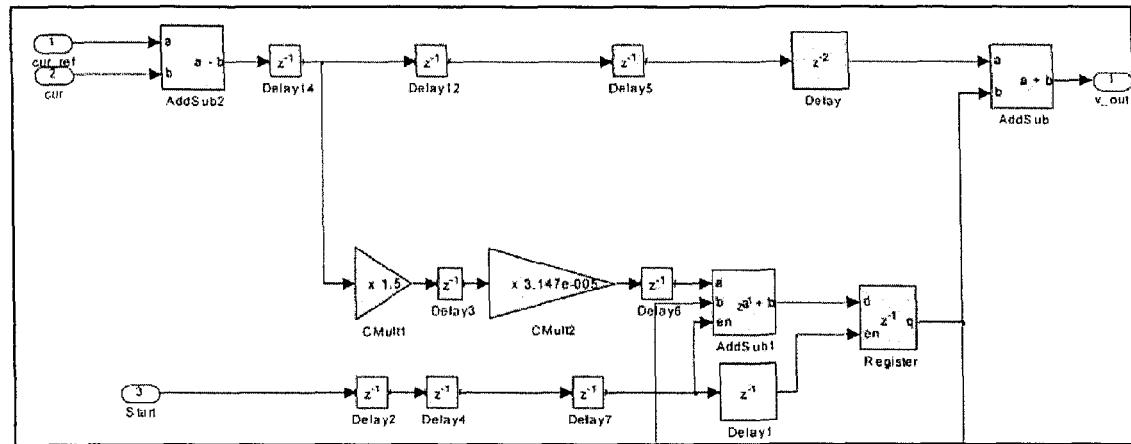

| figure 44 – PI, vue d'ensemble .....                                                       | 116 |

| figure 45 – PI, vue intérieure.....                                                        | 116 |

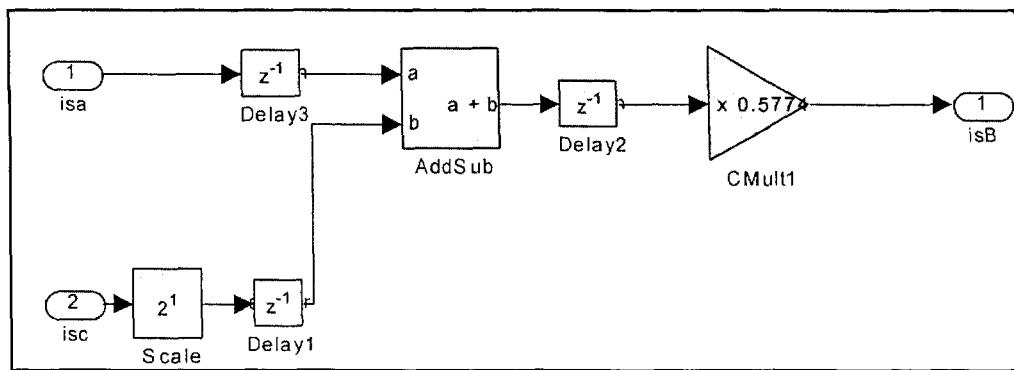

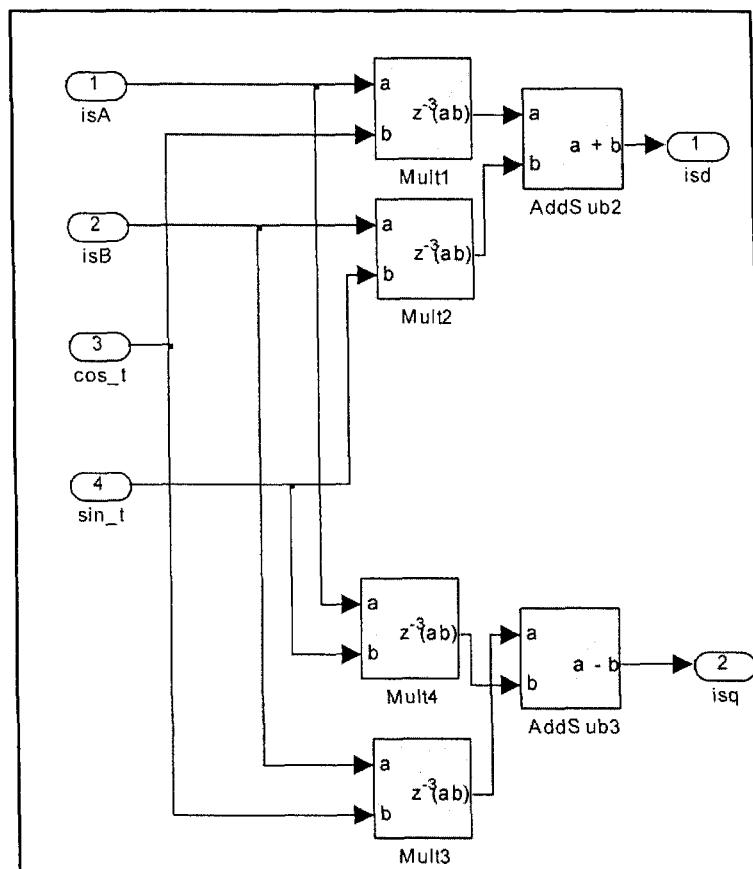

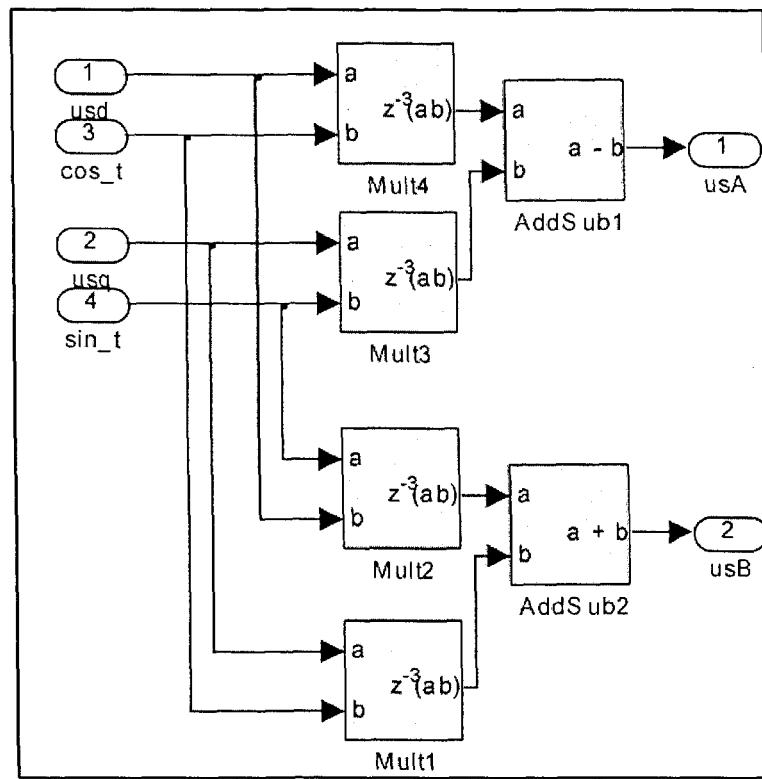

| figure 46 – Transformée de Clark .....                                                     | 117 |

| figure 47 – Transformée de Park.....                                                       | 117 |

| figure 48 – Transformée inverse de Park .....                                              | 118 |

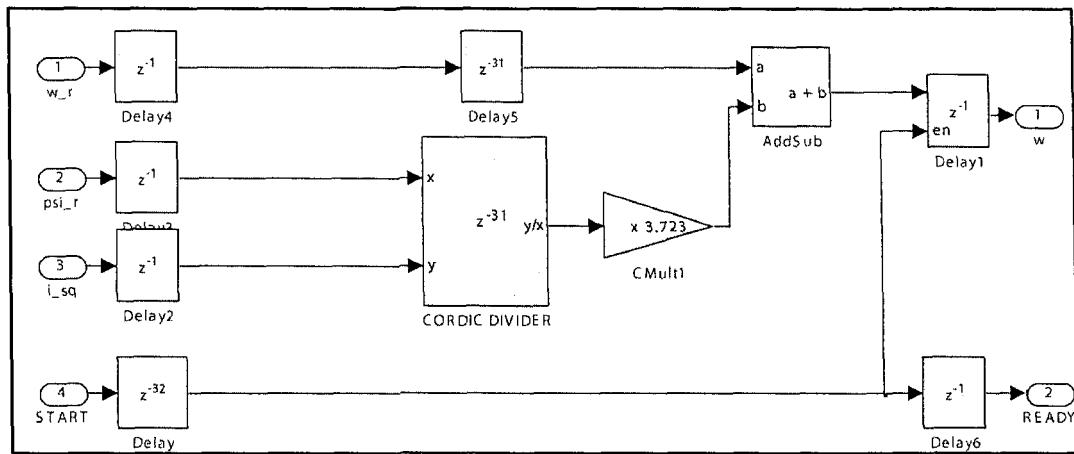

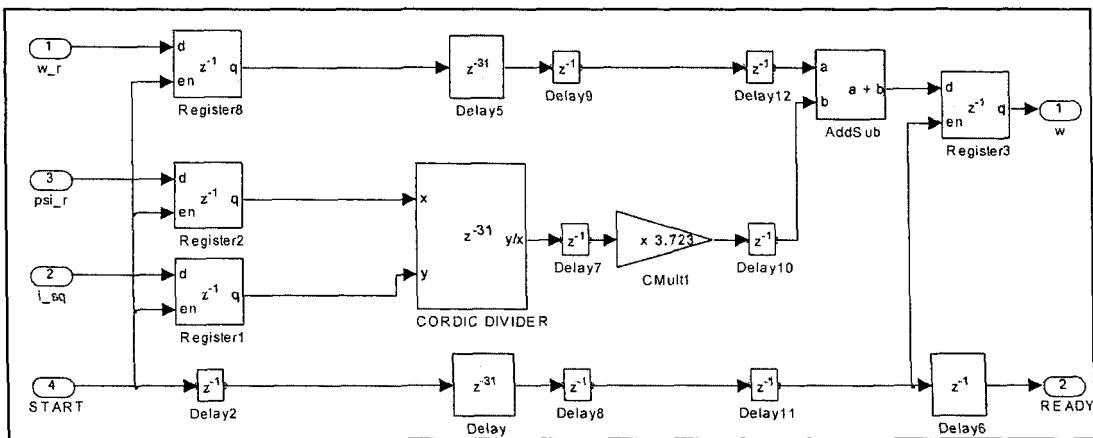

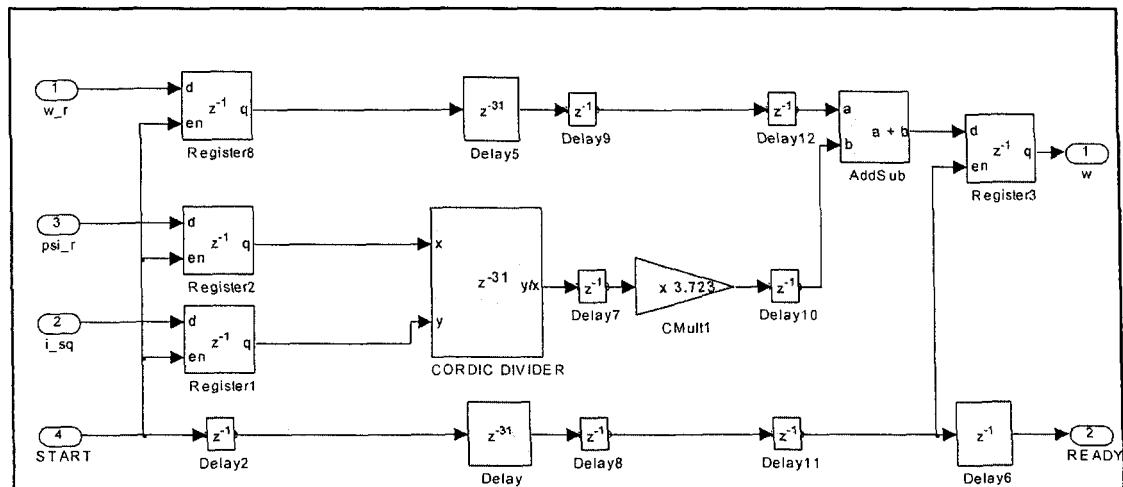

| figure 49 – Estimateur de $\omega$ .....                                                   | 118 |

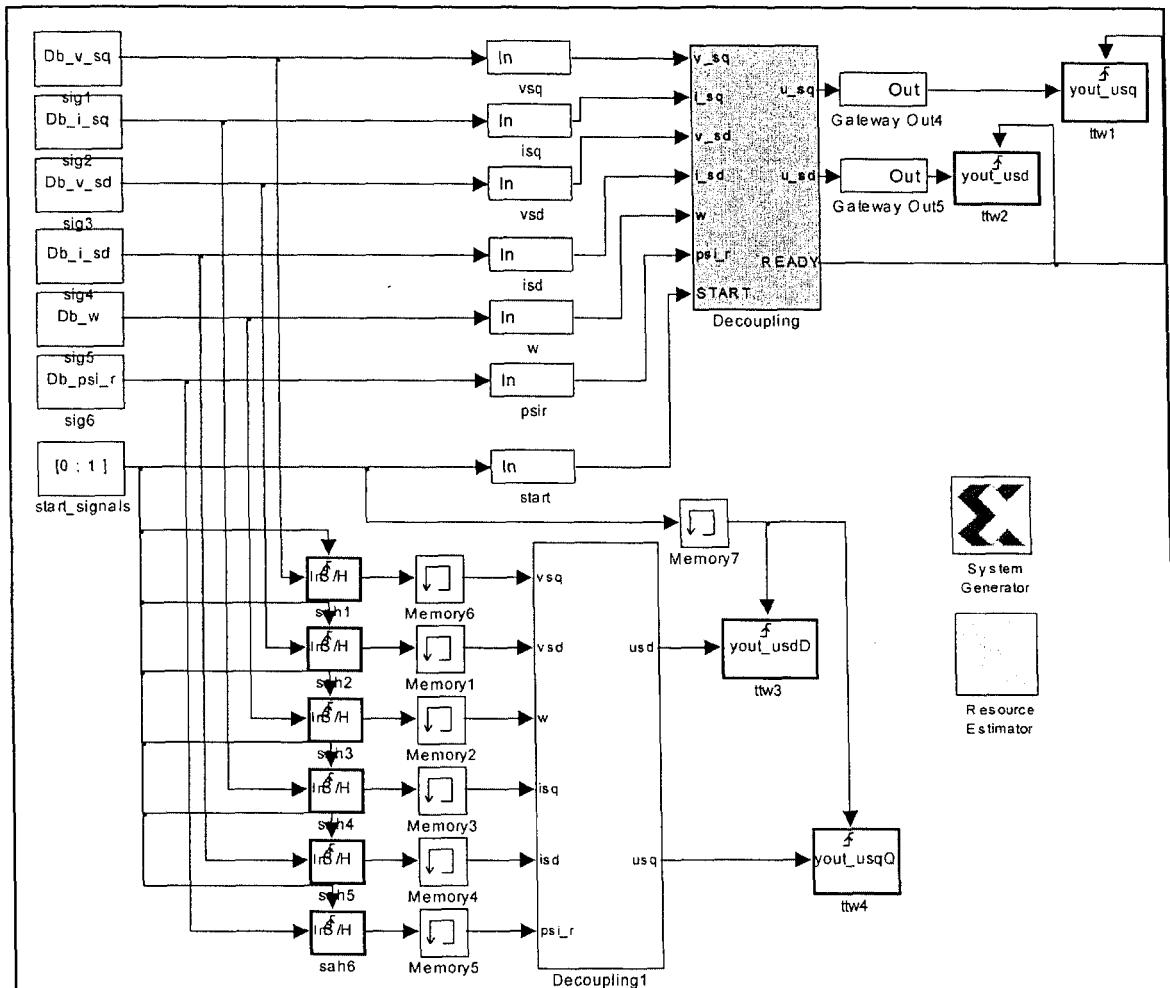

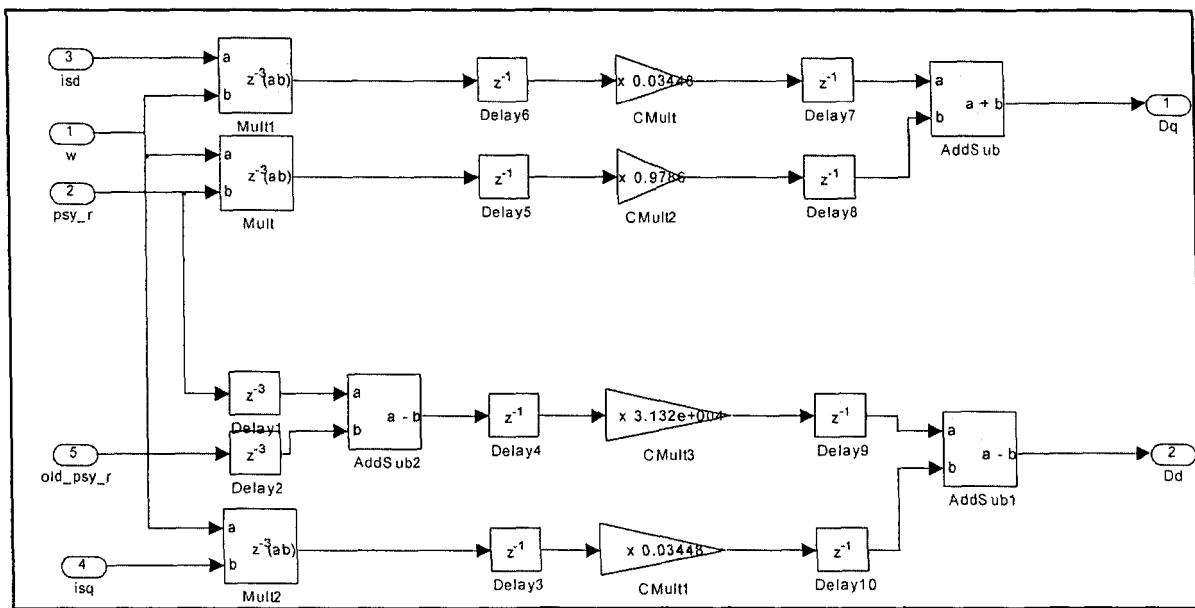

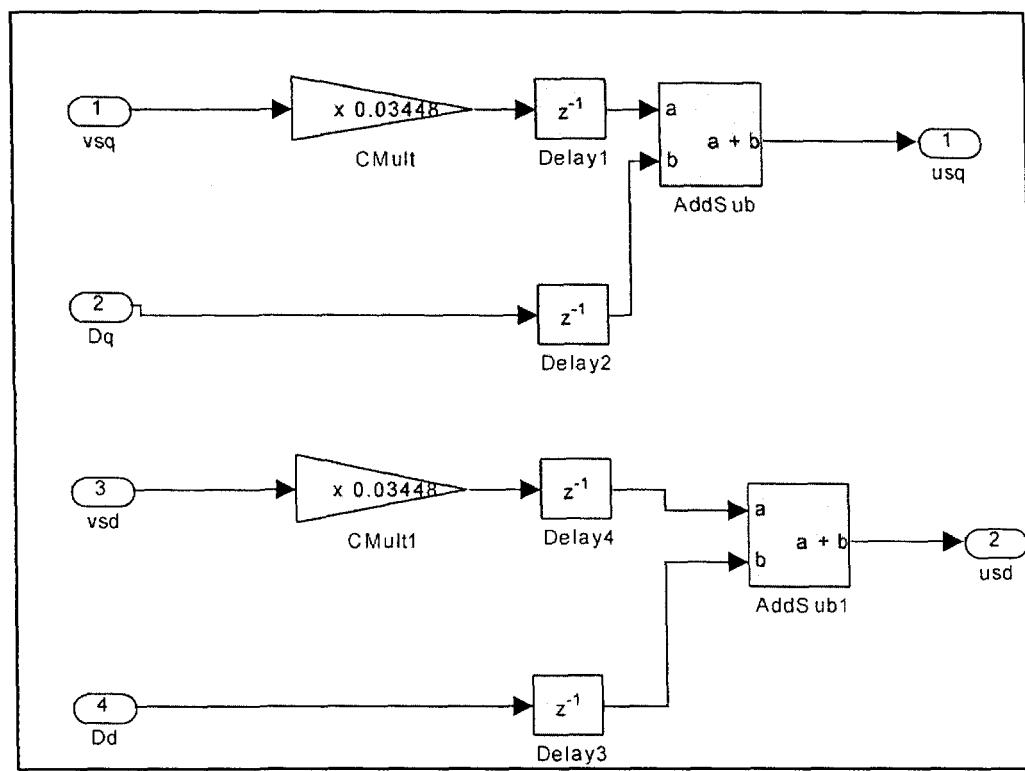

| figure 50 – Bloc decoupling .....                                                          | 119 |

| figure 51 – Calcul de Dq et Dd .....                                                       | 120 |

| figure 52 – Calcul de usq et usd .....                                                     | 121 |

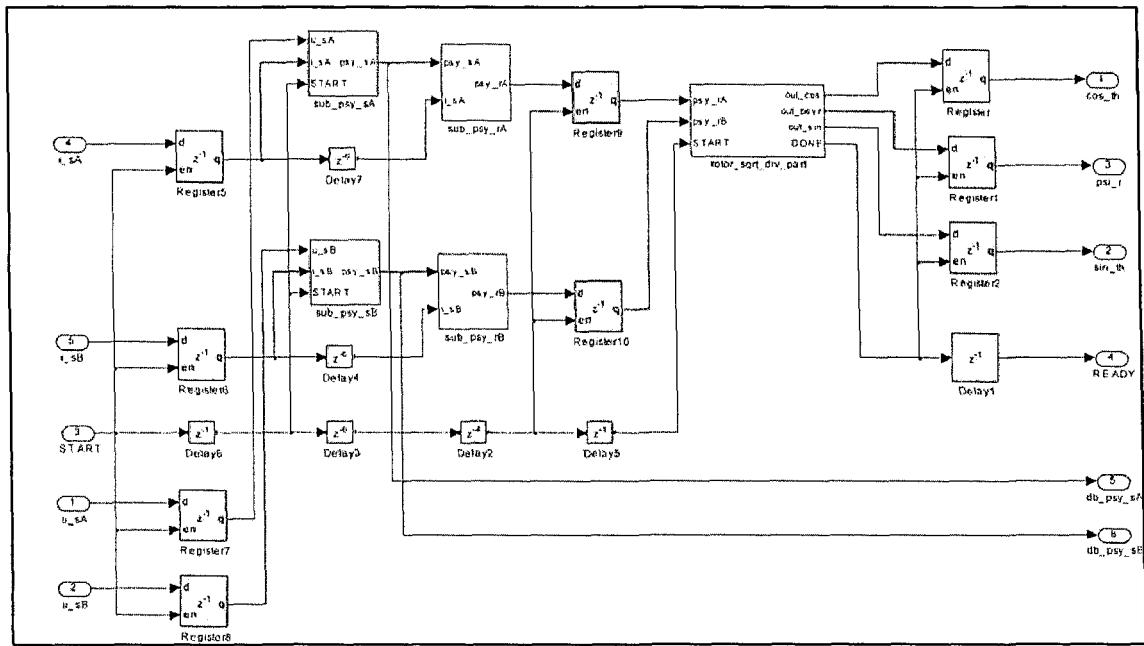

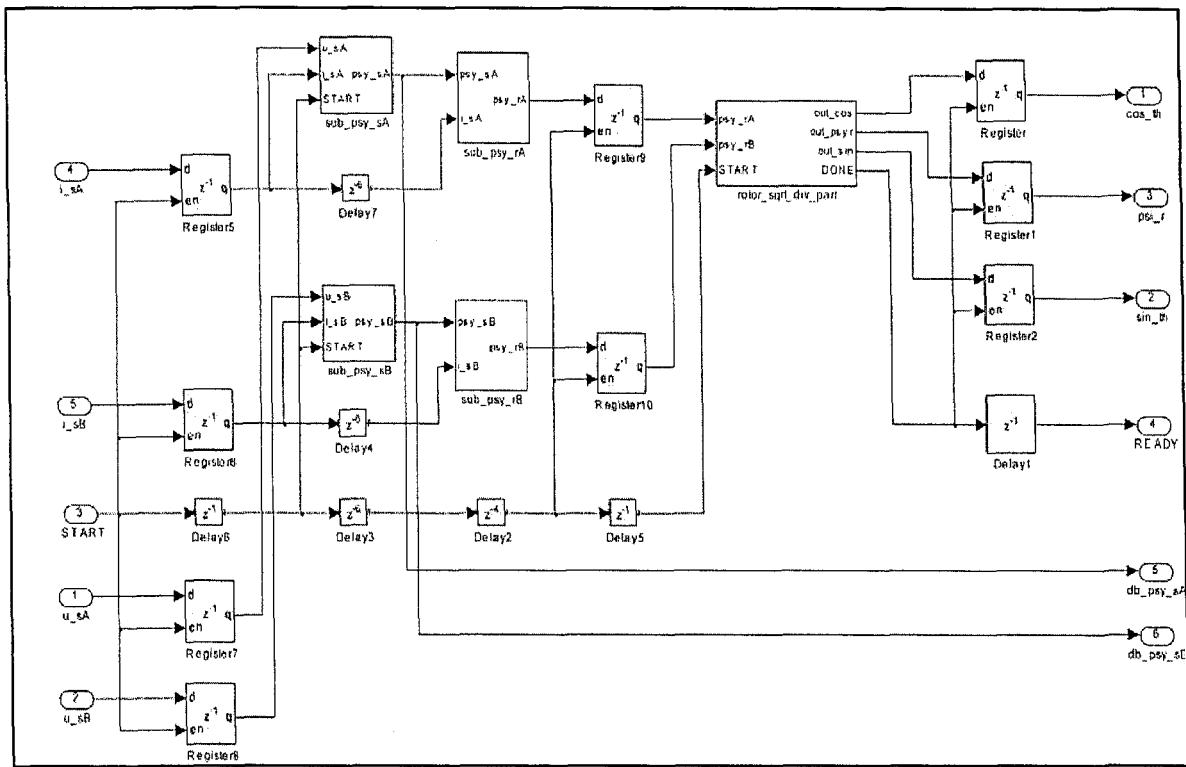

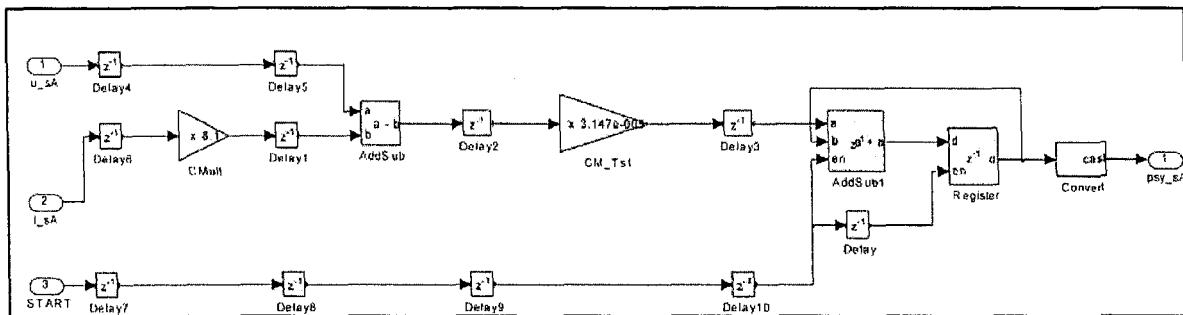

| figure 53 – Estimateur de flux rotoriques .....                                            | 122 |

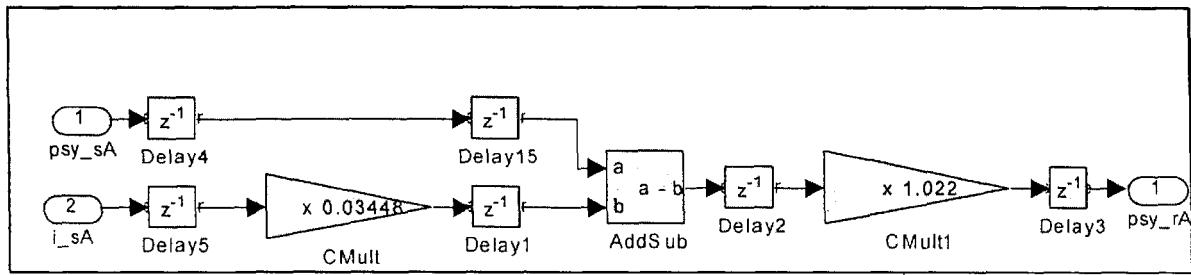

| figure 54 – Calcul de flux statoriques .....                                               | 122 |

| figure 55 – Calcul de flux rotoriques .....                                                | 123 |

| figure 56 – Racine carrée non restaurante dans l'estimateur de flux rotoriques .....       | 123 |

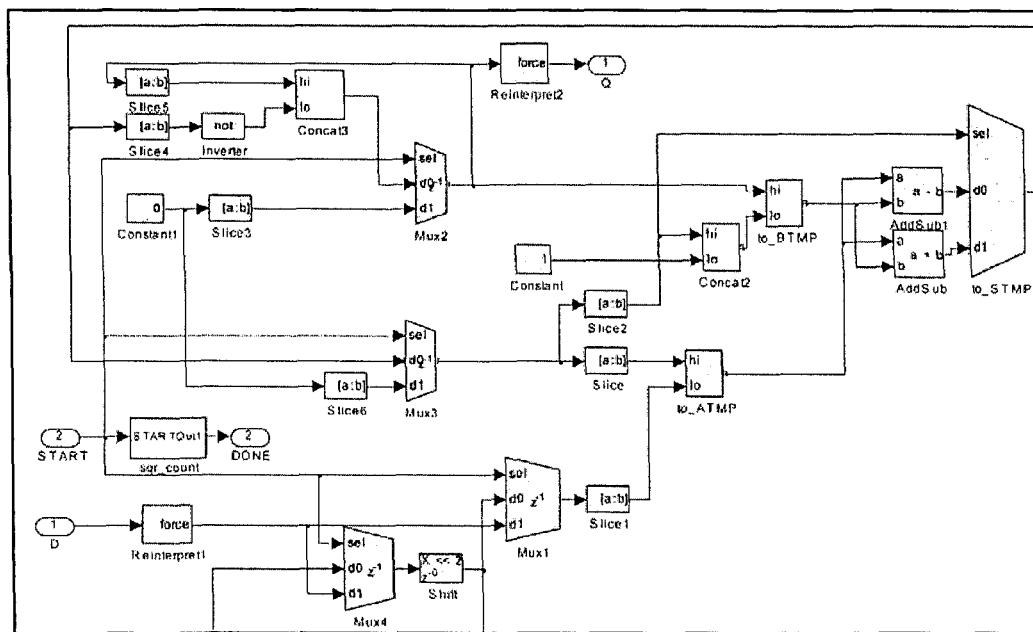

| figure 57 – Racine carrée non restaurante.....                                             | 125 |

|                                           |     |

|-------------------------------------------|-----|

| figure 58 – Division non restaurante..... | 125 |

| figure 59 – Bloc SPS .....                | 143 |

## Liste des tableaux

|                                                                                |     |

|--------------------------------------------------------------------------------|-----|

| tableau 1 - Paramètres du moteur en laboratoire .....                          | 32  |

| tableau 2 - Tailles des opérateurs division et racine carrée.....              | 49  |

| tableau 3 - Temps des 3 méthodes de simulation .....                           | 76  |

| tableau 4 – Les 2 Intel Strataflash Flash memory devices.....                  | 105 |

| tableau 5 - Configurations sur carte Amirix AP1000 (Configuration Flash) ..... | 105 |

# **CHAPITRE 1**

## **Introduction et problématique**

## 1.1 Introduction générale

Cette recherche s'inscrit dans le cadre d'une thèse de maîtrise en ingénierie, dont le sujet consiste à réaliser la commande vectorielle des moteurs à induction sur une seule puce reconfigurable tout en respectant une contrainte de temps de calcul de quelques microsecondes. Cela est fait pour remédier aux implémentations DSP (*digital signal processors*) nécessitant des temps d'exécution assez longs, notamment si l'on inclut l'algorithme de calcul PWM (*pulse-width modulation*) ainsi que des estimateurs complexes de grandeur difficilement mesurables. De plus, cette recherche vise la mise en place d'une plateforme de travail et d'une méthode de développement standardisées de manière à fournir une technique de conception optimale pour des applications futures.

## 1.2 Contexte et revue bibliographique

Actuellement, les fonctions algorithmiques sont généralement implémentées sur deux types de plateforme programmable, soit les DSPs et les FPGA (*field programmable gate arrays*). Les FPGAs peuvent exécuter de multiples opérations en parallèle, ce qui leur donne un avantage sur les DSPs dans le domaine de la mécatronique comme indiqué dans [1]. L'intérêt de ce domaine d'ingénierie interdisciplinaire est de concevoir des systèmes automatiques puissants et de permettre le contrôle de systèmes hybrides complexes. Des plateformes DSP incluant une carte comme la DS1103 de dSPACE sont d'excellents outils encore aujourd'hui utilisés pour le prototypage rapide de contrôle, tel que dans [2] et [3]. Comme ces cartes utilisent des DSPs à virgule flottante avec un langage logiciel de haut niveau, ce sont des outils moins appropriés pour supporter le contrôle d'applications hautement modulaires. Avec des langages à description matérielle comme le VHDL et des outils de synthèse pour FPGAs reconfigurables peu coûteux, le

prototypage rapide d'algorithmes modulaires et complexes constitue une solution efficace déjà observable dans [4][5][6] .

Cependant, le développement sur ces puces n'est pas simple et une plateforme de travail intégrée devient nécessaire afin de concevoir, modéliser, simuler et optimiser. Comme il s'agit d'une plateforme de recherche, il est intéressant de vérifier la viabilité des outils académiques accessibles et maintenus indépendamment en assurant les liens entre chaque outil. De cette manière, chaque module de développement peut évoluer et faire bénéficier à la méthode des nouvelles fonctionnalités et performances sans délai important.

Pour le contrôle vectoriel, les modules clés comme l'estimateur de flux, la transformée de Park, les régulateurs PI (*proportional-integral*) et le générateur PWM sont particulièrement exigeants en calcul. Leur réalisation matérielle avec l'outil de conception DSP System Generator de Xilinx (XSG) œuvrant dans l'environnement Matlab/Simulink constitue le cœur de cette thèse. Particulièrement, la recherche s'intéresse à la méthode de conception qui assure la détermination rapide des précisions d'entrée et de sortie en termes de bits pour chacun des nombreux blocs constituant le contrôle vectoriel. L'intégration de l'outil GAPPY pour accélérer l'établissement et l'optimisation des précisions d'un modèle XSG au sein d'une méthode de prototypage n'a pas, au mieux de notre connaissance, de précédents dans la littérature. Un exemple du type d'utilisation actuelle de GAPPY est présenté dans [7].

Pour le design et la simulation, les plateformes commerciales offertes par les compagnies canadiennes RTDS Technologies [8] et OPAL-RT [9] proposent des performances intéressantes, mais les coûts sont très élevés. De plus, ces solutions intégrées force l'usager à ne pas profiter de la flexibilité de gérer des outils académiques indépendamment. Comme alternative aux coûts importants des systèmes commerciaux, les auteurs de [10][11] proposent une solution peu coûteuse qui se nomme VTB-RT (*Virtual Test Bed Real Time*). Cette méthode utilise du matériel commun (des PCs ordinaires) et le système d'exploitation Linux. Il est cependant nécessaire d'effectuer la configuration de ces systèmes et de migrer les modèles vers ces outils, ce qui force l'usager à dépendre une fois de plus d'une solution d'un tiers parti. La méthode de développement de cette thèse va plutôt regarder l'intérêt d'intégrer les modèles XSG à des

modèles SPS (*SimPowerSystems*) dans l'environnement Simulink et de simuler à l'aide du mode de co-simulation appelé « co-simulation libre » qui utilise un FPGA dans la boucle.

Les résultats de cette thèse serviront comme base de conception pour le prototypage rapide de toutes sortes d'algorithmes de contrôle haute performance déjà existants ou à venir, ainsi que d'autres applications diverses (MEMS, biologie, etc.).

### 1.3 Problématique

Cette recherche vise le développement d'un contrôle vectoriel avec PWM et génération d'ondes entièrement sur FPGA, ainsi que d'une plateforme de travail pour toutes les phases du développement à l'aide d'outils académiques accessibles et gérés individuellement. La méthode de prototypage rapide doit être suffisamment flexible pour être réutilisée lors de projets futurs de mise en œuvre d'algorithmes complexes, et ce, tout en exploitant la plateforme de travail de façon optimale.

Le temps d'exécution du contrôle vectoriel ne doit pas dépasser quelques  $\mu$ s, même si la physique de l'électronique de puissance ne nous fournit qu'une contrainte de l'ordre de 25  $\mu$ s pour des raisons de dissipation d'énergie chez les modules de puissance [12]. En respectant une condition temporelle aussi sévère, on démontre qu'il est possible d'utiliser cette technique pour des algorithmes encore plus complexes. Aussi, cette méthode de développement anticipe les avancements technologiques au niveau de l'électronique de puissance qui permettraient alors de profiter d'un contrôle d'une telle rapidité.

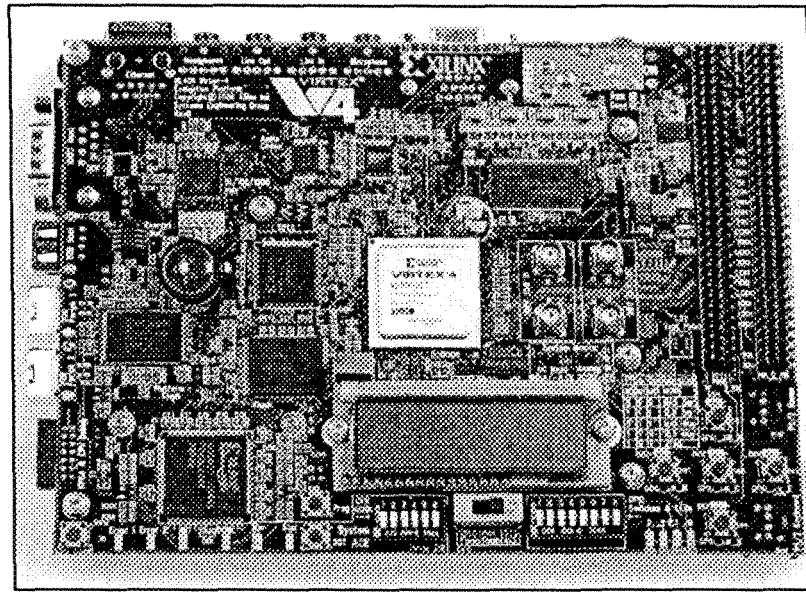

La méthode proposée couvre la dernière étape pour un prototype jugé fonctionnel après simulation, soit l'intégration avec le matériel physique pour tests en laboratoire. Pour ce faire, le prototype doit être placé dans la logique du FPGA (Virtex II pro) contenu sur la carte PCI Amirix AP1000, fournie au laboratoire par la Canadian Microelectronics Corporation (CMC). Cette carte communiquera avec la carte AIO PMC66-16AISS8AO4 de General Standards Corporation pour recevoir les signaux de l'électronique de puissance. La communication entre les deux cartes

s'effectue via l'interface PMC. Personne n'ayant précédemment développé une application pour la carte Amirix utilisant la communication PMC avec une carte d'entrée/sortie, c'est en collaboration avec mon collègue Stéphane Simard que le pilote logiciel et la logique permettant la communication en question sont développés. La partie logique (sur FPGA) sera discutée en détail dans cette recherche puisque son développement est requis pour assurer le bon fonctionnement de la plateforme de travail. Cette logique supplémentaire est développée dans cette recherche afin de communiquer avec le pilote logiciel ainsi que la carte AIO. L'achat de cette carte AIO a d'ailleurs influencé CMC dans le choix d'une carte d'acquisition à coupler à la carte Amirix, et notre système de communication entre ces cartes fait l'objet d'un contrat entre CMC et l'UQAC.

Le prototypage rapide de la commande vectorielle sur FPGA présente avant tout une problématique de méthodologie. Pour un système simple en boucle ouverte, l'implémentation, l'analyse des résultats et la correction du modèle posent peu de difficultés, car les entrées et les sorties peuvent rapidement être comparées aux résultats souhaités d'un modèle de référence. L'opération est plus difficile lors du prototypage rapide d'un système complexe en boucle fermée. La nature modulaire d'un système complexe développé avec les outils Simulink - XSG (dont les licences sont fournies par CMC) demande le débogage individuel des différents modules. Cependant, les entrées et les résultats d'un bloc dépendent nécessairement des autres blocs du modèle. Les sorties du système y sont réinjectées et affectent les résultats subséquents. Comme il n'est pas possible de tester chaque module individuel en boucle fermée immédiatement après sa conception, la technique de prototypage rapide doit tout de même permettre de vérifier la validité des blocs avant l'assemblage final.

La méthode de prototypage doit également fournir une manière d'évaluer la précision du modèle. Comme les valeurs de chaque module devront être comparées à un résultat théorique idéal provenant du modèle de référence Matlab en virgule flottante, cette comparaison doit être juste. Cela serait facile à vérifier s'il s'agissait d'un système en boucle ouverte, mais dans le cas d'une boucle fermée, les valeurs désirées doivent être les mêmes à l'entrée et à la sortie du bloc. En résumé, la méthode doit traiter chaque bloc en boucle ouverte, mais en lui injectant des signaux de boucle fermée provenant du modèle de référence. Une fois l'assemblage du prototype terminé, la réponse de la commande vectorielle est comparée à la référence, et les résultats sont

analysés. Il y aura nécessairement des variations entre les résultats, surtout à l'initialisation du système, mais l'analyse doit en tenir compte et juger si le prototype offre la réponse souhaitée, avec la précision demandée. Aussi, la précision doit être évaluée et ajustée en fonction de tous les cas possibles pour une certaine gamme de valeurs (ex : pour couvrir les paramètres d'un large éventail de moteurs différents).

La méthode de prototypage rapide doit donc satisfaire les caractéristiques suivantes :

- la **généralité** (pour être facilement adaptée à un autre algorithme de contrôle ou à un autre moteur);

- la **flexibilité d'analyse** (pour produire des résultats différents, comme la précision des calculs, avec un minimum de modifications);

- l'**exactitude des résultats** (pour la réponse du système et la précision).

Une fois la méthode de prototypage développée, l'obtention des résultats pour l'analyse et le débogage se fait par simulation. Ici encore, la complexité du contrôle pose problème. Si l'on désire effectuer le prototypage d'un contrôle dont le temps de calcul est très court, on doit aussi utiliser des vitesses d'échantillonnage très courtes. Le nombre de calculs fait ainsi croître le temps de simulation. Un exemple chiffré donne une bonne idée du problème.

Soit un contrôle nécessitant 200 coups d'horloge. À une vitesse de 100 MHz, on obtient un temps de contrôle de 2  $\mu$ s. Si un contrôle doit être déclenché à toutes les 25  $\mu$ s, il faut  $\frac{5s}{25\mu s} \times 200 = 40\,000\,000$  coups d'horloge simulés pour observer les résultats du moteur pendant 5 secondes. Le contrôle comporte un nombre élevé d'opérations mathématiques et une grande précision (un grand nombre de bits pour la partie entière et fractionnaire des opérandes), ce qui le rend trop lent (plusieurs jours) à simuler par des logiciels comme Matlab - Simulink. De plus, ces tests impliquent qu'une quantité massive de résultats soit accumulée dans Matlab, ce qui a pour conséquence d'alourdir davantage les opérations. On trouve une solution partielle à la lenteur des simulations dans la co-simulation offerte par XSG qui utilise le FPGA pour effectuer le travail du prototype. Il est une fois de plus nécessaire de trouver une manière optimale d'intégrer cet outil à la méthode de prototypage rapide, car la préparation de chaque co-simulation est relativement longue. Bien que Xilinx fournit des exemples de modèles pour illustrer le gain de temps avec la

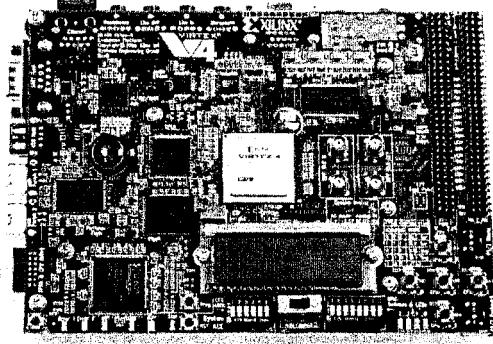

co-simulation, il n'est pas possible de trouver une étude dans la littérature qui nous permet de bien estimer les temps impliqués dans l'utilisation de cet outil. La recherche permet de mieux estimer les cas où la co-simulation XSG est un bon choix et le temps que cela va impliquer dans le processus de développement. La plateforme de co-simulation utilisée est la carte Xilinx ML402 fournie par le Conseil de recherches en sciences naturelles et en génie du Canada (CRSNG).

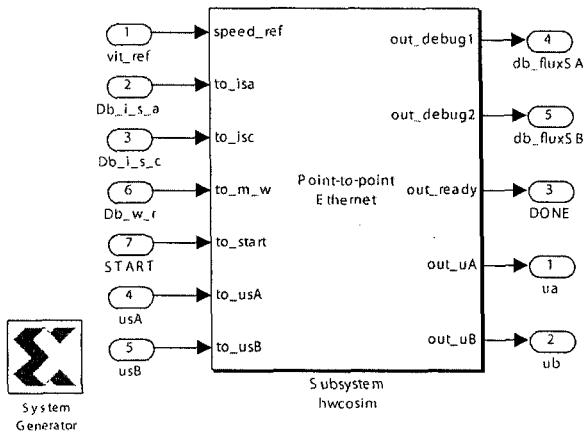

Le contrôle ne doit pas seulement être simulé à l'aide de valeurs théoriques. Il faut pouvoir le tester dans un environnement réel, c'est-à-dire, en le reliant à un moteur. Évidemment, vu le coût des équipements et la sécurité du personnel, il serait illogique et totalement irresponsable de brancher le prototype au moteur et d'observer ce qui se passe. Ce moteur doit avant tout être simulé, et c'est le toolbox SPS de Matlab-Simulink qui sera employé à cet effet. Cependant, le couplage des blocs SPS et XSG n'est pas une simple question de branchements. Afin de simuler les deux entités simultanément, les contraintes temporelles doivent être considérées. Le moteur est simulé en termes de temps, alors que le prototype XSG est simulé en pas d'horloge. Un couplage temporel doit donc se faire pour assurer une bonne simulation. Une fois ce couplage achevé, l'intégration des outils de co-simulation de XSG devient critique pour accélérer la simulation.

Les moteurs et modules de puissance (CRSNG) sont installés au laboratoire ainsi que les filtres, une charge résistive qui permet de varier les couples de charge et les connecteurs manquant pour assurer la communication entre tous les appareils.

## 1.4 Objectifs et méthodologie de recherche

La recherche est amorcée par une revue de la littérature concernant le contrôle vectoriel, les implémentations de commande des moteurs électriques sur FPGA, et l'implémentation *space vector PWM* (SVPWM) sur FPGA. En parallèle, les détails de la méthode de prototypage rapide sur FPGA sont définis de manière brouillonne. Pendant ce temps, l'outil XSG est exploré en détail afin de bien maîtriser ses fonctionnalités.

Avec les étapes de la préparation complétées, le développement du premier prototype du contrôle vectoriel est amorcé en se basant sur les équations théoriques de ce type de contrôle (voir annexe A). La méthode de prototypage rapide est modelée afin d'obtenir des résultats cohérents et de perdre un minimum de temps pendant le développement. Les erreurs commises et les outils non appropriés permettent de particulièrement bien cerner le flux optimal de conception. Pour le contrôle vectoriel, les blocs individuels sont développés et testés, ainsi que l'ensemble du modèle. La réponse du système obtenue est comparée à celle du modèle de référence de commande vectorielle, et la précision est optimisée en conséquence. Cette étape d'ajustement de la précision du modèle avec l'outil GAPP (section 4) devient un point critique de la méthode avant d'entamer le processus de développement.

Une fois le prototype apte à respecter toutes les conditions temporelles, il peut être synthétisé et ensuite chargé dans un FPGA. L'outil de co-simulation de XSG est utilisé pour remplacer le modèle du prototype dans Matlab-Simulink par un bloc unique qui communique avec le FPGA via un lien ETHERNET.

Une version SPS de l'équipement (moteur et module de puissance) est conçue pour connecter au bloc du prototype à co-simuler. Pour une première estimation du modèle en conditions physiques réelles, le contrôle théorique (une version modifiée du modèle Matlab de référence) est couplé au moteur virtuel afin d'estimer la réponse attendue. Lorsque le moteur fonctionne bien avec ce contrôle, celui-ci est remplacé par la version XSG (le prototype). Ici, un travail est effectué afin de respecter les contraintes temporelles, car les deux systèmes sont vus différemment par Matlab-Simulink. Le prototype est simulé en termes de pas d'horloge, et le moteur en temps effectif.

Pour les étapes précédentes du développement, la co-simulation matérielle ne peut être employée, car un grand travail de débogage doit encore être effectué. Pour éviter que les simulations s'éternisent pendant des semaines, une précision de contrôle moins agressive est utilisée pendant les tests du système de commande vectorielle (pour la génération de signaux PWM). L'idée est d'obtenir de bonnes courbes de réponse sans toutefois s'occuper de la précision qui sera ajustée plus tard.

Lorsque le couplage est fonctionnel, la co-simulation matérielle est utilisée pour accélérer le temps de calcul, afin de vérifier une plus grande plage de résultats et d'évaluer la précision de ces derniers.

Comme le prototype est développé pour FPGA, l'espace et le temps sont considérés. Pour l'espace, la cellule logique (CL) est l'unité de mesure utilisée. Pour le temps, deux échelles sont nécessaires; lorsque l'ensemble du système est considéré, incluant moteur, contrôle et PWM, c'est la  $\mu$ s, et pour les composants implémentés strictement sur le FPGA, les coups d'horloges font office de référence.

En ce qui concerne le prototypage, plusieurs informations doivent être compilées. Les temps d'exécution de chaque composant du contrôle, en coup d'horloge, sont déterminés en analysant le chemin critique d'un bloc et en confirmant par simulation. Les ressources du FPGA nécessaires au bloc sont évaluées grâce à un outil d'estimation de XSG qui fournit un résultat après synthèse, placement et routage. Finalement, des estimations de temps de simulation sont calculées selon les diverses techniques utilisées. Toutes ces informations sont aussi amassées pour le système en entier, une fois qu'il est fonctionnel et débogué. Avec ces statistiques, il devient possible de fournir une échelle réaliste pour accompagner les étapes de la méthode de prototypage, facilitant l'estimation en gestion de projet. Cela permet par exemple au développeur utilisant la méthode de prédire à l'avance la taille du FPGA nécessaire à son application, et d'approximer le temps de développement que le projet demandera. Cela donne aussi une idée de l'effort qui doit être fourni dans l'optimisation du prototype aussi bien en termes de densité logique que de temps d'exécution.

## **CHAPITRE 2**

### **Algorithme et plateforme**

## 2.1 Introduction et schématisation de l'algorithme

Avant d'amorcer le développement du prototype, il faut étudier l'algorithme utilisé. Dans le cas présent, il s'agit de la commande vectorielle. La recherche bibliographique permet d'identifier des articles et des sources qui expliquent la commande afin d'en tirer les équations mathématiques. On peut alors schématiser la commande vectorielle sous forme de boîtes connectées par des fils. Chacun de ces blocs va produire des sorties en appliquant les entrées aux équations du bloc.

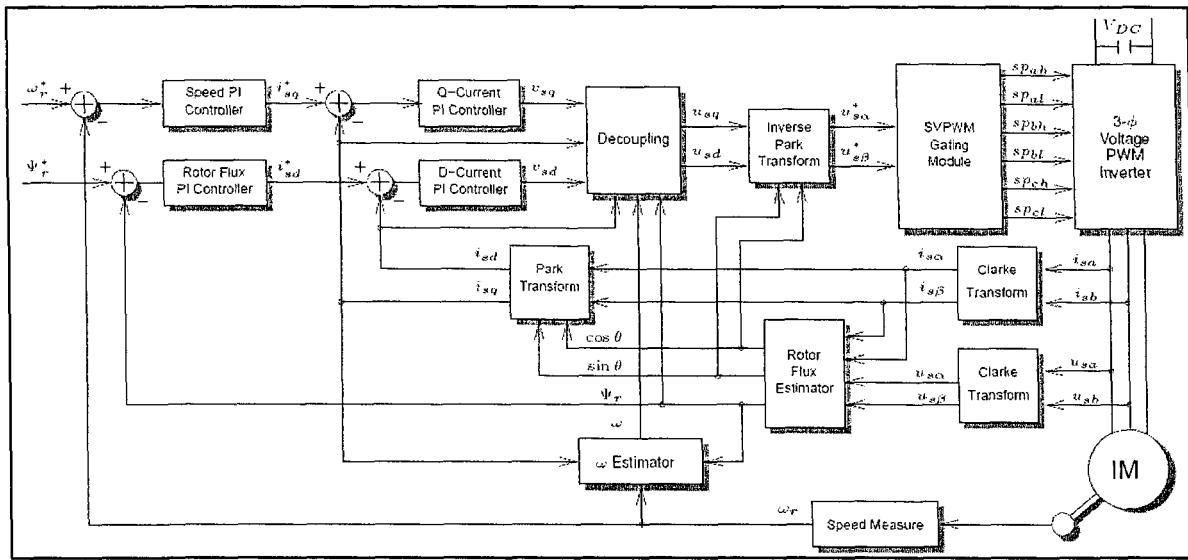

### 2.1.1 Contrôle vectoriel

Le choix du contrôle vectoriel est intéressant comme application utilisée afin de créer une méthode de prototypage optimale. C'est sa complexité et sa modularité qui offrent un défi intéressant ainsi qu'un bon terrain d'évaluation pour des outils de co-simulation. La présence d'une racine carrée et d'une division offre aussi l'avantage de pouvoir appliquer et vérifier l'implémentation de ces opérations selon un modèle non restaurant plus économique en terme de ressources logiques (voir section 3.4). Les résultats de l'implémentation de ces opérations ont permis de publier deux articles sur le sujet que l'on retrouve à l'annexe I.

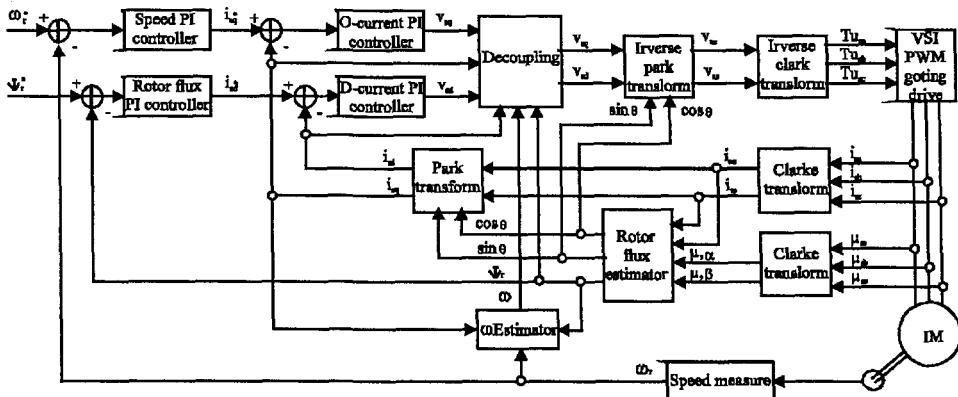

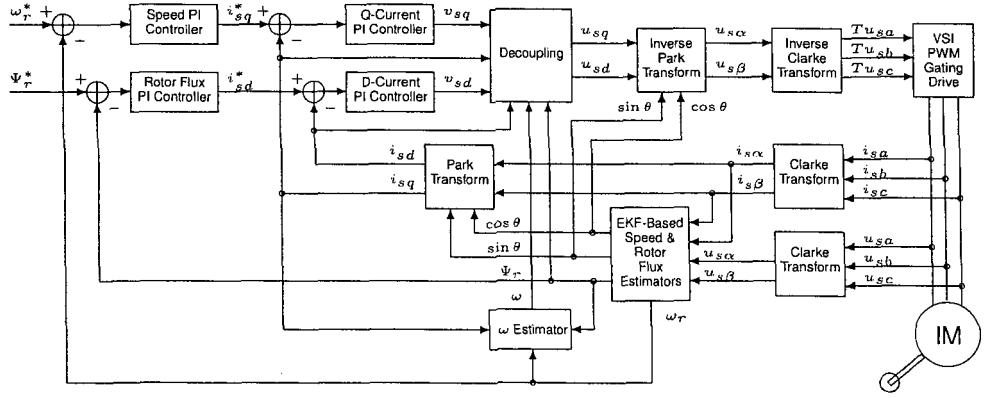

figure 1 - Contrôle vectoriel

La figure 1 montre comment le contrôle vectoriel est scindé sous forme modulaire. Les équations de chaque module se retrouvent à l'annexe A. Dans cette recherche, la lecture de la vitesse se fait avec capteur.

### 2.1.2 Survol du portillonnage (délais d'activation et temps de maintien)

Avant la venue des larges FPGAs disponibles aujourd’hui, les méthodes utilisées, incluant l’utilisation de DSPs seuls ou en combinaison avec des microcontrôleurs spécialisés, permettaient un temps de cycle total de plus de 100  $\mu$ s. Il n’y avait alors pas de manière efficace d’implémenter le SVPWM, ce qui causait l’obtention d’une période de commutation aux alentours de 1-5 kHz, produisant ainsi du bruit audible.

L’introduction de FPGAs plus puissants durant les années 90 a permis pour la première fois de diminuer la quantité de traitement à gérer par le DSP à l’aide de coprocesseurs PWM sur un FPGA de petite taille. Dans le domaine du contrôle de moteur, cela a permis d’augmenter la fréquence de commutation à 10-15 kHz, réduisant nettement le bruit perceptible.

Avec les FPGAs d'aujourd'hui, un contrôle large et complexe comprenant le générateur SVPWM au complet peut se trouver sur une seule puce, tout en supportant des fréquences de l'ordre de 50 kHz. Il serait même possible d'obtenir des fréquences aussi élevées que 100 kHz (transistors MOSFET), mais l'utilité d'une telle vitesse demeure pour l'instant questionable vu que la dissipation d'énergie est proportionnelle à la fréquence de commutation et que le courant généré par les transistors de puissance (IGBT, GTO) diminue selon la même proportion. Même à 20 kHz, la dissipation d'énergie est importante.

Par exemple, l'équipement utilisé dans notre laboratoire supporte, selon le manufacturier, une fréquence de commutation maximale de 20 kHz. Cependant, il est recommandé de ne pas utiliser une fréquence au-delà de 16 kHz sauf si absolument nécessaire, comme dans le cas d'un contrôle nécessitant une très large bande. Une fréquence de 16 kHz offre l'avantage d'une tension de sortie avec moins de distorsions causées par l'insertion du temps mort. Les simulations du contrôle vectoriel en boucle fermée de cette recherche sont donc paramétrées afin de reproduire une telle fréquence.

Ces désavantages limitent l'intérêt d'utiliser des onduleurs à très haute fréquence de commutation. Un exemple d'application où la fréquence doit être limitée est l'opération de gros moteurs industriels lorsqu'un fort courant est requis de l'onduleur. Pour des applications sur plateformes autonomes (ex. : robots mobiles), c'est la dissipation d'énergie qui doit être minimisée. Une fréquence de 16 kHz semble donc largement suffisante pour la plupart des applications de contrôle, tout en demeurant à l'extérieur de la bande de fréquence audible.

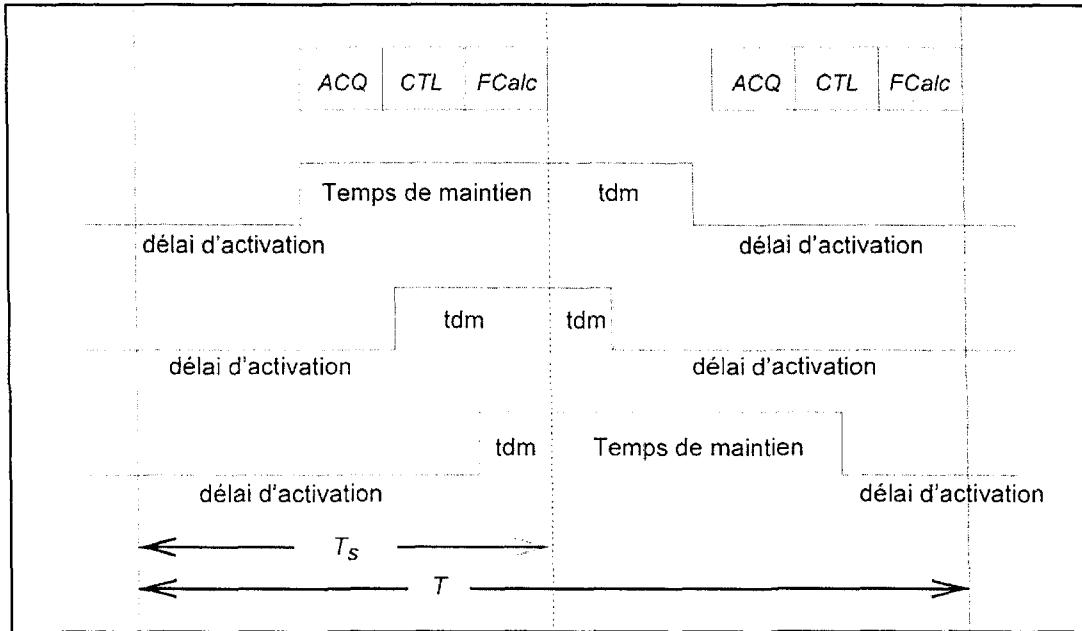

figure 2 - Portillonnage PWM asymétrique

Ces contraintes sont prises en considération lors de la maximisation de la fréquence d'échantillonnage et de contrôle. Afin d'optimiser cette dernière sans augmenter la fréquence de commutation, un portillonnage PWM asymétrique est employé. Ceci permet d'obtenir une période d'échantillonnage  $T_s$  qui est égale à la moitié de la fréquence de commutation  $T$ . La figure 2 illustre le cycle d'acquisition (ACQ), de contrôle (CTL) et de calcul des délais d'activation (FCalc) qui sont observables à la fin de la période  $T_s$ . Le délai d'activation  $T_f$  représente le temps nécessaire avant d'allumer les transistors de puissance, alors que le temps de maintien  $T_d$  représente le temps où ces transistors continuent de conduire. Ces temps suivent l'équation  $T_f + T_d = T_s$ .

Même s'il existe sur le marché des transistors de puissance qui atteignent presque 100 kHz (MOSFET), les calculs de ce travail seront effectués en considérant une fréquence de commutation de 16 kHz exigée par le module de puissance IGBT utilisé dans cette recherche. Cette fréquence offre un temps de commutation de 62.5  $\mu$ s, soit un échantillonnage de 31.25  $\mu$ s. Il est important de s'assurer d'avoir suffisamment de temps pour l'achèvement du cycle de temps  $T_{cycle}$  qui se représente selon l'équation  $T_{cycle} = T_{acq} + T_{ctl} + T_{Fcalc}$ . La section 3.3 illustre que le

$T_{ctl} + T_{F_{calc}}$  nécessite environ 2  $\mu$ s. Avec des convertisseurs analogues numériques (ADC) qui supportent 1 million d'échantillons par seconde (MSPS), soit  $T_{acq} = 1 \mu$ s, cela donne un  $T_{cycle} = 3 \mu$ s, ce qui est très rapide.

Ceci veut dire que la technologie permet de réduire le temps de calcul d'un algorithme complexe de contrôle à quelques  $\mu$ s. Des algorithmes divers pourront donc être modifiés et adaptés afin de bénéficier de cette accélération. Un exemple est illustré à la figure 2 où l'utilisation d'un générateur SVPWM asymétrique permet d'effectuer deux cycles de contrôle complets au lieu d'un seul à l'intérieur d'une période de commutation tout en respectant la physique.

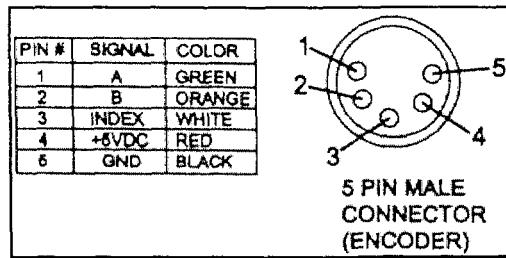

### 2.1.3 Lecture de vitesse provenant d'un encodeur optique

Le moteur utilisé comporte un encodeur optique afin de fournir l'information concernant la vitesse de rotation actuelle de l'engin. Il y a 5 sorties observées, soit : A, B, INDEX, +5 et GND. Chaque signal correspond à un fil de couleur, illustré à la figure 3.

figure 3 - Fils de l'encodeur optique

L'encodeur optique traduit la position angulaire en signal électrique. Pour chaque rotation du moteur, 1000 lignes d'encodage produisent 1000 changements d'état sur les lignes A et B. Donc, plus la période d'un signal sur A ou B est longue, plus le moteur tourne lentement. Le retard entre les signaux A et B permet quant à lui de déterminer la direction de rotation de l'engin.

En cherchant dans la littérature, on trouve l'article [13] qui propose une méthode de lecture de signaux d'un encodeur optique optimale sur FPGA. Les lectures de vitesses sont alors précises pour un grand nombre de scénarios vu la possibilité d'ajuster la méthode de calcul selon la fréquence à traiter. En basse vitesse, l'implémentation utilise une méthode de comptage de période alors qu'en haute vitesse, c'est un comptage de fréquence.

Dans le cadre de ce travail, un simple décodeur sera employé afin de pouvoir plus rapidement passer à la phase de tests. Ce décodeur ne va pas changer, qu'il opère en basse ou en haute vitesse. Vu la présence de 1000 changements d'état par rotation, un intervalle de 1 ms est observé par le FPGA, et la vitesse moyenne est estimée en calculant la valeur de rotation par minute (RPM) correspondante à l'aide de l'équation  $X \times \frac{60 \text{ s}}{1000 \text{ lignes}} = Y \text{ rpm}$  où  $X$  est le nombre de lignes détecté par seconde.

Cette méthode de lecture moyenne agit comme un petit filtre sur la vitesse mesurée. Un échantillon de 1 ms est suffisant pour la dynamique du moteur qui sera testé en laboratoire, alors que le filtrage devrait empêcher les vibrations de trop affecter les résultats.

## 2.2 Référence Matlab de l'algorithme

Même en connaissant les équations qui forment l'algorithme, il est nécessaire de vérifier la validité du prototype. Il faut établir une référence Matlab de l'algorithme; une version fonctionnelle de l'algorithme de contrôle dont les résultats peuvent être accumulés dans le logiciel Matlab. Comme les données numériques sont faciles à importer dans l'environnement Matlab, nos données de référence peuvent être générées dans n'importe quel logiciel qui peut exporter ses résultats. Souvent, cette référence sera le résultat d'une autre recherche ou de l'aboutissement d'autres travaux. Dans le cas présent, un modèle de commande vectoriel développé sous Matlab par le professeur Rachid Beguenane [14] sera utilisé comme référence. Le fait d'établir une telle référence a une conséquence importante pour la réalisation des objectifs : si le prototype donne, avec les mêmes entrées que pour la référence, des sorties qui approchent

celles de la référence en respectant une contrainte d'erreur déterminée, le prototype peut être optimisé et co-simulé. En d'autres termes, le prototype est considéré comme étant valide.

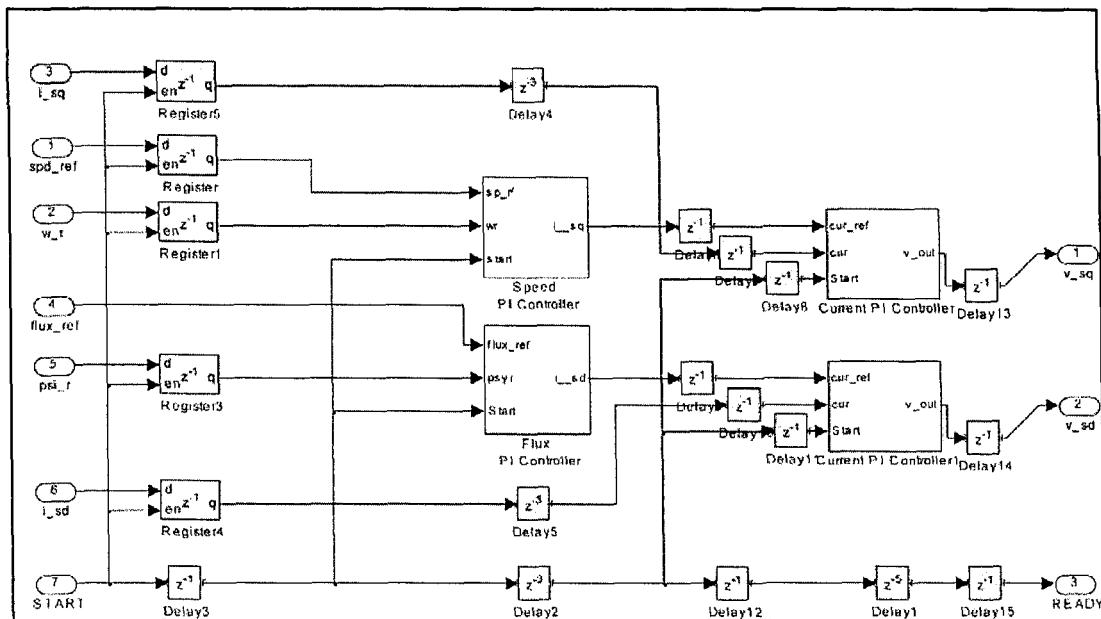

### 2.2.1 Contrôle Vectoriel

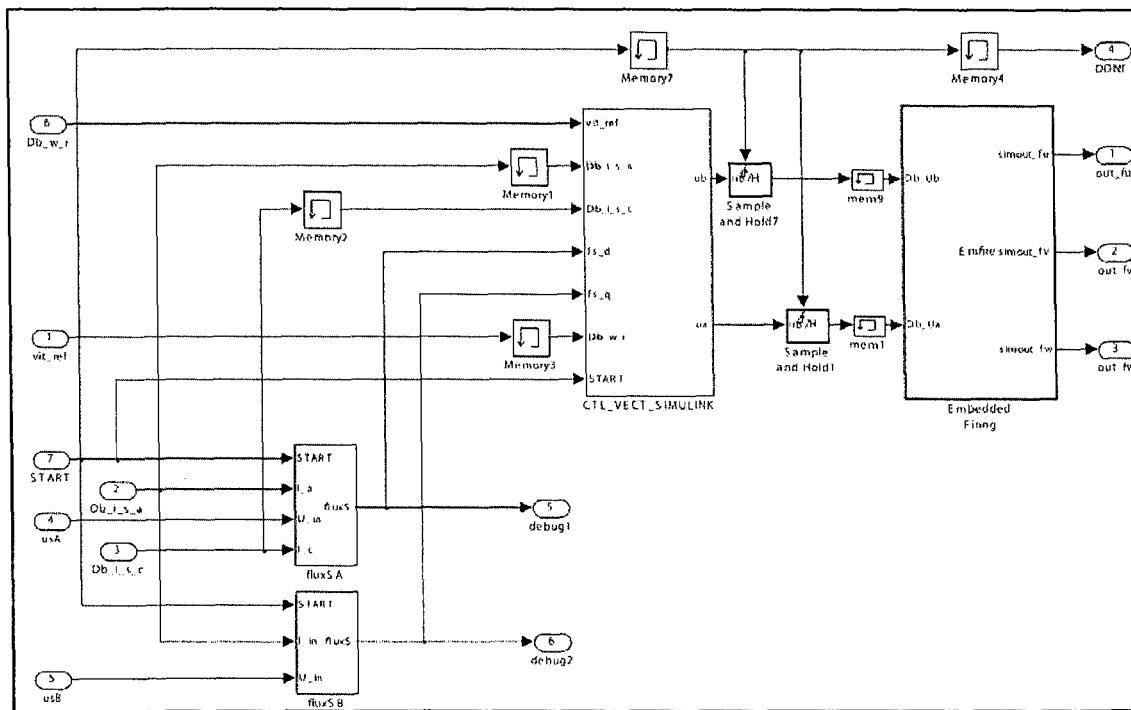

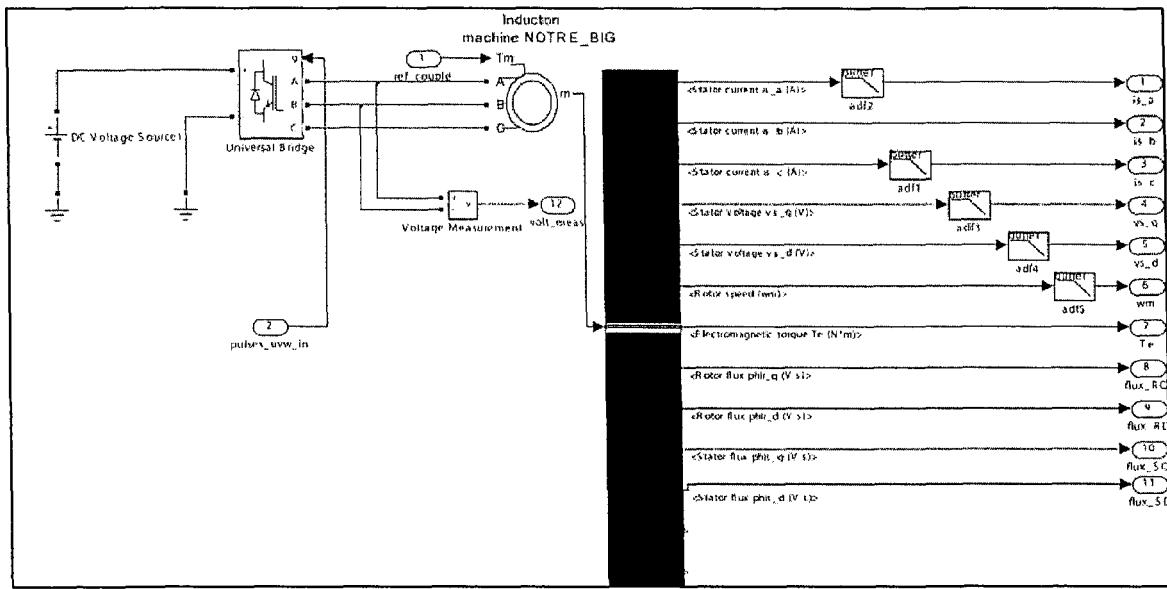

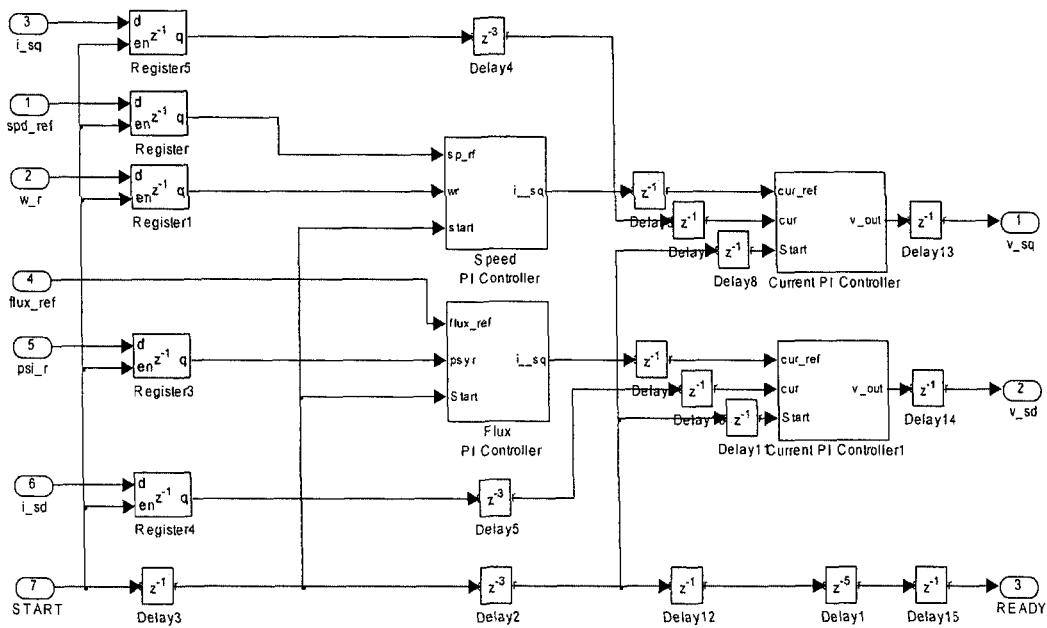

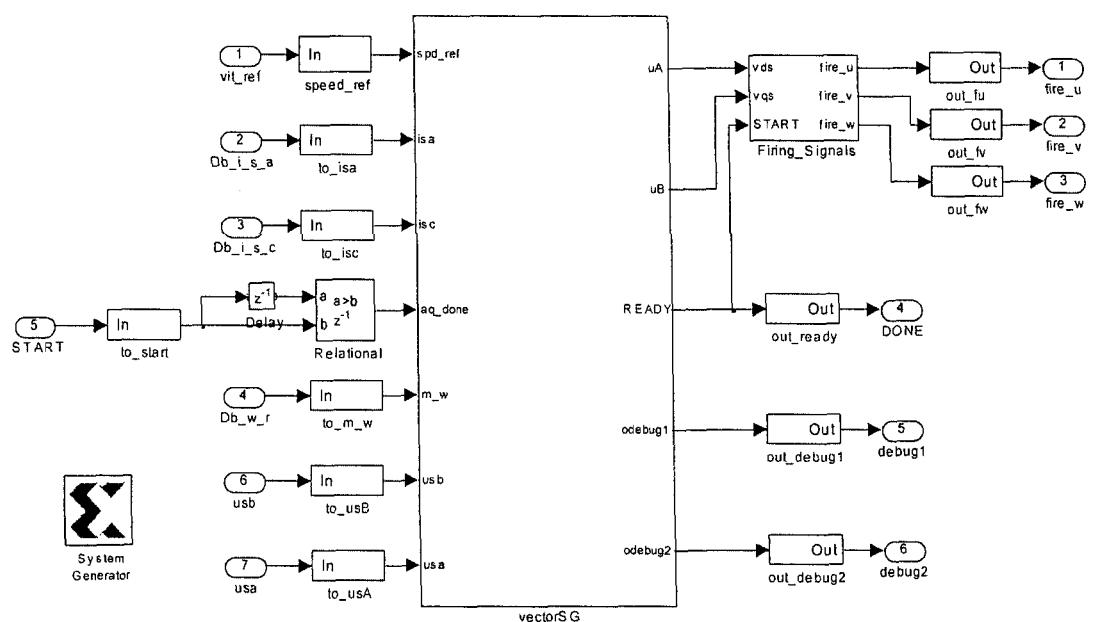

**figure 4 - Interface du contrôle Simulink (référence)**

La figure 4 représente l'implémentation de référence Simulink du contrôle vectoriel basé sur le modèle de [15]. Comme il s'agit d'une référence, la précision maximale de Matlab est utilisée. L'interface à la sortie et à l'entrée du bloc qui contient le modèle correspond exactement à l'interface de contrôle vectoriel implémenté en utilisant l'outil XSG. Ceci permet de facilement substituer ces systèmes dans l'environnement de test qui comprend les engins SPS ainsi que le bloc de portillonage (voir section 4.9).

### 2.2.2 Portillonnage (délai d'activation et temps de maintien)

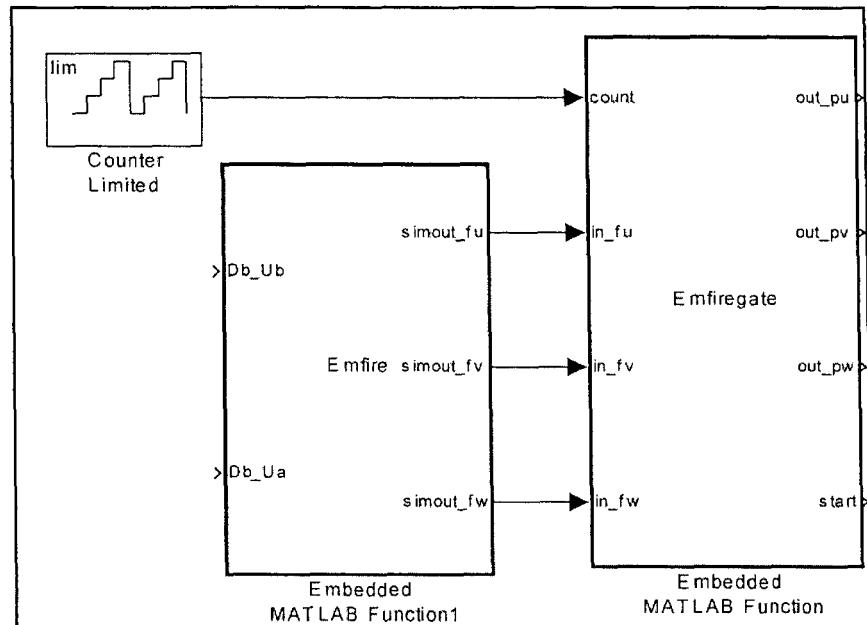

Pour le calcul des délais d'activation ainsi que pour le portillonnage, la référence Matlab est facilement transférable vers un bloc de fonction embarquée (code à l'annexe C dans l'environnement Simulink. Ces blocs (figure 5) sont utilisés dans la simulation en boucle fermée de la référence Simulink couplée aux équipements modélisés par SPS. De plus, le bloc portillonnage sera réutilisé lors de la co-simulation du contrôle vectoriel XSG car il s'agit d'un processus séparé qui ne peut être co-simulé dans le cadre de cette application (voir explication à la section 4.8).

figure 5 - Calcul des délais d'activation et portillonnage (embedded Matlab functions)

### 2.2.3 Moteur et électronique de puissance

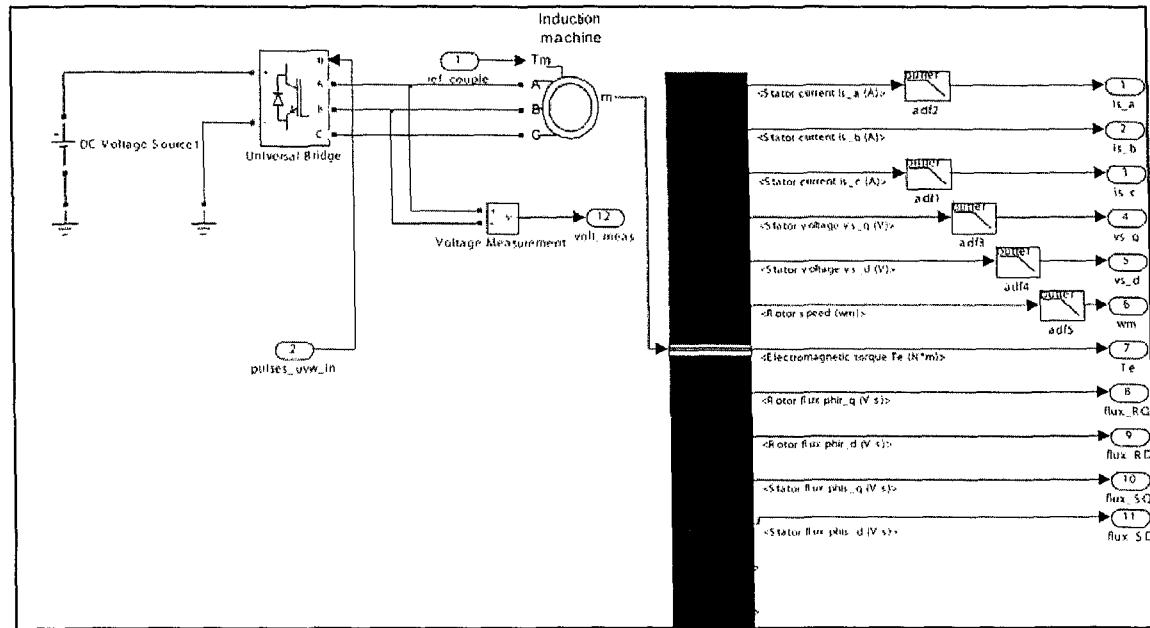

Le toolbox SPS est utilisé afin de modéliser le moteur et le module de puissance dans un environnement de contrôle vectoriel complet. Le développement du modèle XSG de contrôle vectoriel dépend fortement des paramètres utilisés pour identifier le moteur SPS simulé. C'est

pourquoi les paramètres de ce moteur partagent la nomenclature des variables utilisées pour le modèle XSG. Il n'y a donc pas de fichier d'initialisation particulier pour le bloc SPS illustré à la figure 6.

figure 6 - Module de puissance et moteur à induction (SPS)

Lors du développement, un premier ensemble de paramètres est utilisé qui correspond au moteur retrouvé dans un tutoriel de SPS. Ce moteur est choisi pour faciliter le test du portillonage en comparant les résultats avec ceux du tutoriel SPS de SVPWM. Une fois le modèle XSG fonctionnel, les paramètres du moteur disponible en laboratoire qui sera la cible de tests physiques sont utilisés. Ces paramètres sont illustrés dans le tableau 1.

| Moteur Motorsoft 2928 |                          |

|-----------------------|--------------------------|

| Puissance             | 250 W                    |

| Vitesse               | 4000 RPM                 |

| Voltage               | 42 V                     |

| $P_p$                 | 1                        |

| $R_S$                 | 8.1 $\Omega$             |

| $L_S, L_R$            | 0.8155 H                 |

| $R_R$                 | 3.8048 $\Omega$          |

| $J$                   | 0.0014 kg m <sup>2</sup> |

**tableau 1 - Paramètres du moteur en laboratoire**

Un des objectifs de la plateforme de développement établie dans cette recherche étant la versatilité du modèle généré, le changement de paramètres entre deux moteurs si complètement différents démontre la flexibilité offerte par la plateforme de travail. Cela démontre aussi que l'optimisation n'est pas trop agressive, ce qui limiterait l'étendue des valeurs que peuvent prendre les paramètres du moteur.

Les tensions et les courants sont filtrés avant leur introduction au contrôle vectoriel. Lors du développement du modèle, des filtres d'ordre 4 et de fréquence de 5000 Hz sont utilisés afin de faciliter le débogage du modèle et de mieux évaluer la précision de sortie de celui-ci. Une fois le modèle assez performant selon les standards du développement, des filtres de fréquence de 500 Hz sont utilisés, ce qui correspond à ceux fabriqués par le technicien de département pour le montage en laboratoire.

### 2.3 Collecte des données de la référence

La dernière étape préparatoire en ce qui concerne l'algorithme consiste à effectuer la collecte des données de la référence. Comme le prototype XSG est développé bloc par bloc, ces derniers

sont nécessairement reliés par des signaux intermédiaires. Ceux-ci sont bien identifiés lors de la schématisation de l'algorithme, mais ils peuvent être difficiles à identifier dans le modèle de référence. En effet, ce dernier peut être un code complexe sans forme graphique qui se prête mal à l'identification rapide de signaux. Il faut malgré cela isoler chacun de ces signaux (si possible) dans la référence et accumuler les résultats pendant une simulation (figure 7). Ces données seront utilisées pour tester individuellement chaque bloc du prototype avec XSG. Vu la complexité de l'algorithme, il est clair que la quantité de données produites sera énorme. Heureusement, il n'est pas nécessaire d'accumuler une trop grande plage de données pour les signaux intermédiaires. Il s'agit ici de vérifier que nos équations reflètent le comportement de la référence, sans plus. Les cas extrêmes (valeurs trop grandes, trop petites, dépassemens, etc.) seront gérés plus tard dans le projet à l'aide de l'outil GAPPY (voir section 4.2). Cependant, il faut être plus rigoureux pour l'ensemble du système. Il faut simuler plus longtemps en accumulant les entrées et sorties de l'ensemble de l'algorithme, sans les signaux intermédiaires (figure 8). Dans le cas de la commande vectorielle, un profil de vitesse et de charge est utilisé pour tester le contrôle. La vitesse de référence est changée, ainsi que la charge, et les résultats sont notés. Ceci présente l'avantage de pouvoir afficher la réponse du système sous forme de graphiques qui peuvent ensuite être comparés avec ceux du prototype.

figure 7 - Collecte des données de référence (Contrôle Simulink)

figure 8 - Collecte des données de référence (réponse du moteur)

## 2.4 Platerorme Amirix

Bien qu'il s'agisse de la dernière étape de développement qui sera suggérée dans la méthode de prototypage rapide produite dans ce travail, il est nécessaire de tout de suite explorer les détails de la plateforme de test en laboratoire. Cette dernière est composée de deux cartes, soit une carte de développement Amirix AP1000 et une carte d'acquisition analogique numérique PMC66-16AISS8AO4 de General Standards. Cette dernière se branche à la carte Amirix via le bus PCI mezzanine (PMC). La recherche mentionne aussi une carte Xilinx ML402. Cette carte est utilisée strictement pour la co-simulation car sa configuration pour cette étape est plus rapide.

Notre achat de carte AIO a influencé CMC qui cherchait une carte d'acquisition à joindre à la plateforme Amirix AP1000 afin d'offrir une solution complète aux groupes de recherche académiques de son réseau. Comme la documentation et les exemples fournis par Amirix ne contiennent pas de projets utilisant la communication via PMC (ni sur la plateforme Linux embarquée, ni sur le *Baseline* de la carte), un contrat entre CMC et l'UQAC (travail réalisé par notre équipe de recherche) fut signé avec pour objectif de produire le nécessaire pour assurer la communication des deux cartes, ainsi qu'une méthodologie simple pour utiliser la carte AIO à partir de la logique matérielle du FPGA. Cet ajout au *Baseline* de la carte Amirix est maintenant utilisé à l'échelle nationale dans la recherche des circuits intégrés et le domaine de MEMS (Micro Electro Mechanical Systems). Comme il s'agit d'une étape de la méthode de prototypage de cette recherche, les détails de développement de la communication sur la carte Amirix sont présentés dans l'annexe B.

## **CHAPITRE 3**

### **Modèle System Generator**

### 3.1 Brève description

Dans le cadre de cette recherche, le développement du prototype s'effectue avec le logiciel XSG. Il s'agit d'un toolbox développé par Xilinx pour être intégré dans l'environnement Matlab-Simulink et qui laisse l'usager créer des systèmes hautement parallèles pour FPGA. Les modèles créés sont affichés sous forme de blocs, et peuvent être raccordés aux autres blocs et autres toolbox de Matlab-Simulink comme SPS. Une fois le système complété, le code VHDL généré par l'outil XSG reproduit exactement le comportement observé dans Matlab. Pour le prototypage rapide, le choix de cet outil est facilement explicable. Le système de contrôle devant être vérifié et simulé souvent et rapidement pendant tout le développement, il est beaucoup plus simple d'analyser les résultats avec Matlab qu'avec les outils habituellement associés au VHDL, tel que Modelsim. Aussi, le modèle peut ensuite être couplé à des moteurs virtuels (à l'aide du toolbox SPS) et des simulations en boucle fermée sont réalisables. Quand le prototype fonctionne, le passage vers la plateforme matérielle pour des tests sur le terrain est rapide, ce qui rend la validation du prototype un projet réalisable à court terme.

### 3.2 Méthode de développement

Avec une banque de résultats provenant de la référence établie, le développement des blocs du prototype peut se faire. L'outil XSG est utilisé afin de produire un modèle qui va tout de suite fonctionner sur le matériel une fois achevé et validé.

### 3.2.1 Développement de bloc individuel et validation de premier niveau

L'avantage d'utiliser XSG pour le prototypage rapide devient plus évident lorsqu'il est nécessaire de tester un bloc achevé. Il suffit de brancher aux entrées les données intermédiaires obtenues de la référence. En simulant, on recueille les données à la sortie pour ensuite les comparer avec les données de la référence. Notons qu'il peut y avoir une certaine erreur, car une précision arbitraire selon le nombre de bits des opérandes est employée. L'outil GAPPY va plus tard permettre d'ajuster cette précision (voir section 4.2). Pour l'instant, il faut seulement vérifier le comportement du bloc.

Lorsqu'un bloc se comporte bien, ce test s'effectue assez rapidement, car le temps de simulation est plus court. Nous avons déjà mentionné que les signaux intermédiaires ne sont pas emmagasinés en trop grand nombre, de façon à rendre le temps de simulation acceptable. Cependant, lorsqu'un bloc ne répond pas comme il se doit, le travail devient plus important. Dans le cas de la commande vectorielle, plusieurs blocs sont d'une complexité importante comme le bloc découplage ou le bloc estimateur de flux du rotor. La provenance de l'erreur à l'intérieur du bloc est souvent difficile à identifier. Il faut alors reprendre notre méthode en traitant le bloc comme un algorithme séparé. On retourne vers la référence afin d'identifier les signaux que l'on retrouve à l'intérieur du bloc problématique, et une nouvelle collecte de données est effectuée. Ensuite, de nouvelles sorties temporaires sont instanciées à l'intérieur du bloc fautif pour tenter d'identifier la source du problème.

Afin de rapidement identifier si le comportement du modèle XSG correspond au modèle théorique Simulink, les résultats des deux modèles sont comparés. Cependant, il s'agit de tests qui ne serviront pas seulement lors du développement initial, mais qui seront sollicités lors de toutes les phases de débogage. Ainsi, il est important d'établir certaines règles afin d'accéder rapidement à cet environnement lorsqu'un problème survient. Deux méthodes sont ici proposées : la méthode simultanée et la sainte croyance.

Voyons premièrement les conditions communes aux deux méthodes.

- *Le bloc XSG utilise le même fichier d'initialisation que le modèle final*

Il est important d'utiliser le même fichier d'initialisation que le modèle XSG final afin de ne pas avoir à créer d'autres copies de ce fichier. Chaque fichier supplémentaire d'initialisation doit être modifié si un changement de constante, de précision, etc. est effectué. Lorsqu'un modèle est composé de nombreux blocs, maintenir un nombre égal de scripts d'initialisation devient une source d'erreurs trop importante.

- *Les données (entrées et sorties) sont toutes dans une même source*

Dans les deux méthodes proposées, les entrées proviennent de l'enregistrement des signaux lors d'un test en boucle fermée du système de référence (Simulink et SPS). Comme tous ces signaux sont enregistrés au même endroit (ex. : fichier MAT), il est important de toujours utiliser cette source, même si une seule portion des signaux est utilisée. Encore une fois, la maintenance de multiples fichiers doit être évitée pour minimiser les causes d'erreur et faciliter la réutilisation de l'environnement de bloc individuel lors de débogage avancé.

- *Les entrées respectent la nomenclature des signaux du modèle de référence Simulink*

Dans un système complexe, plusieurs signaux sont insérés dans des blocs différents afin de subir plusieurs traitements. Il convient donc d'utiliser le même nom pour un signal injecté dans plusieurs blocs différents. Dans l'environnement de bloc individuel, les entrées sont souvent des signaux provenant du *workspace* ou d'un fichier. Comme la deuxième règle spécifie que l'on doit utiliser un seul et même fichier de source, les noms des entrées vont devoir correspondre dans chaque environnement de test. Les sorties ne vont pas se plier exactement à cette règle selon la méthode choisie.

- *Les blocs sont encapsulés exactement comme dans le modèle final ou de référence*

Il est important d'utiliser le même routage de fils afin de pouvoir supprimer et remplacer un bloc rapidement lors de modifications à vérifier.

- *L’analyse des résultats se trouve dans un fichier Matlab unique au bloc, exécutable en tout temps*

Chaque bloc doit avoir son fichier Matlab d’analyse qui va générer les résultats (et souvent, les graphiques) permettant de valider le bloc XSG. Un seul fichier par bloc assure que l’utilisateur n’a pas besoin de faire fonctionner les autres blocs (ou de commenter des lignes du fichier Matlab) pour faire une analyse. Le fichier doit également pouvoir produire une analyse en tout temps, afin que l’usager puisse faire une pause dans sa simulation et analyser les résultats obtenus jusqu’à cette pause, sans devoir compléter un temps donné de simulation.

### 3.2.1.1 La méthode simultanée

figure 9 - méthode simultanée (bloc individuel)

L'environnement contient une source d'entrée, deux blocs et deux ensembles de sorties. La source d'entrée commune aux deux blocs provient du modèle de référence Simulink. Ces signaux sont ensuite injectés dans le bloc XSG ainsi que son bloc Simulink correspondant, en parallèle. Les deux sorties (XSG et référence) sont ensuite enregistrées et comparées à l'aide du fichier d'analyse Matlab créé pour le bloc. Cette méthode est la plus efficace pour tester la correspondance des

deux blocs, car ceux-ci sont tous les deux isolés et doivent traiter les mêmes entrées. Les connexions et délais entre les blocs du système ne sont donc pas une cause d'erreur possible dans ce scénario.

Cependant, la comparaison des deux systèmes occasionne souvent des problèmes de « timing ». Le nombre de pas nécessaire pour le traitement n'est pas forcément le même pour les deux blocs, ce qui engendre l'insertion de blocs supplémentaires pour synchroniser les résultats à comparer et introduit conséquemment une nouvelle source d'erreur. Mais le plus gros désavantage de cette méthode est que, advenant un changement dans le bloc XSG, les contraintes temporelles peuvent être appelées à changer, ce qui signifie que l'usager doit modifier le mécanisme de synchronisation entre les deux blocs. Un tel ouvrage ralentit l'usager lors de tests de débogage et détériore la facilité de réutilisation de l'environnement.

### 3.2.1.2 La sainte croyance

figure 10 - méthode de la sainte croyance

Cette méthode ne contient qu'un seul bloc par environnement, soit le bloc XSG. Pour des entrées qui proviennent de la simulation du modèle Simulink théorique entier, le bloc XSG traite ces données et produit des résultats qui sont ensuite comparés aux résultats enregistrés aux

sorties du même bloc dans le modèle théorique entier. On suppose ici que le bloc du modèle théorique est juste, et que les sorties théoriques utilisées sont fiables pour l'analyse.

L'avantage d'une telle méthode est la rapidité d'utilisation. Un seul bloc doit être simulé par l'ordinateur, un seul ensemble de sorties doit être enregistré, et l'environnement ne change jamais, peu importe les modifications apportées au bloc XSG. La réutilisation de cet environnement est donc très grande, et le débogage s'effectue rapidement.

Cependant, un changement des constantes et paramètres de n'importe quel bloc du système affecte les résultats du système de référence Simulink. Donc, pour chaque changement de constante, la simulation du modèle de référence en entier doit à nouveau être effectuée. Cela n'est pas toujours nécessaire en utilisant la méthode simultanée, car pour une même entrée, les deux traitements sont simulés. Pour un modèle complexe (figure 11), ce désavantage peut coûter du temps plutôt qu'en sauver. Le plus grand désavantage est au niveau de la précision d'identification, car cette méthode ne permet pas de détecter un problème qui vient des interconnexions entre les blocs. Par exemple, un usager pourrait chercher longtemps le problème de correspondance entre deux sorties, alors qu'avec la méthode simultanée, l'erreur serait la même à la sortie des deux traitements, ce qui confirme que le bloc XSG démontre le même comportement que son bloc de référence. Bien que plus rare, ce cas peut se produire et ralentir l'identification d'un problème surtout dans un système qui comporte de nombreux délais, registres et bascules d'entrée et de sortie.

figure 11 - Estimateur de flux rotorique (bloc complexe)

### 3.2.2 Développement d'ensemble, liaisons et validation de deuxième niveau

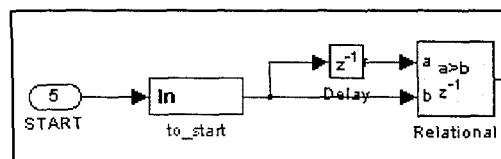

Le test de chaque bloc individuel peut sembler laborieux, mais le temps investi dans cette étape se rentabilise lors du débogage du système complet. En effet, il serait laborieux de chercher le bloc fautif qui rend le système complet inopérant. Plus le test des blocs individuels est rigoureux, moins le test du système complet est laborieux. Souvent, comme dans le cas de la commande vectorielle, le défi est alors de bien synchroniser les blocs entre eux. C'est ici que des signaux « START » et « READY » peuvent être implémentés afin de s'assurer que le traitement des données se fait dans le bon ordre. Il ne s'agit plus ici d'un problème d'ordre mathématique, mais plutôt d'ordre logistique.

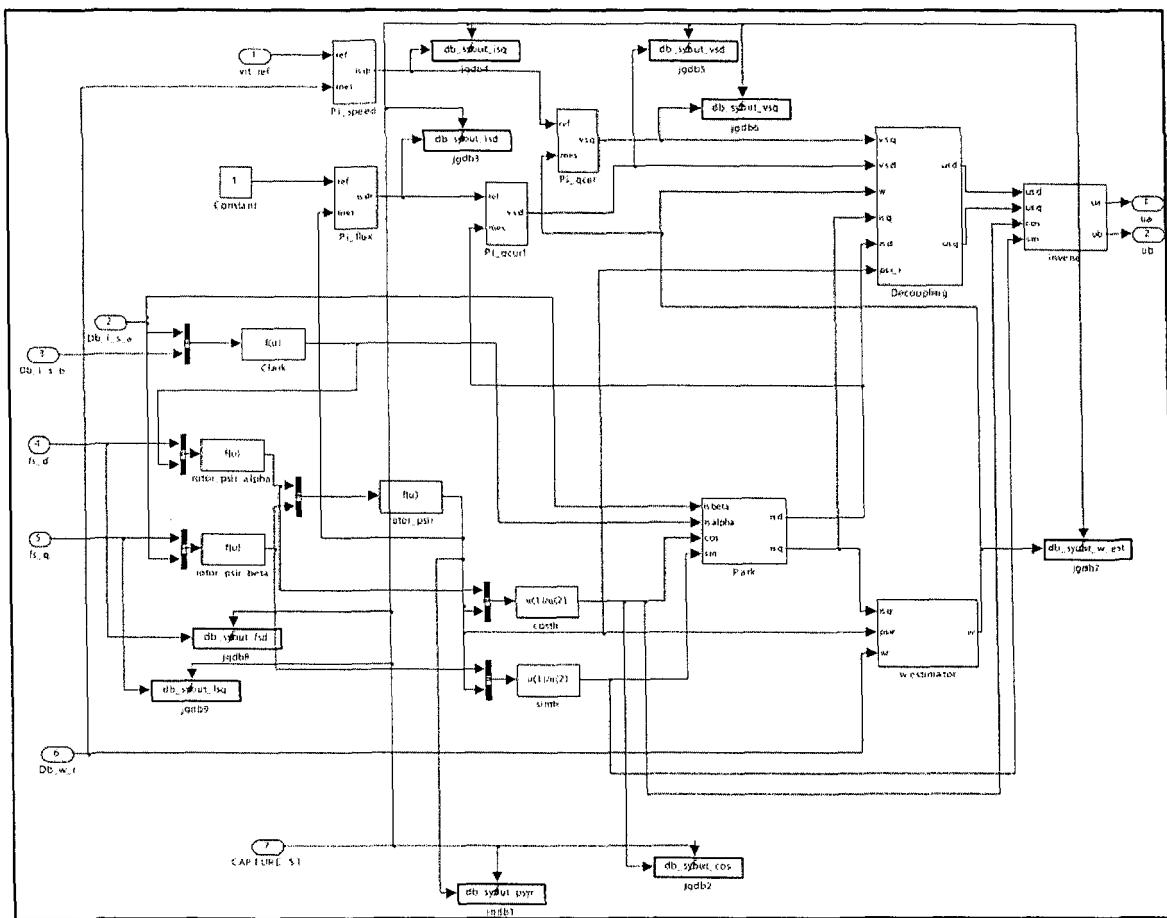

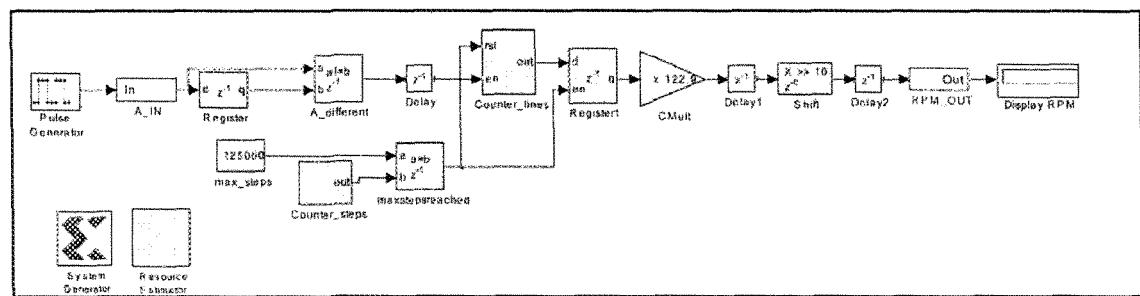

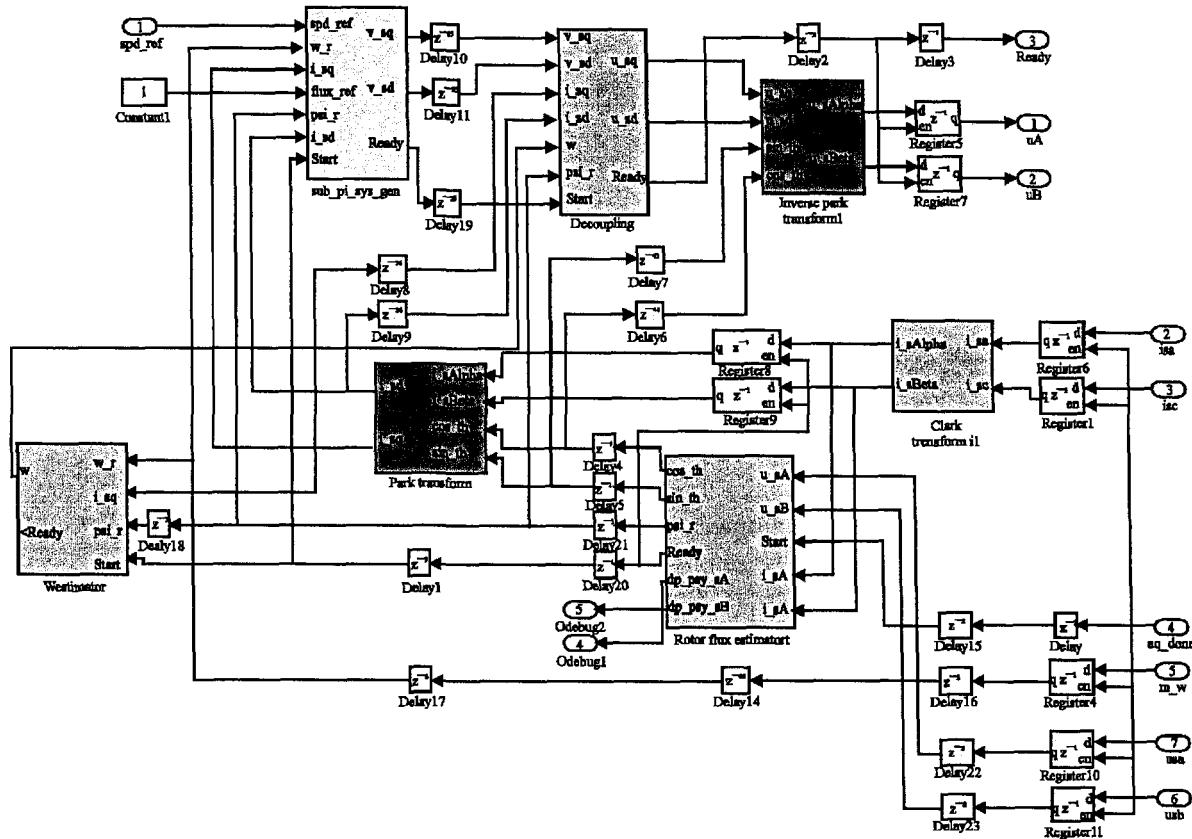

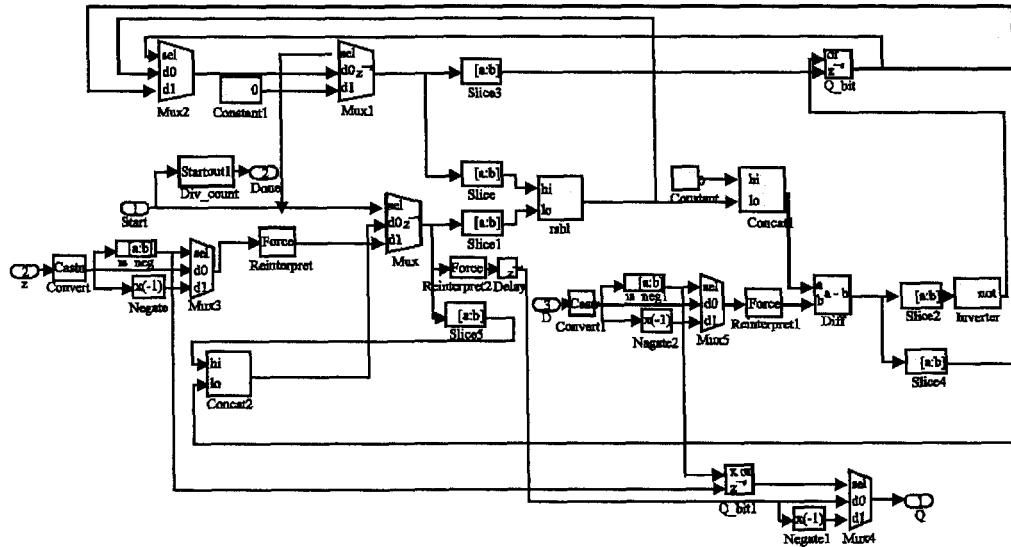

### 3.3 Contrôle vectoriel

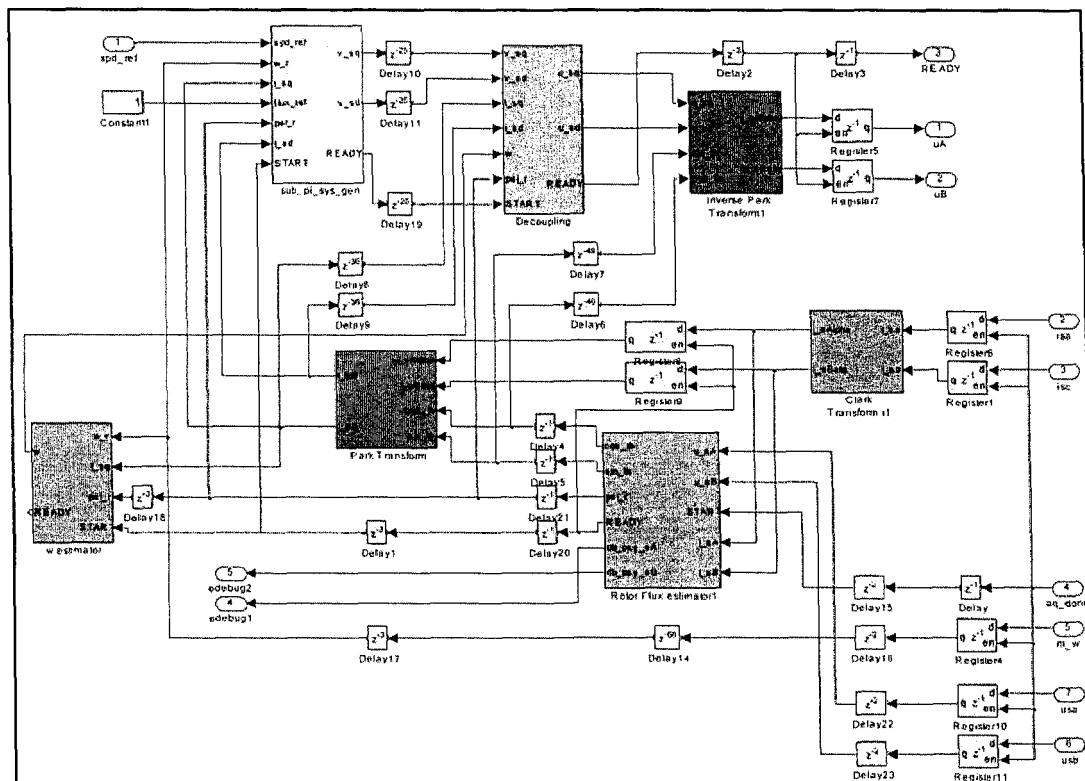

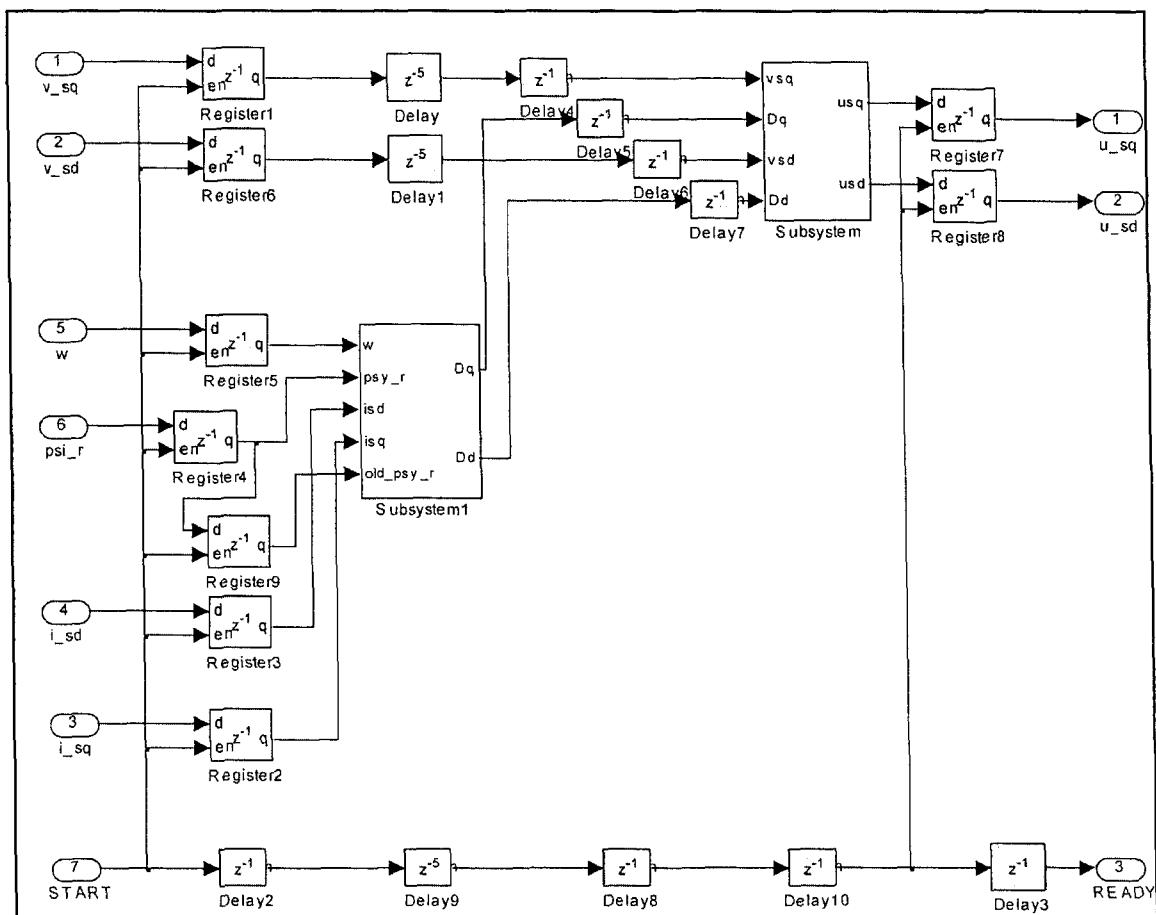

Le contrôle vectoriel XSG est divisé selon les mêmes blocs schématisés lors de la prise de connaissance de l'algorithme de contrôle. De cette façon, il est plus facile de comparer et de tester les blocs de manière individuelle durant le développement. Le résultat d'assemblage de tous les composants est illustré à la figure 12. Des schémas internes de chaque sous-système composant le contrôle vectoriel se trouvent à l'annexe E.

figure 12 - Contrôle vectoriel complet XSG

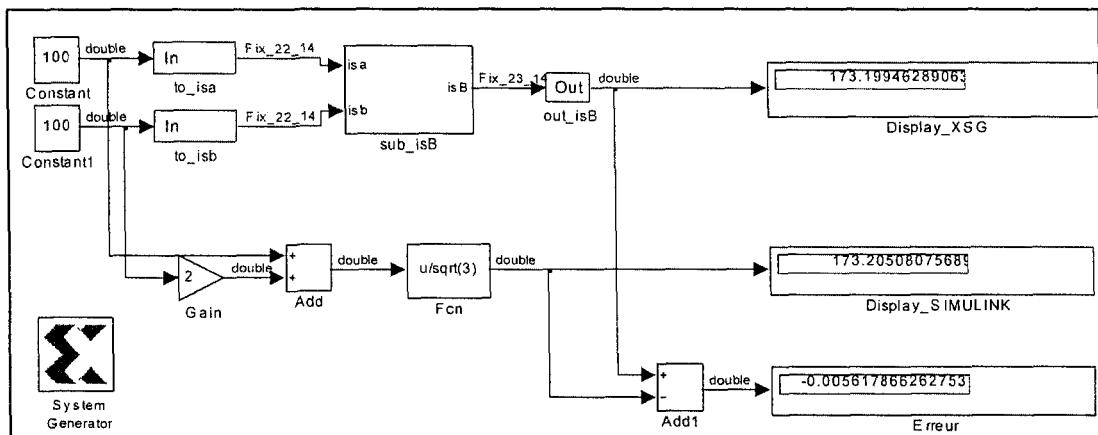

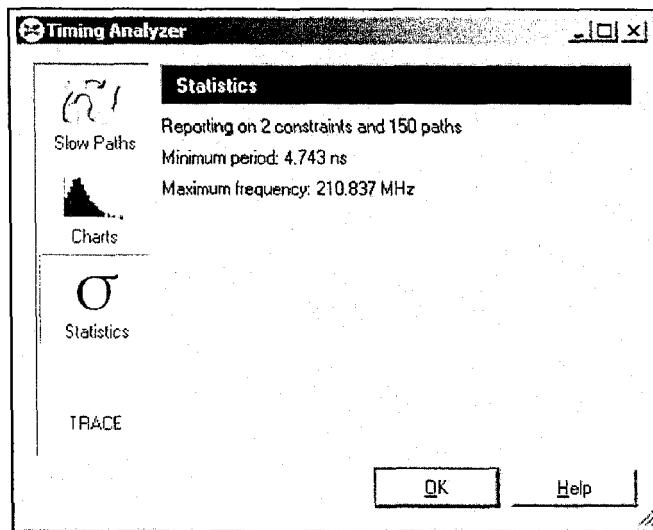

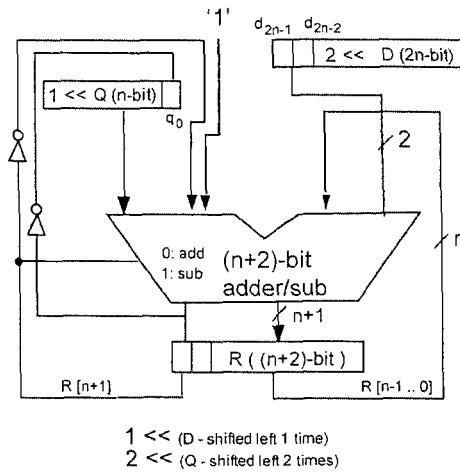

En incluant le calcul des délais d'activation (*firing*), le contrôle demande 122 pas d'horloge avec une précision adéquate pour donner les résultats observés à la section 4.10. Comme illustré dans la section 2.1.2, le contrôle ne s'effectue que deux fois pour une période de commutation, ce qui signifie qu'à une vitesse d'horloge de 62.5 MHz (environ 2  $\mu$ s), il a amplement le temps de se compléter. Advenant le cas où il serait désirable d'effectuer des contrôles en série, il faut considérer qu'on doit attendre 70 pas d'horloge entre chaque échantillonnage. Ceci est dû au fait que l'opération de division et celle de racine carrée présentes dans le système doivent produire un résultat avant de traiter une nouvelle valeur (voir section 3.4).

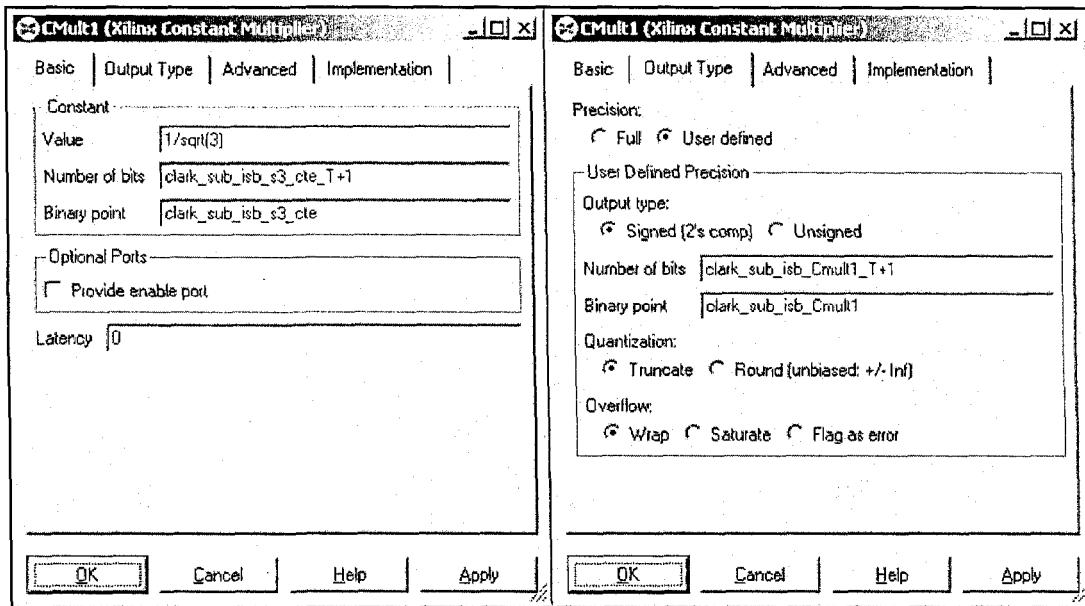

La figure 13 illustre les propriétés d'un bloc d'opération XSG où la précision peut être changée par une valeur ou une variable. La section 4.2 explique l'importance d'utiliser des variables et l'outil Gappa pour déterminer ces précisions. La précision des signaux d'entrée de tout le système (courants, tensions, vitesse) est représentée sur 16 bits, car il s'agit de la précision offerte par la carte AIO utilisée au laboratoire.

figure 13 - propriétés d'un bloc XSG

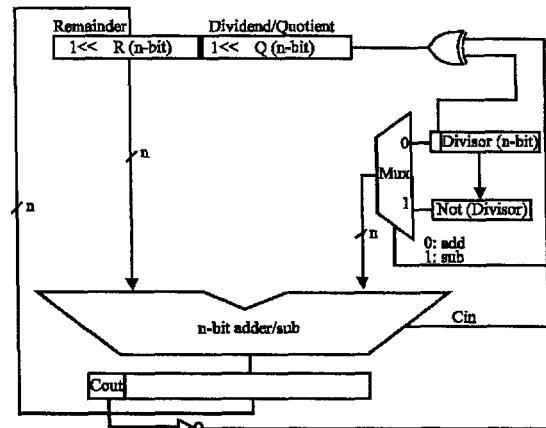

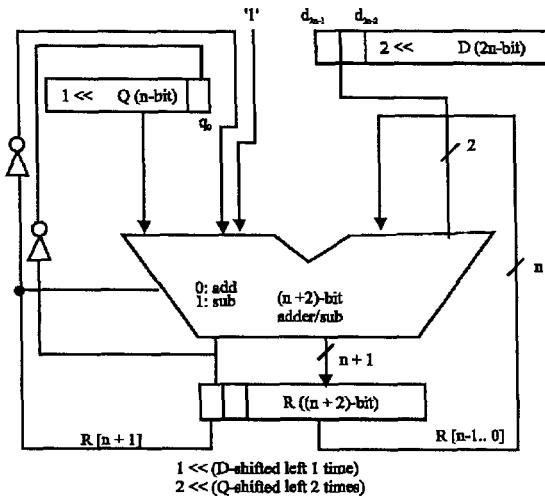

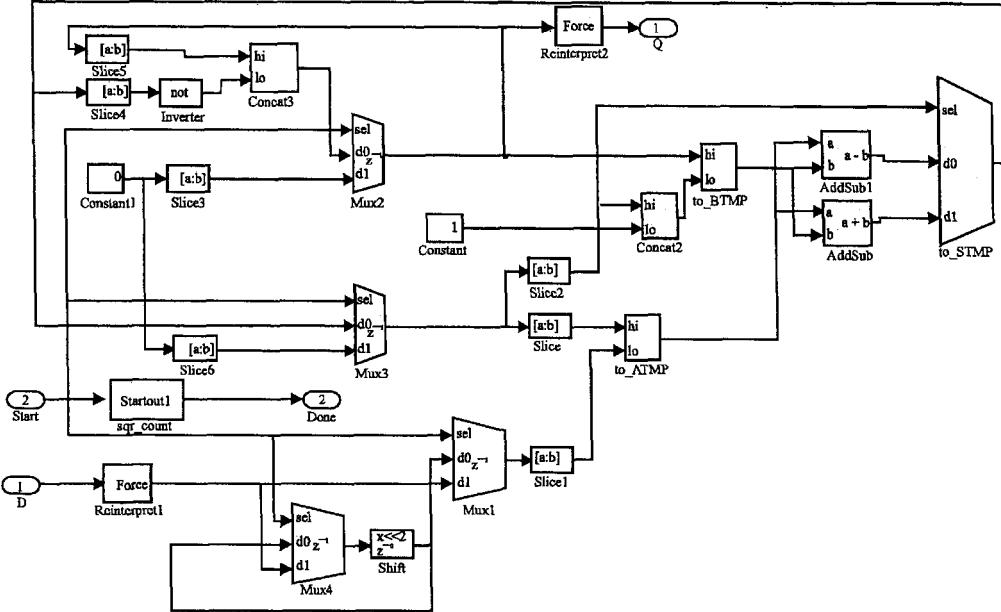

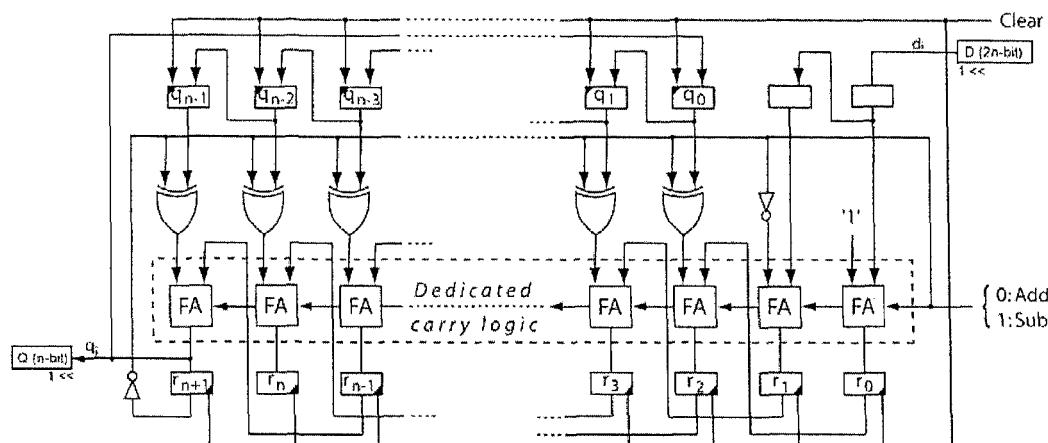

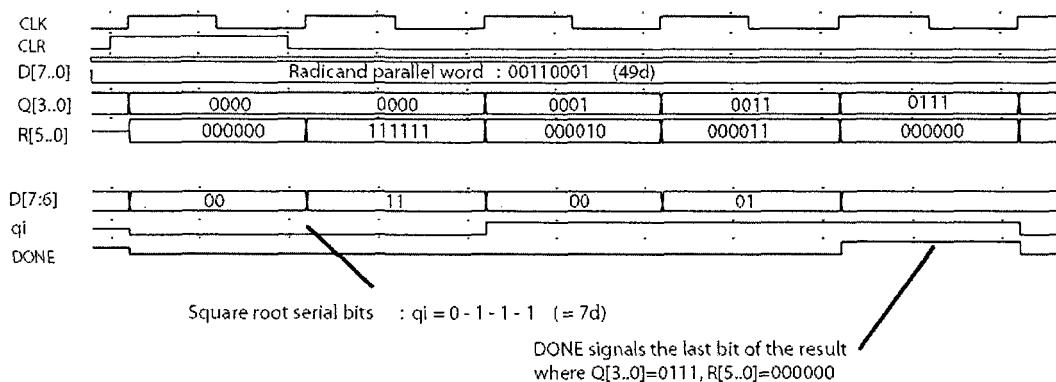

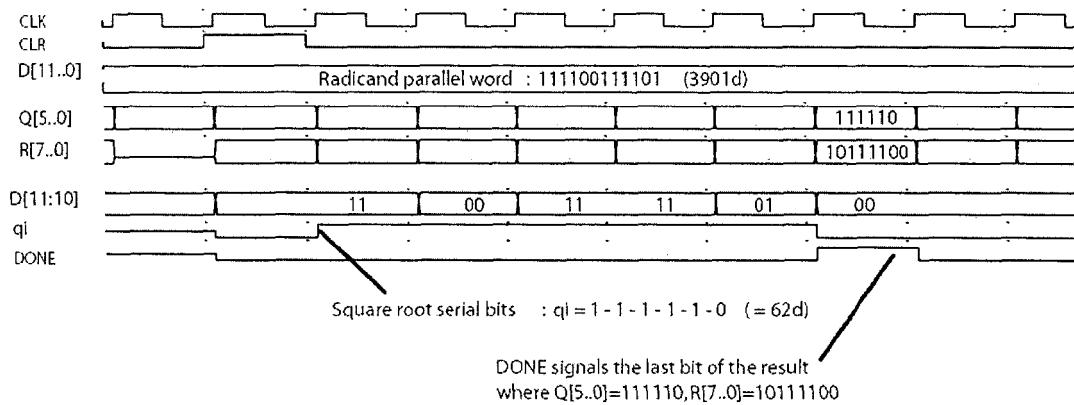

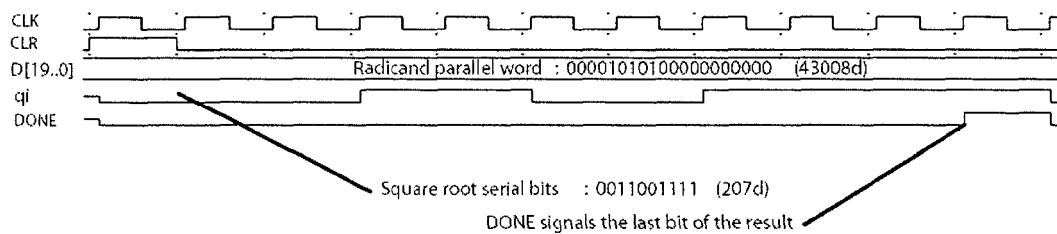

### 3.4 Division et Racine carrée

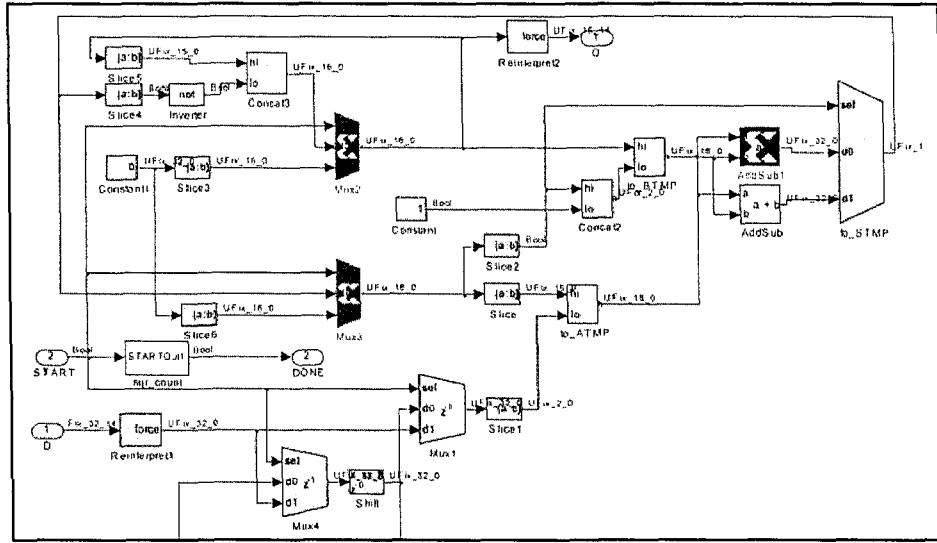

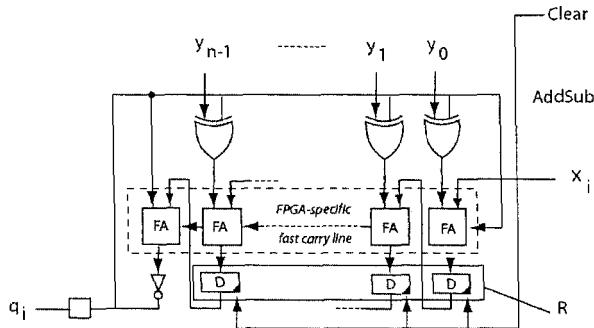

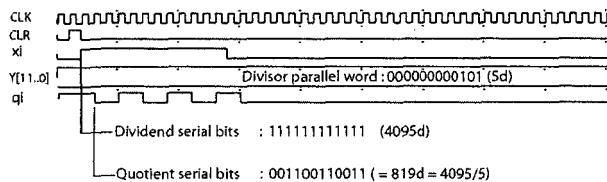

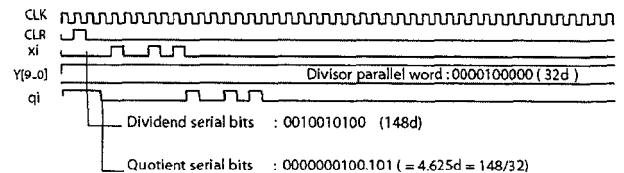

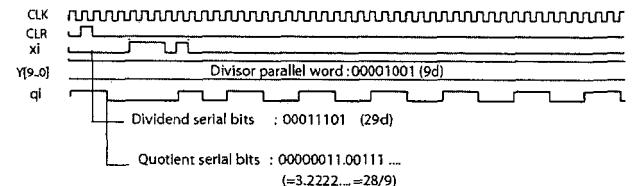

Il est possible d'utiliser une version non restaurante de la racine carrée et de la division afin de garder petite la taille du système et d'obtenir une meilleure précision. En effet, les opérations de division et de racine carrée fournies par XSG sont des implémentations CORDIC lourdes et peu précises. Après de nombreux tests en utilisant les versions 7, 8.1 et 8.2 de XSG (les résultats n'ont pas été vérifiés avec la nouvelle version 9), l'opération de racine carrée CORDIC de XSG ne donne qu'une grossière approximation du résultat lorsqu'une grande précision fractionnaire est demandée. De plus, la lourde implémentation de cette opération nécessite un long temps de synthèse lors de la génération d'un bloc co-simulé ou du fichier BIN pour des tests sur le terrain. Dans le cas du contrôle vectoriel, la précision offerte par l'opérateur racine carrée n'est pas suffisante, et le contrôle diverge. La division CORDIC offre pour sa part une précision très satisfaisante et permet le bon fonctionnement d'un algorithme comme le contrôle vectoriel. Cependant, sa grande taille et sa vitesse d'exécution moins grande peut la rendre moins intéressante pour une application très complexe qui nécessite déjà beaucoup de ressources du FPGA.

Les versions non restaurantes décrites dans l'annexe I de ces deux opérations offrent la précision désirée, mais elles ne peuvent pas recevoir plusieurs valeurs à traiter avant l'accomplissement de l'opération. Pour une valeur X à l'entrée de la racine carrée, il n'est pas possible de changer X pour une valeur Y tant que le résultat de la racine de X n'est pas obtenu. Heureusement, comme le contrôle vectoriel s'effectue très rapidement et s'insère confortablement entre deux échantillonnages, les versions non restaurantes peuvent être utilisées sans effet négatif. Les opérations sont complétées longtemps avant qu'un nouvel échantillonnage doive être traité. De plus, le nombre de pas nécessaire pour effectuer une racine carrée est coupé de moitié avec cette nouvelle implémentation, tandis que la division nécessite le même nombre de pas d'horloge.

Les tailles et performances des opérateurs sont comparées au tableau 2. Il s'agit de versions qui n'ont jamais été optimisées pour les FPGAs auparavant. Les schémas XSG des versions non restaurées créées dans XSG pour cette recherche se trouvent à l'annexe F.

| 32 bits (14 binary point) |                 |             |       |                     |                 |       |

|---------------------------|-----------------|-------------|-------|---------------------|-----------------|-------|

|                           | Sqrt NON CORDIC | Sqrt CORDIC | Diff. | Division NON CORDIC | Division CORDIC | Diff. |

| <i>Slices</i>             | 60              | 1377        | 2295% | 124                 | 1806            | 1456% |

| <i>FFs</i>                | 82              | 2289        | 2791% | 96                  | 3132            | 3263% |

| <i>BRAMs</i>              | 0               | 0           | n.a.  | 0                   | 0               | n.a.  |

| <i>LUTs</i>               | 103             | 2425        | 2354% | 218                 | 2981            | 1367% |

| <i>IOBs</i>               | 0               | 0           | n.a.  | 0                   | 0               | n.a.  |

| <i>Emb. Mults</i>         | 0               | 6           | 600%  | 0                   | 3               | 300%  |

| <i>TBUFs</i>              | 0               | 0           | n.a.  | 0                   | 0               | n.a.  |

| <i>Nbr. de pas</i>        | 24              | 51          | 213%  | 48                  | 47              | 98%   |

| <i>Vitesse</i>            | 238.112 MHz     | 58.666 MHz  | 25%   | 173.408 MHz         | 76.963 MHz      | 25%   |

tableau 2 - Tailles des opérateurs division et racine carrée

### 3.5 Portillonnage (délai d'activation et temps de maintien)

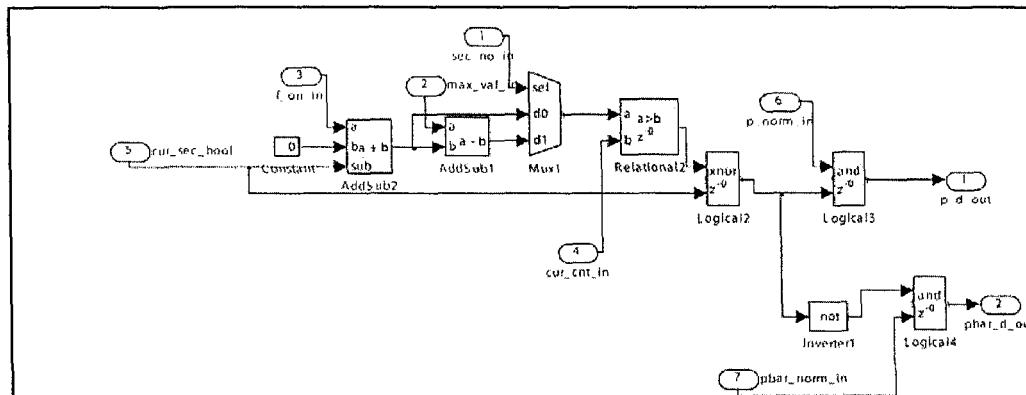

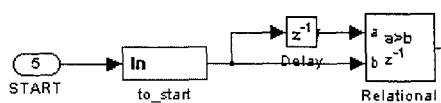

Les blocs de portillonnage précédemment implémentés à l'aide du bloc de fonction embarquée (voir section 2.2.2) dans Simulink sont maintenant créés avec XSG (figure 14 et figure 15).

figure 14 - Portillonage

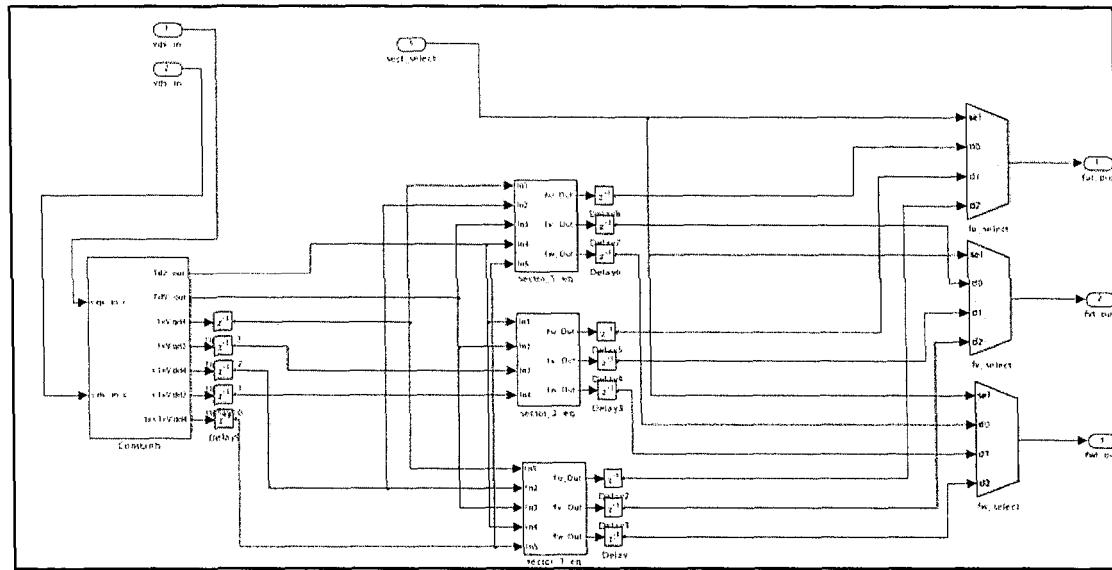

### figure 15 - Calcul des délais d'activation

Le calcul du temps mort (figure 16) qui s'effectue à l'intérieur du bloc de portillonage est basé sur un algorithme développé par OPAL-RT dans [9] et adapté à la situation de la recherche. Le fichier d'initialisation Matlab dicte le temps mort désiré avec la constante `dead_time`.

### figure 16 - Calcul du temps mort

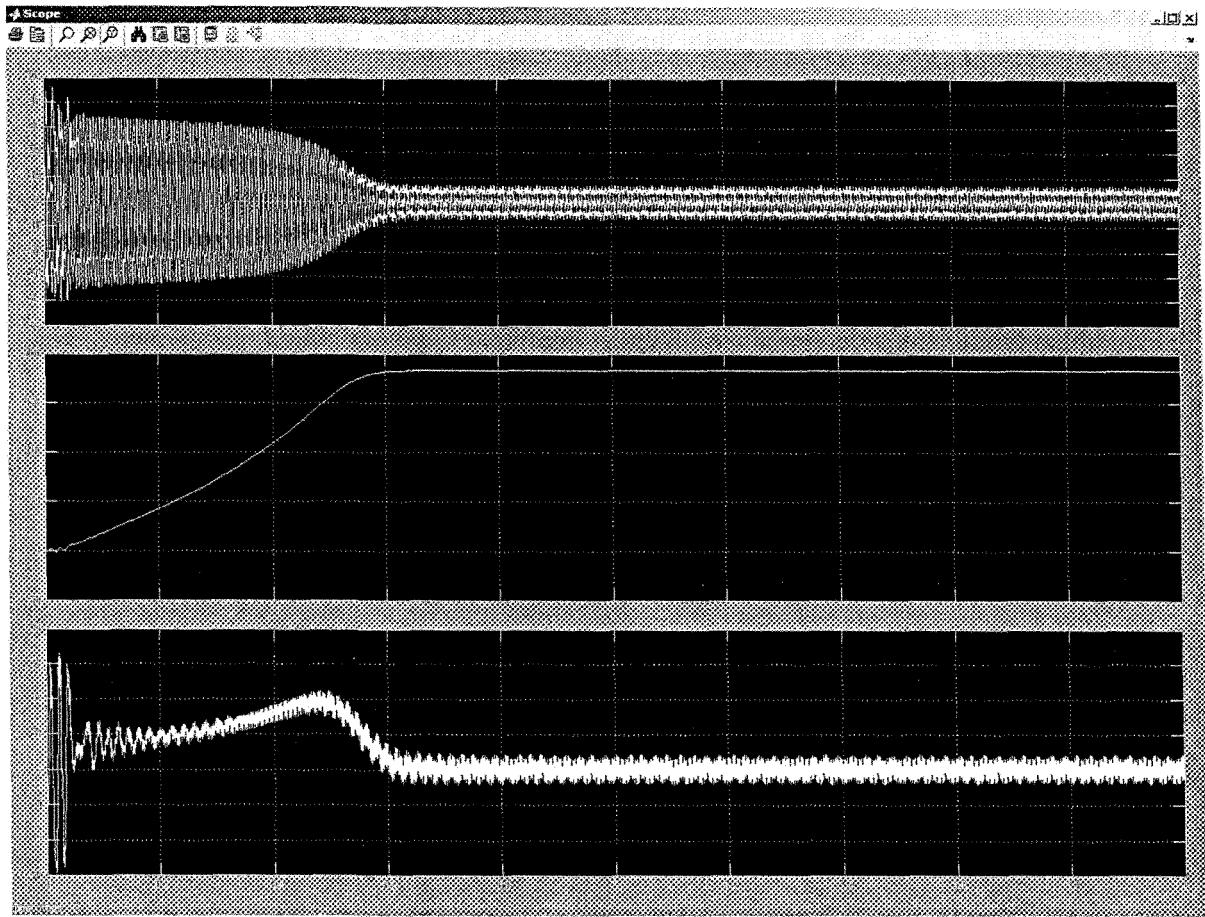

Afin de tester le bon fonctionnement du portillonnage avant son intégration au sein du projet entier, celui-ci est inséré dans un tutoriel fournit par SPS. Il remplace alors le portillonnage de base

s'y trouvant, et le débogage peut s'effectuer jusqu'à l'obtention d'une précision adéquate. Les résultats sont observables à la figure 17.

**figure 17 - Courants, vitesse et torque du moteur avec simulation du portillonnage XSG**

Le profil suivant donne les résultats de la figure 19.

```

freq=10;

Ua=0;Ub=0;

for k=Ts:Ts:3

Wref=2*pi*(freq/p);

if k > (0.3)

freq=30;

end

```

```

if k > (0.8)

freq=10;

end

if k > (1.7)

freq=50;

end

if k > (2.5)

freq=5;

end

```

figure 18 - Courants, vitesse et torque du moteur avec simulation du portillonnage XSG

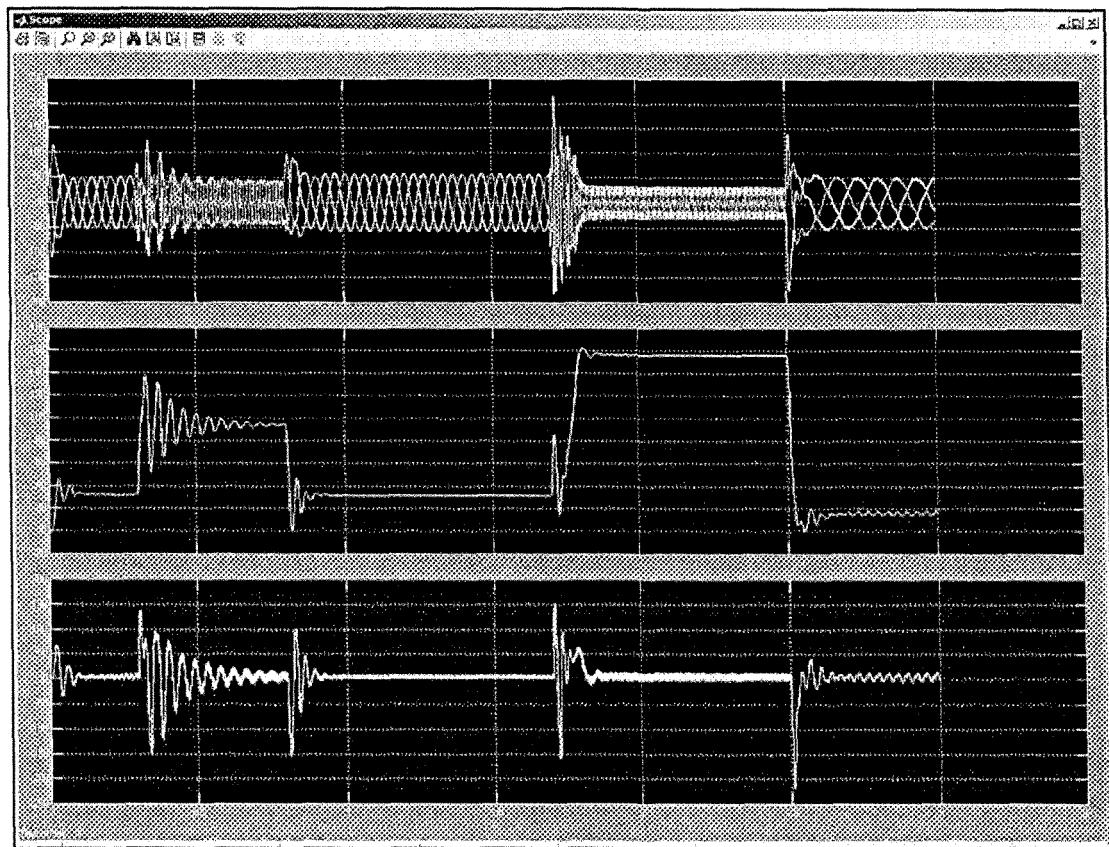

### 3.6 Lecture de vitesse provenant d'un encodeur optique

L'implémentation de la lecture de vitesse simple se trouve à la figure 19. Il s'agit d'un filtre simple qui calcule la vitesse moyenne pour une plage de temps spécifiée. Une implémentation beaucoup plus efficace décrite dans [12] sera éventuellement développée et testée avant d'effectuer des tests plus poussés en laboratoire. Pour des tests préliminaires et la vérification des connexions, cette méthode est suffisante.

figure 19 - Lecture de vitesse d'un encodeur optique (modèle simple)

## **CHAPITRE 4**

### **GAPPA et les outils de vérification XSG**

## 4.1 Introduction à GAPPA

Un outil fort intéressant appelé GAPPA (Génération Automatique de Preuves de Propriétés Arithmétiques) est développé au Laboratoire de l'Informatique du Parallelisme en France. Cet outil permet de vérifier et prouver les propriétés numériques de programmes qui font de l'arithmétique en virgule flottante et en point fixe. C'est ce dernier volet qui nous intéresse pour la présente recherche, car il s'agit du volet qui peut grandement réduire les temps de développement avec XSG (ou même un projet codé à la main en langage HDL).