UNIVERSITÉ DU QUÉBEC

MÉMOIRE

PRÉSENTÉ À

L'UNIVERSITÉ DU QUÉBEC À CHICOUTIMI

COMME EXIGENCE PARTIELLE

DE LA MAÎTRISE EN INGÉNIERIE

PAR

JEAN-JACQUES CLAR

**DÉVELOPPEMENT D'APPLICATIONS PARALLÈLES POUR UN**

**SYSTÈME MULTIPROCESSEUR EXPÉRIMENTAL**

Juillet 2002

### **Mise en garde/Advice**

Afin de rendre accessible au plus grand nombre le résultat des travaux de recherche menés par ses étudiants gradués et dans l'esprit des règles qui régissent le dépôt et la diffusion des mémoires et thèses produits dans cette Institution, **l'Université du Québec à Chicoutimi (UQAC)** est fière de rendre accessible une version complète et gratuite de cette œuvre.

Motivated by a desire to make the results of its graduate students' research accessible to all, and in accordance with the rules governing the acceptance and diffusion of dissertations and theses in this Institution, the **Université du Québec à Chicoutimi (UQAC)** is proud to make a complete version of this work available at no cost to the reader.

L'auteur conserve néanmoins la propriété du droit d'auteur qui protège ce mémoire ou cette thèse. Ni le mémoire ou la thèse ni des extraits substantiels de ceux-ci ne peuvent être imprimés ou autrement reproduits sans son autorisation.

The author retains ownership of the copyright of this dissertation or thesis. Neither the dissertation or thesis, nor substantial extracts from it, may be printed or otherwise reproduced without the author's permission.

*Nous ne devrions pas croire une chose uniquement parce qu'elle a été dite, ni croire aux traditions parce qu'elles ont été transmises depuis l'Antiquité; ni aux "on dit" en tant que tels; ni aux écrits des sages parce que se sont des sages qui les ont écrits; ni aux imaginations que nous supposons avoir été inspirées par un être spirituel; ni aux déductions tirées de quelque hypothèse hasardeuse que nous aurions pu faire; ni à ce qui paraît être une nécessité analogique; ni croire sur la simple autorité de nos instructeurs ou de nos maîtres.*

*Mais nous devons croire à un écrit, à une doctrine ou à une affirmation lorsque notre raison et notre expérience intime les confirment.*

*C'est pourquoi je vous ai enseigné à ne pas croire simplement d'après ce qui vous a été dit, mais conformément à votre expérience personnelle, et puis à agir en conséquence et généreusement.*

*Bouddha*

# Résumé

Un souci constant qui guide le développement de l'informatique est l'accélération des performances. Dans cette optique, une des solutions souvent utilisées réside en la mise en parallèle des traitements.

L'émergence, depuis quelques années, des applications multimédia et l'augmentation incessante de la complexité des systèmes pouvant être intégrés sur un circuit moteur rend possible l'apparition et le développement de DSP<sup>1</sup> de plus en plus complets, dédiés à certains traitements numériques intensifs. Les applications cibles traitent généralement une énorme quantité de données avec un nombre limité de fonctions. Ces traitements, souvent indépendants les uns des autres, peuvent être effectués en parallèle. Le but est d'exploiter le parallélisme dans les données de plusieurs algorithmes afin de les traiter nettement plus rapidement qu'avec un ordinateur séquentiel conventionnel.

Pour obtenir des applications à traitement parallèle performantes il faut effectuer une partition des algorithmes étudiés en assignant une partie du traitement à chacun des processeurs.

---

<sup>1</sup>DSP: Digital Signal Processors : Processeurs de Traitement de Signaux

Le projet PULSE, issu d'un groupe de recherche de l'École Polytechnique de Montréal, travaille au développement d'une architecture multiprocesseur de type SIMD<sup>2</sup> dédiée au traitement numérique en temps réel.

Le circuit intégré cible possède quatre processeurs dans sa première version. La seconde version doit inclure seize processeurs à l'intérieur du même circuit intégré.

Durant ce projet, sept applications numériques connues ont étées écrites en langage assembleur et optimisées sur la première version de **PULSE**. Les applications sont : multiplications vecteurs-matrice, algorithmes de cryptage RSA et IDEA, algorithme de Bresenham, modèle continu (poisson) et transformation binaire d'images (inclus érosion et dilatation d'images). Pour certaines de ces applications - multiplications vecteurs-matrice, algorithme de Bresenham et transformation binaire d'images – les résultats obtenus se comparent avantageusement avec les librairies déjà développées sur des circuits intégrés concurrents.

En plus des applications numériques ce projet à permis d'améliorer les différents outils de **PULSE** – documentation et simulateur –, ainsi que le modèle VHDL<sup>3</sup>.

---

<sup>2</sup>SIMD: **S**ingle **I**nstruction **M**ultiple **D**ata

<sup>3</sup>VHDL: **V**ery **H**igh **S**peed **I**ntegrated **C**ircuits) **H**ardware **D**escription **L**anguage

# Remerciements

Bon cette page sert à remercier tous les gens m'ayant enrichi de leurs précieuses aides.

Ce projet et le mémoire qui si rattache ont été complétés en 2 parties.

La première partie s'échelonne sur 2 années passées à compléter les cours et le travail de recherche à l'UQAC pour tenter d'accéder au titre de maître en ingénierie. Il s'agit de membres du GRM : Yvon Savaria pour sa passion, ses connaissances et naturellement ses dollars, pour leurs indispensables aides Normand Bélanger, Nicolas Contandriopoulos, Ivan Kraljic , Paul Marriott et Claude Villeneuve.

La seconde partie couvre le temps de rédaction. C'est avec plaisir que je présente de profonds remerciements aux personnes que j'ai emmerdées par mon indisponibilité durant les trois dernières années pour rédiger ce mémoire. Tout d'abord cette merveilleuse famille qui m'entoure et me suivrait au bout de la galaxie si cela peut aider l'accomplissement de notre destin, Caterpillar et Brian Funke pour les nuits passées sur mon portable au lieu de partager une bonne bière dans le hot tub à Tucson, Novell et Brian Misbach pour l'opportunité d'utiliser et de pousser mes connaissances sur les systèmes multiprocesseurs. Sonia, je te remercie pour avoir corrigé ma première version et aussi pour m'avoir dit que mon français était récupérable, peut-être...

Daniel Audet conservera toujours une place spéciale pour m'avoir fait confiance en me proposant ce projet, pour son aide et sa non-ingérence dans mon travail. Pour la rédaction de ce mémoire faisait-il preuve d'une patience sans limite, avait-il lancé la serviette ou tout bonnement il était trop occupé à faire des choses plus importantes que de me taper sur les doigts ?

# Table des Matières

|                                                                 |             |

|-----------------------------------------------------------------|-------------|

| <i>Résumé</i> .....                                             | <i>ii</i>   |

| <i>Remerciements</i> .....                                      | <i>iv</i>   |

| <i>Table des Matières</i> .....                                 | <i>vi</i>   |

| <i>Liste des encadrés</i> .....                                 | <i>x</i>    |

| <i>Liste des tableaux</i> .....                                 | <i>xi</i>   |

| <i>Liste des figures</i> .....                                  | <i>xiii</i> |

| <i>Liste des Annexes</i> .....                                  | <i>xv</i>   |

| <i>Chapitre 1 – INTRODUCTION GÉNÉRALE</i> .....                 | <i>1</i>    |

| 1.1. Préambule.....                                             | <i>2</i>    |

| 1.1.1. Le Multimédia .....                                      | <i>2</i>    |

| 1.2. Introduction au parallélisme .....                         | <i>4</i>    |

| 1.2.1. La Classification des Différents Types de Machines ..... | <i>5</i>    |

| 1.2.2. L'évolution de la quincaillerie.....                     | <i>7</i>    |

| 1.3. Projet de deuxième cycle.....                              | <i>9</i>    |

|                                                                     |           |

|---------------------------------------------------------------------|-----------|

| <b>1.4. Le projet PULSE .....</b>                                   | <b>10</b> |

| 1.4.1. Le Groupe .....                                              | 11        |

| 1.4.2. Interaction et Utilisation des Outils de Développement ..... | 12        |

| 1.4.3. Caractéristiques Générales de PULSE .....                    | 14        |

| 1.4.4. V1 versus V2 .....                                           | 25        |

| <b>1.5. Contribution du présent projet .....</b>                    | <b>26</b> |

| 1.5.1. Méthodologie du Projet .....                                 | 26        |

| <b>1.6. Présentation de la thèse .....</b>                          | <b>27</b> |

| <i>Chapitre 2 – REVUE DES SYSTÈMES EXISTANTS .....</i>              | <b>29</b> |

| <b>2.1. Préambule.....</b>                                          | <b>30</b> |

| <b>2.2. Introduction .....</b>                                      | <b>31</b> |

| 2.2.1. Description générale .....                                   | 31        |

| <b>2.3. Architecture .....</b>                                      | <b>35</b> |

| 2.3.1. CNAPS .....                                                  | 35        |

| 2.3.2. ‘C80 .....                                                   | 37        |

| 2.3.3. SHARC .....                                                  | 40        |

| 2.3.4. A236 .....                                                   | 42        |

| <b>2.4. Environnement de développement.....</b>                     | <b>44</b> |

| 2.4.1. CNAPS .....                                                  | 44        |

| 2.4.2. ‘C80 .....                                                   | 45        |

|                                                                        |            |

|------------------------------------------------------------------------|------------|

| 2.4.3. SHARC.....                                                      | 45         |

| 2.4.4. A236 .....                                                      | 45         |

| <b>2.5. Conclusion .....</b>                                           | <b>47</b>  |

| <i>Chapitre 3 – DÉVELOPPEMENT D'APPLICATIONS .....</i>                 | <i>49</i>  |

| <b>3.1. Préambule.....</b>                                             | <b>50</b>  |

| 3.1.1. Objectifs de développement .....                                | 50         |

| 3.1.2. Méthodologies adoptées .....                                    | 55         |

| 3.1.3. Environnement de développement .....                            | 58         |

| 3.1.4. Évaluation de la performance, du débit et de l'efficacité ..... | 59         |

| 3.1.5. Goulot d'étranglement.....                                      | 60         |

| <b>3.2. Applications développées .....</b>                             | <b>62</b>  |

| 3.2.1. Multiplication vecteurs - matrice.....                          | 62         |

| 3.2.2. Algorithme de Bresenham .....                                   | 82         |

| 3.2.3. Algorithme RSA .....                                            | 89         |

| 3.2.4. Équations aux différences finies (Poisson).....                 | 93         |

| 3.2.5. Morphologie Binaire : Érosion et Dilatation .....               | 98         |

| 3.2.6. IDEA.....                                                       | 104        |

| 3.2.7. Constat.....                                                    | 112        |

| <i>Chapitre 4 – ÉVALUATION DE LA PERFORMANCE .....</i>                 | <i>113</i> |

| <b>4.1. Préambule.....</b>                                             | <b>114</b> |

|                                                     |            |

|-----------------------------------------------------|------------|

| <b>4.2. Présentation des résultats .....</b>        | <b>115</b> |

| 4.2.1. Paramètres et mesures de développement ..... | 115        |

| 4.2.2. Banc d'essai .....                           | 115        |

| 4.2.3. Résultats.....                               | 119        |

| <b>4.3. Conclusion .....</b>                        | <b>130</b> |

| <i>Chapitre 5 - CONCLUSION .....</i>                | <i>131</i> |

| <b>5.1. Développement D'Applications .....</b>      | <b>133</b> |

| 5.1.1. Développement sur PULSE.....                 | 134        |

| 5.1.2. Test, Évaluation et Recommandation .....     | 136        |

| <b>5.2. Conclusion .....</b>                        | <b>142</b> |

| <i>Bibliographie.....</i>                           | <i>143</i> |

| <i>Annexe A - APPLICATIONS DÉVELOPPÉES.....</i>     | <i>147</i> |

| <i>Annexe B – OPÉRATION MODULO RAPIDE .....</i>     | <i>197</i> |

# Liste des encadrés

|                                                                                        |     |

|----------------------------------------------------------------------------------------|-----|

| Encadré 3.1 : Opérations : multiplication vecteur - matrice .....                      | 64  |

| Encadré 3.2 : Multiplication vecteurs-matrice, version de base .....                   | 68  |

| Encadré 3.3 : Multiplication vecteurs-matrice, données dans la mémoire interne .....   | 69  |

| Encadré 3.4 : Multiplication vecteur-matrice, version pseudo-systolique .....          | 72  |

| Encadré 3.5 : Multiplication vecteurs-matrice, version pseudo-systolique .....         | 79  |

| Encadré 3.6 : Opérations – utilisation nouvelle combinaison instruction parallèle..... | 80  |

| Encadré 3.7 : Bresenham - Pseudo-code.....                                             | 84  |

| Encadré 3.8 : Bresenham - Opérations – traitement d'un segment de droite.....          | 86  |

| Encadré 3.9 : Bresenham - Opérations : calcul position pixel .....                     | 87  |

| Encadré 3.10 : Poisson - Opérations : équation aux différences finies .....            | 95  |

| Encadré 3.11 : Morphologie - Opérations - morphologie binaire.....                     | 102 |

| Encadré 3.12 : Opérations de cryptage avec IDEA.....                                   | 105 |

# Liste des tableaux

|                                                                                     |     |

|-------------------------------------------------------------------------------------|-----|

| Tableau 1.1 : Classification de Flynn.....                                          | 5   |

| Tableau 1.2 : Latence - Instructions d'exceptions .....                             | 17  |

| Tableau 3.1 : Vecteurs – Matrice - Organisation des données, mémoire d'entrée ..... | 66  |

| Tableau 3.2 : Vecteurs – Matrice - Traitement des données dans chaque UT .....      | 67  |

| Tableau 3.3 : Vecteurs – Matrice - Traitement des données dans chaque PE .....      | 70  |

| Tableau 3.4 : Vecteurs – Matrice - Nombre de cycles par vecteur .....               | 74  |

| Tableau 3.5 : Vecteurs – Matrice - Nombre de cycles par vecteur .....               | 81  |

| Tableau 3.6 : Cryptage avec IDEA – Opérations récursives .....                      | 109 |

| Tableau 3.7 : Cryptage avec IDEA – Opérations finales .....                         | 110 |

| Tableau 4.1 : Présentation des Résultats .....                                      | 119 |

| Tableau 4.2 : Goulots d'étranglements .....                                         | 120 |

| Tableau 4.3 : Multiplication vecteurs – matrice – traitement de 200 vecteurs .....  | 122 |

| Tableau 4.4 : Bresenham – traitement de 50 vecteurs de 10 pixels .....              | 123 |

| Tableau 4.5 : Cryptage -Performance – traitement de $10^6$ caractères .....         | 123 |

|                                                                                           |     |

|-------------------------------------------------------------------------------------------|-----|

| Tableau 4.6 : Poisson, simulation d'une maille de 32 x 32 = 1024 PEs .....                | 123 |

| Tableau 4.7 : Morphologie Mathématique - Performance (128 x 128 image).....               | 124 |

| Tableau 4.8 : Morphologie Mathématique - Performance (256 x 256 image).....               | 124 |

| Tableau 4.9 : Relation entre calcul et efficacité .....                                   | 125 |

| Tableau 4.10 : Facteur d'accélération Sp et Efficacité Ep .....                           | 126 |

| Tableau 4.11 : Multiplication vecteurs – matrice, nombre de vecteurs traités .....        | 127 |

| Tableau 4.12 : Bresenham - Comparaison avec <i>UWICL</i> (50 segments de 10 pixels) ..... | 128 |

| Tableau 4.13 : RSA – Comparaison ( $10^6$ caractères de 8 bits) .....                     | 129 |

| Tableau 4.14 : Morphologie Binaire - Comparaison avec <i>UWICL</i> (512 x 512 images).... | 129 |

| Tableau 5.1 : Liste des recommandations et limitations rencontrées.....                   | 137 |

# Liste des figures

|                                                                              |    |

|------------------------------------------------------------------------------|----|

| Figure 1.1 : Modèle SIMD avec Mémoires Distribuées .....                     | 7  |

| Figure 1.2 : Membres du groupe PULSE.....                                    | 11 |

| Figure 1.3 : PULSE - Environnement d'Opération - exemple.....                | 14 |

| Figure 1.4 : Caractéristiques générales de l'architecture de PULSE .....     | 21 |

| Figure 1.5 : PULSE - Entrées et sorties des données .....                    | 22 |

| Figure 1.6 : PULSE - Canaux de communications et traitement des données..... | 23 |

| Figure 1.7 : PULSE - Élément de calcul et étapes d'exécution .....           | 24 |

| Figure 2.1 : Sous-système CNAPS .....                                        | 32 |

| Figure 2.2 : CSC et CNAPS-10xx avec connexions .....                         | 36 |

| Figure 2.3 : Bloc diagramme du 'C80 .....                                    | 38 |

| Figure 2.4 : Bloc diagramme du SHARC .....                                   | 41 |

| Figure 2.5 : Bloc diagramme du A236.....                                     | 43 |

| Figure 3.1 : Pipeline de PULSE .....                                         | 53 |

| Figure 3.2 : Décomposition d'un algorithme .....                             | 57 |

|                                                                                         |     |

|-----------------------------------------------------------------------------------------|-----|

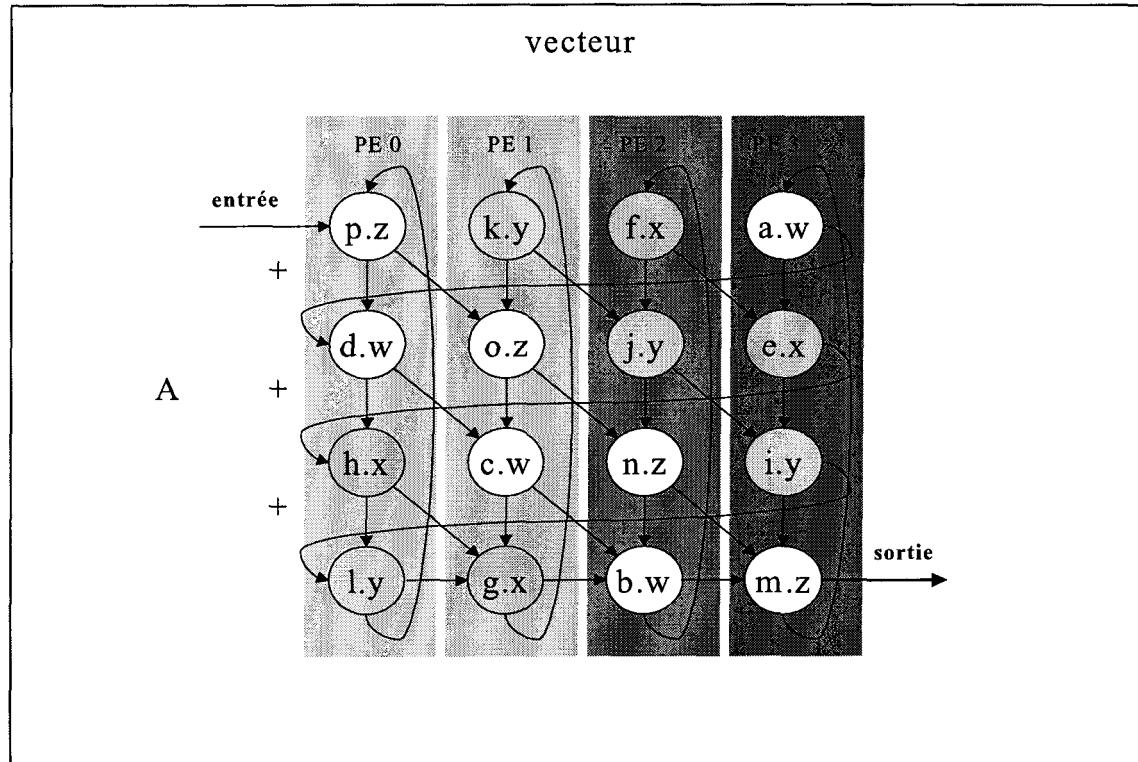

| Figure 3.3 : Vecteurs – Matrice - Mouvement de données et opérations .....              | 71  |

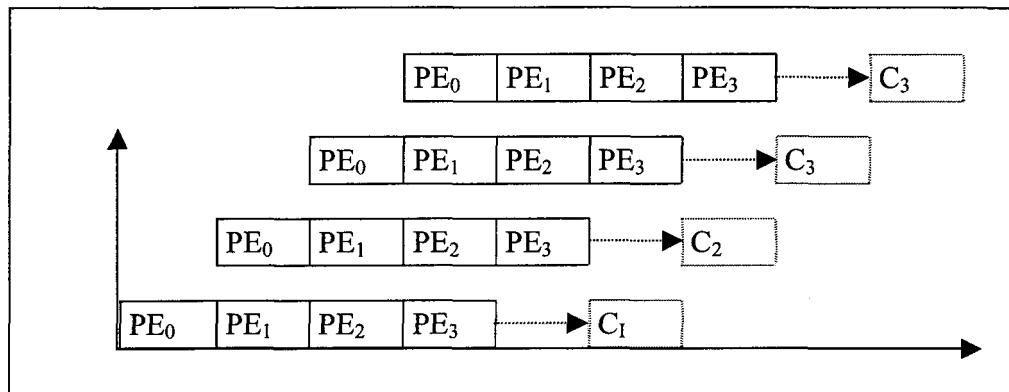

| Figure 3.4 : Vecteurs – Matrice - Remplissage du pipeline et sortie des résultats ..... | 75  |

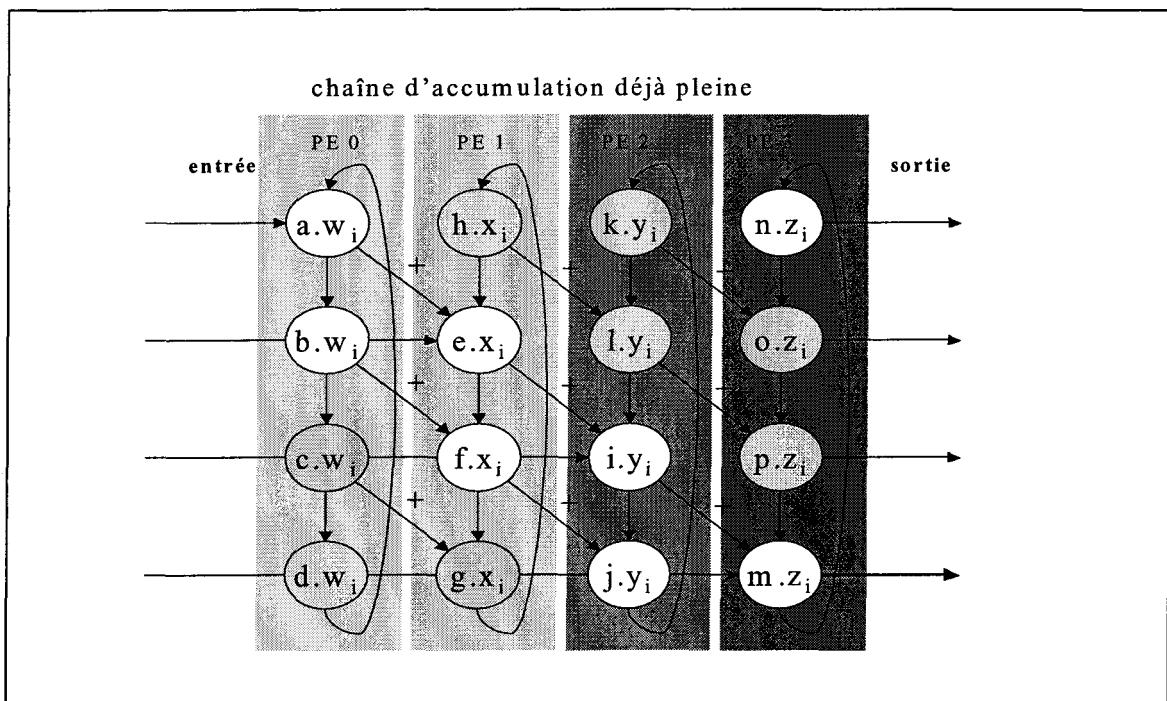

| Figure 3.5 : Entrée des données, opérations et sortie des résultats .....               | 77  |

| Figure 3.6 : Vecteurs – Matrice - Décomposition basée sur l'architecture .....          | 78  |

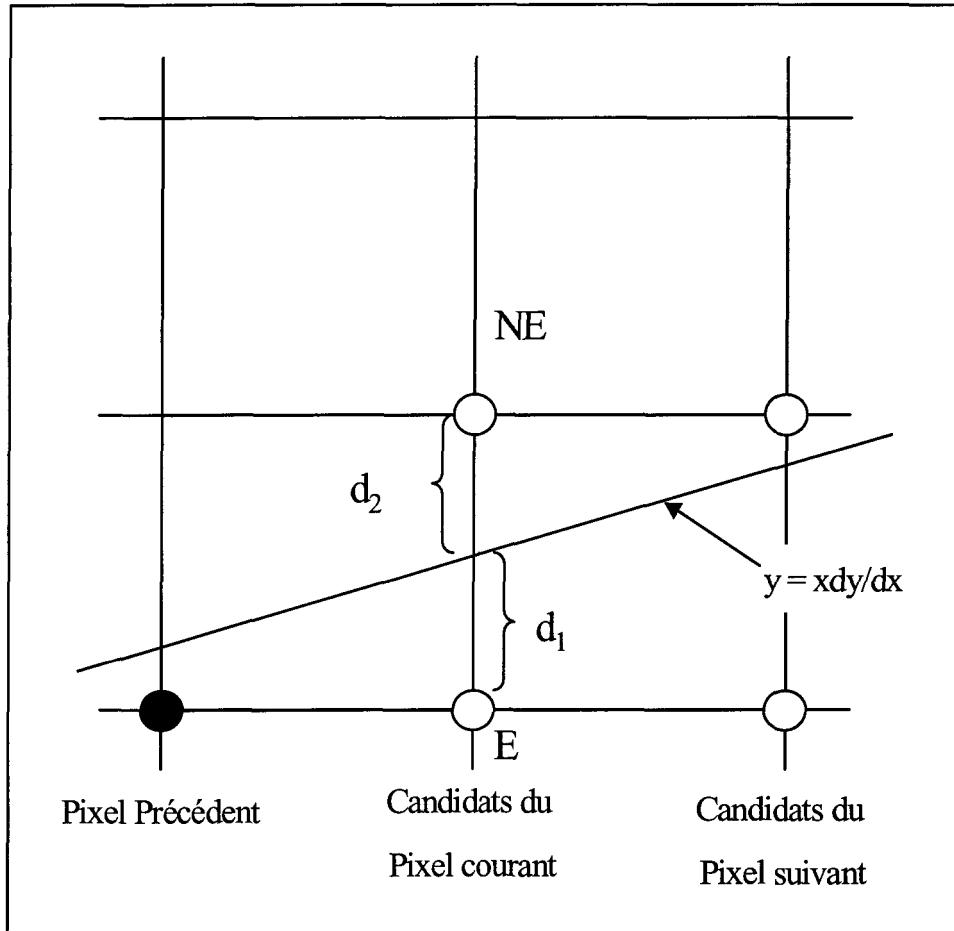

| Figure 3.7 : Bresenham - Traçage de lignes.....                                         | 83  |

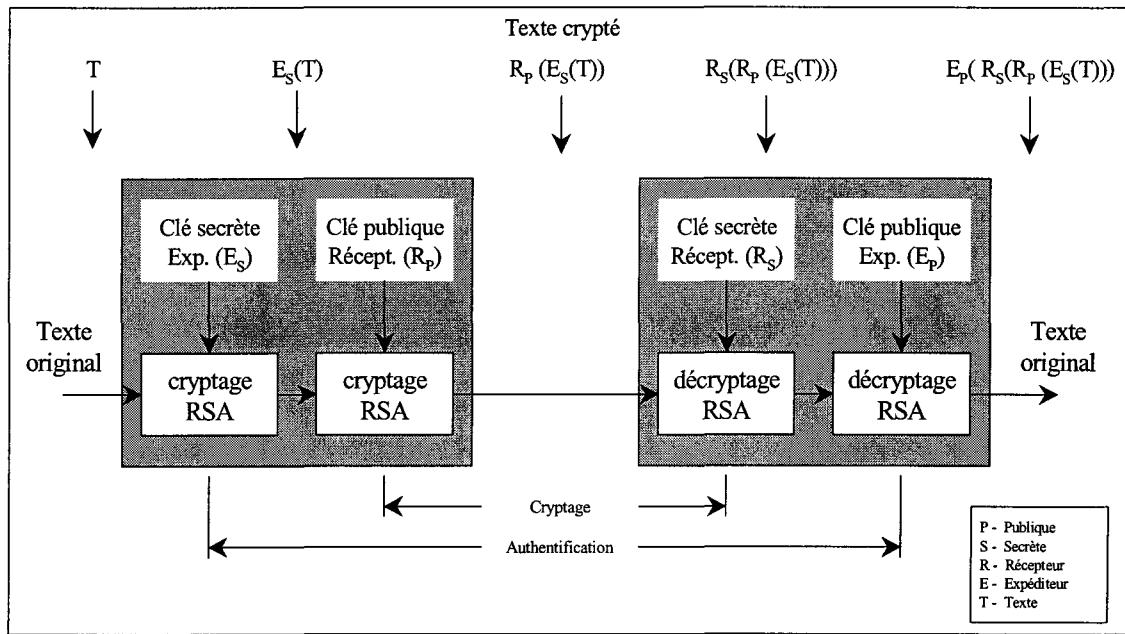

| Figure 3.8 : RSA - Authentification et Cryptage de message .....                        | 90  |

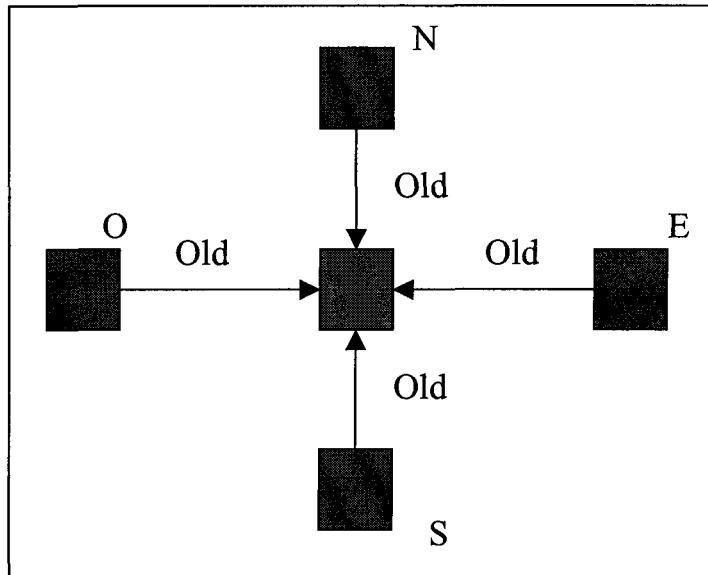

| Figure 3.9 : Poisson - Voisinage nodal .....                                            | 94  |

| Figure 3.10 : Poisson - Correspondance Maille – PE .....                                | 96  |

| Figure 3.11 : Morphologie - Correspondance Pixel – PE .....                             | 99  |

| Figure 3.12 : Morphologie - Colonne supplémentaire de 0 (zéro).....                     | 99  |

| Figure 3.13 : Morphologie - Mouvement de données et calcul .....                        | 101 |

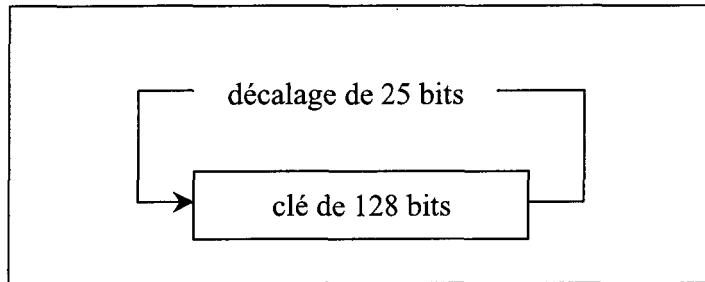

| Figure 3.14 : IDEA - Création des clés dérivées.....                                    | 105 |

## Liste des Annexes

|                                           |     |

|-------------------------------------------|-----|

| Annexe A - APPLICATIONS DÉVELOPPÉES ..... | 147 |

| Annexe B – OPÉRATION MODULO RAPIDE .....  | 197 |

## CHAPITRE 1

### *INTRODUCTION GÉNÉRALE*

## 1.1. PRÉAMBULE

### 1.1.1. Le Multimédia

À ce jour, le développement d'applications multimédias pour commercialisation présente de sérieuses barrières pour les concepteurs et les utilisateurs. Les CPUs<sup>4</sup> d'aujourd'hui (mais peut-être pas ceux de demain) font preuve de lacune au point de vue performance pour traiter de façon simultanée le graphisme, le son, la vidéo et les communications en temps réel. L'objectif étant de produire avec le plus de réalisme possible les applications multimédias.

Les applications multimédias de haute qualité, surtout les jeux, nécessitent une énorme puissance de traitement. Par exemple, un simple microprocesseur standard est incapable de façon simultanée d'interpréter des images en 3-D, de générer du son de qualité CD, de reconnaître la parole et de détecter les mouvements sur un affichage plein écran le tout de façon synchrone. Chacun de ces processus accapare une partie de la puissance de traitement du processeur maître, diminuant du même coup le pourcentage de la puissance totale disponible pour les autres tâches. Le tout se continue jusqu'à atteindre 100% de la puissance de traitement des composantes en places. Chacune des tâches initiées subséquemment gruge sur les tâches déjà en cours créant un ralentissement perceptible par l'utilisateur ; images saccadées, sorties sonores interrompues, décalage entre les différentes tâches, ...

---

<sup>4</sup> Central Processing Unit

---

---

---

---

Si toutes ces opérations peuvent être aujourd'hui, avec un niveau de performance raisonnable, traitées dans un seul système multimédia, c'est grâce à un support externe au processeur principal.

**Comment cela se fait-il ?**

Différents microprocesseurs, avec de multiples DSPs incorporés sur des cartes, s'occupent de mener à bien certaines des tâches de façon individuelle afin d'appuyer le processeur maître. Ces cartes sont conçues pour un groupe de tâches spécifiques souvent très coûteuses en temps processeur, ce qui résulte en une configuration optimale sans se soucier de généralisation comme le processeur principal. Le processeur maître peut déléguer une partie des tâches en cours et concentrer sa puissance sur les tâches restantes.

Plusieurs entreprises dont les noms sont aujourd'hui renommés, se partagent ce marché qui s'élève à plus de *1 milliard de dollars US* par année.

Un des critères principaux pour pouvoir pénétrer ce marché et y survivre, est le degré d'accélération des performances afin d'augmenter la rapidité de traitement des applications. Dans cette optique, une des solutions matérielles proposées réside dans le traitement parallèle des applications.

---

---

---

## 1.2. INTRODUCTION AU PARALLÉLISME

Les premiers ordinateurs furent tous des machines séquentielles. L'architecture de ces ordinateurs séquentiels s'inspire du modèle de von Neumann. Depuis l'avènement du premier ordinateur, les machines de type von Neumann ont vu leur puissance de calcul considérablement augmenter, sans pour autant pouvoir satisfaire la demande. L'apparition du parallélisme, dans les processeurs d'abord et ensuite dans les ordinateurs, est liée à deux principes.

- 1. La puissance de calcul.** La course à la puissance de calcul est la première raison de l'apparition du parallélisme. Quelle que soit la vitesse à laquelle la puissance des processeurs augmente, il existe toujours une limite courante de puissance qui est le plus souvent d'ordre technologique, liée, par exemple, à la capacité d'intégration des circuits. Pour augmenter encore la puissance des machines, il y a deux solutions. Atteindre un progrès technologique qui permet d'accroître la complexité et la vitesse des circuits intégrés, ou bien introduire un nouveau concept : le parallélisme. En effet, même s'il n'est pas possible à cause de limitations technologiques d'effectuer une opération plus rapidement sur un processeur, rien ne nous empêche d'exécuter plusieurs opérations sur plusieurs processeurs simultanément.

- 2. Le coût.** La seconde raison est d'ordre économique. Il est très important de pouvoir produire des machines ayant un excellent rapport coût/performance. Or, assez souvent, l'accroissement de la puissance d'un élément de calcul entraîne

---

---

---

une explosion des coûts et le prix de l'élément devient alors prohibitif. En revanche, il est possible d'atteindre de grandes puissances de calcul à des coûts compétitifs en faisant coopérer de nombreux éléments de calcul de moyenne ou faible puissance. La puissance des différents éléments étant compensée par leur nombre.

### 1.2.1. La Classification des Différents Types de Machines

Flynn [FLYN66] considère une machine de von Neumann comme étant une machine qui utilise un unique flot d'instructions et qui travaille sur un unique flot de données. Le terme anglais consacré est celui de **SISD** (Single Instruction, Single Data). Il est possible d'introduire le parallélisme en multipliant les flots d'instructions et/ou les flots de données. Nous obtenons alors les quatre classes de machines suivantes.

|                     |          | Flot de données    |                               |

|---------------------|----------|--------------------|-------------------------------|

|                     |          | Unique             | Multiple                      |

| Flot d'instructions | Unique   | SISD (von Neumann) | SIMD (tableau de processeurs) |

|                     | Multiple | MISD (pipeline)    | MIMD (multiprocesseurs)       |

**Tableau 1.1 : Classification de Flynn**

Le sujet de recherche de cette thèse a été effectué sur une machine de type SIMD. Les informations qui suivent s'appliquent directement au type de modèle et d'architecture utilisés à l'intérieur du présent projet.

---

---

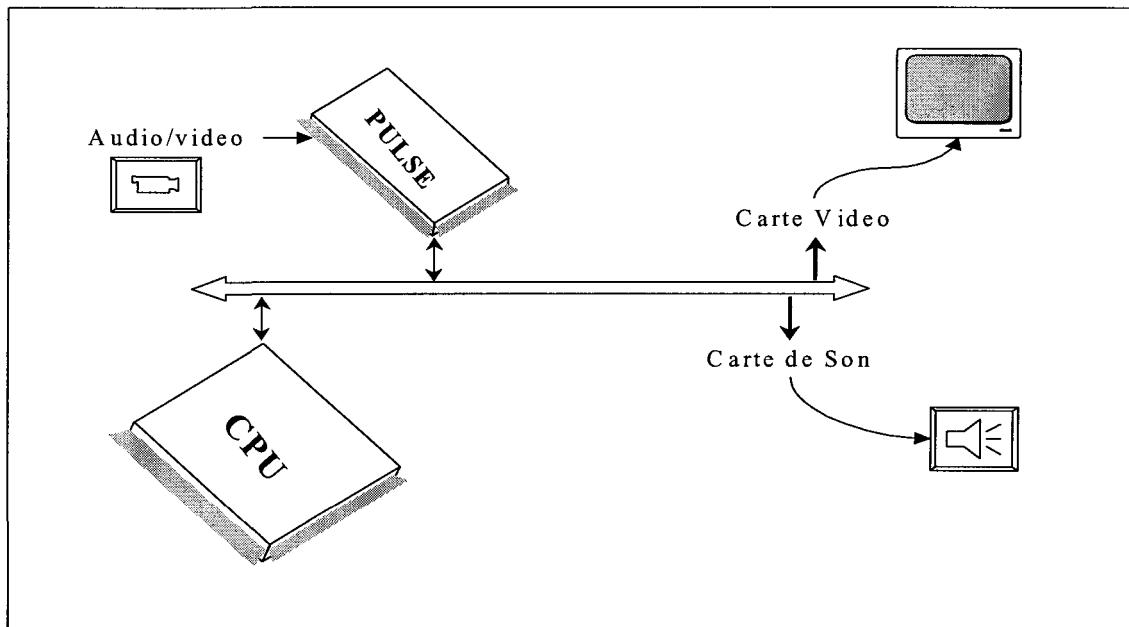

- **SIMD** - Dans une machine SIMD, il existe une seule unité de contrôle qui dirige tous les éléments de calcul, chaque élément de calcul travaillant sur une donnée qui lui est propre. Ce type de machine est souvent appelé tableau de processeurs (array processors). Les données traitées par chaque élément de calcul peuvent se trouver dans un espace de mémoire qui est global à toute la machine ou dans des espaces mémoire propres aux différents éléments de calcul. Dans le cas de **PULSE**, chaque élément de calcul opère sous le contrôle d'un séquenceur externe.

Il est maintenant possible d'introduire une classification des différents types de machines basée sur l'organisation de la mémoire. Les données peuvent se trouver dans une mémoire partagée ou distribuée.

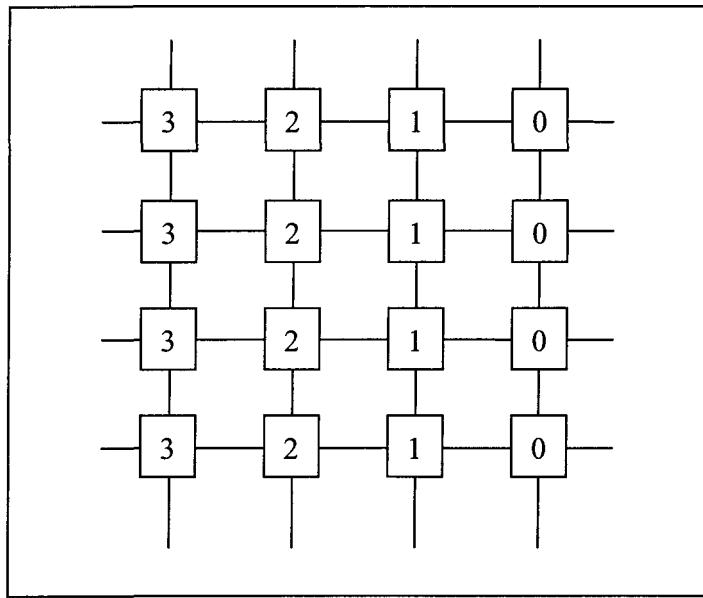

La classe des machines SIMD avec une mémoire distribuée est caractérisée par un contrôle centralisé et des données distribuées. Les processeurs d'une machine de ce type sont souvent appelés *éléments de calcul* (processing elements), abrégé par *PE*. Les *PEs* ne disposent pas d'un séquenceur mais sont contrôlés par l'extérieur. La puissance de calcul de la machine parallèle est obtenue par le très grand nombre de *PE* utilisés. Chaque processeur possède une petite mémoire locale et reçoit ses instructions d'un unique séquenceur de sorte que tous les *PE* exécutent la même instruction de manière synchrone (figure 1.1).

---

---

**Figure 1.1 : Modèle SIMD avec Mémoires Distribuées**

Un mécanisme de masquage permet de définir un sous-ensemble de processeurs, appelé ensemble de processeurs actifs, qui sont les seuls à exécuter l'instruction courante. Les processeurs inactifs ne font rien, en attendant que l'ensemble des processeurs actifs ait terminé l'instruction. Nous verrons plus tard en étudiant les différentes applications que c'est le cas lorsqu'une instruction conditionnelle est employée. Les communications entre les processeurs sont réalisées à l'aide d'instructions spécifiques via un réseau de communication.

### 1.2.2. L'évolution de la quincaillerie

L'augmentation incessante de la complexité des systèmes pouvant être intégrés sur un circuit rend possible le développement de DSPs de plus en plus complets. La loi de Moore<sup>5</sup>,

---

<sup>5</sup> Gordon E. Moore, Intel Corporation co-fondateur

---

---

qui tient depuis 1965, prédit que le nombre de transistors à l'intérieur d'une puce double environ à chaque année. L'émergence, depuis quelques années, des applications multimédia motive et finance ce développement. Ces DSPs sont dédiés à certains traitements numériques intensifs. Les DSPs cibles traitent généralement une énorme quantité de données souvent avec un nombre limité de fonctions. Même Intel, avec sa famille de processeurs Pentium, a ajouté un jeu d'instructions limitées de type SIMD à compter de sa technologie MMX au début de 1997. Par la suite, l'arrivée des processeurs Pentium III et 4 incluait de nouvelles technologies, SSE<sup>6</sup> et SSE2, avec pour but d'étendre l'utilisation de la technologie SIMD.

---

<sup>6</sup> Streaming SIMD Extensions

### **1.3. PROJET DE DEUXIÈME CYCLE**

Ce projet de recherche a été effectué en collaboration avec le Groupe de Recherche en Micro-électronique (GRM) de l'École Polytechnique de Montréal. Le projet de deuxième cycle consistait à participer à l'évaluation matérielle et logicielle d'un système multiprocesseur expérimental développé par le GRM. Le projet du GRM a comme nom **PULSE**.

---

---

#### **1.4. LE PROJET PULSE**

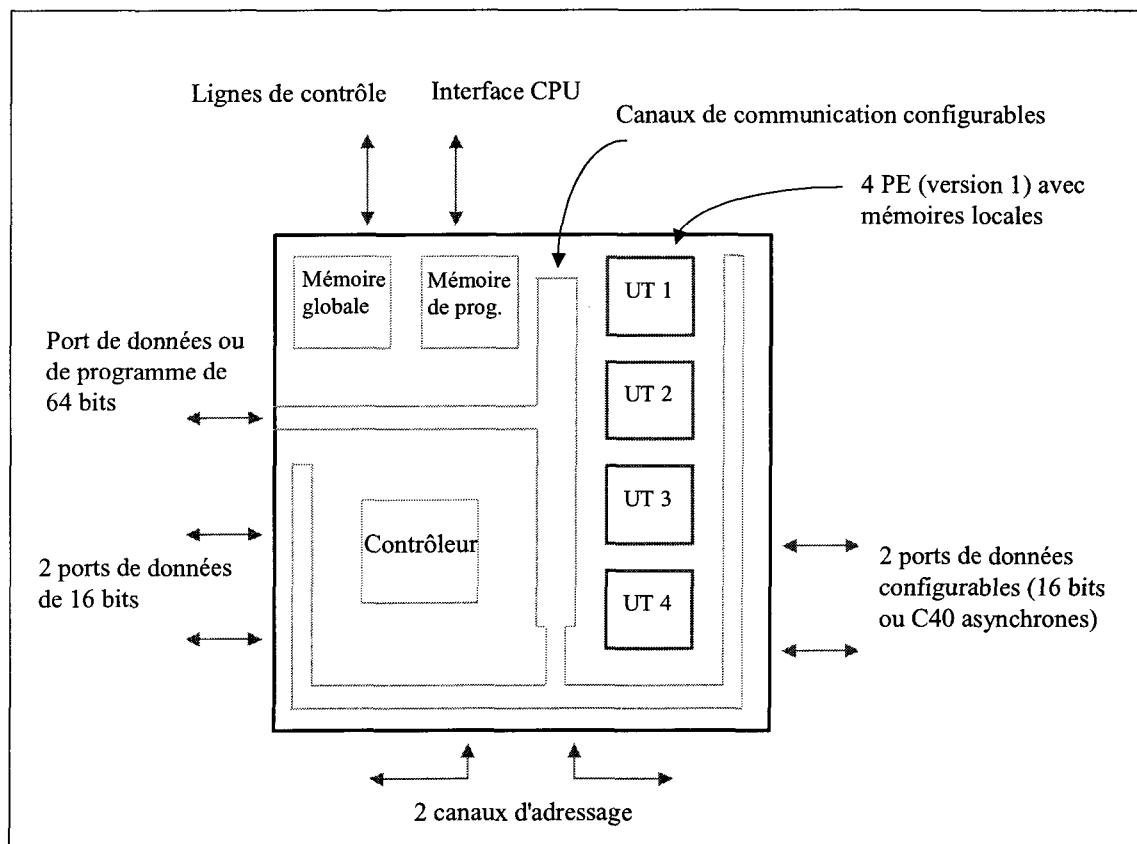

L'acronyme **PULSE** vient de Parallel Ultra Large Scale Engine qui signifie un moteur de traitement utilisant des unités parallèles avec une intégration ULSI. Le circuit intégré développé par le Groupe est un processeur de type SIMD.

---

---

### 1.4.1. Le Groupe

Le Groupe **PULSE** comptait, à une certaine époque de son développement, près d'une quarantaine de membres des milieux universitaires et privés (voir figure 1.2). Notre participation s'est échelonnée de janvier 1997 à mai 1998.

Figure 1.2 : Membres du groupe **PULSE**

---

#### 1.4.2. Interaction et Utilisation des Outils de Développement

Le début de notre participation à l'intérieur du Groupe a coïncidé avec la disponibilité de la première version du simulateur logiciel de **PULSE**. Le simulateur a été l'outil principal de développement d'applications utilisé tout au long de ce projet. Le simulateur était basé sur le modèle **VHDL** de **PULSE**. Il n'était pas exportable, il a donc résidé sur un serveur à l'intérieur des locaux du Groupe à l'École Polytechnique de Montréal tout au long du projet. L'accès au simulateur s'est effectué via l'interface du fureteur Netscape.

Au mois d'octobre 1997 une première version portable du simulateur a été utilisée sur UNIX. Malgré l'absence d'interface graphique, ce simulateur a grandement aidé l'avancement des travaux grâce à sa rapidité d'exécution.

À partir de ce moment, les deux simulateurs ont été utilisés conjointement pour tester et développer les différentes applications. Voici leurs caractéristiques principales et les différents aspects de l'utilisation de l'un ou l'autre.

##### Modèle VHDL :

- Interface graphique : visualisation des résultats d'opérations dans les composantes principales du processeur, opérations pas à pas, production de résultats de performances.

- Modèle *assez* stable à partir de sa disponibilité, en fait, à part quelques exceptions les résultats d'exécutions étaient justes. Des défectuosités et des temps d'indisponibilités ont cependant été rencontrées en cours de développement.

---

---

---

---

- Exécution lente : un simulateur pour le groupe, temps d'obtention des résultats directement proportionnel au nombre d'utilisateurs et à la rapidité du réseau, alors qu'il est inversément proportionnel à la puissance du serveur. Mise à jour après plusieurs semaines d'utilisation d'un problème de configuration d'une composante de réseau du GRM ralentissant atrocement le transfert de données entre l'hôte du modèle **VHDL** et le monde extérieur.

#### **Modèle exportable :**

- Possibilité de produire des fichiers résultats

- Rapide d'exécution (dépend seulement de la performance du processeur hôte)

- Limite sur l'utilisation de certaines instructions et mode d'adressages.

- Simulateur expérimental, utilisé à partir de sa disponibilité à l'intérieur du groupe.

Certaines anomalies se sont révélées durant son utilisation.

L'avantage majeur du simulateur exportable était sa rapidité d'exécution des programmes développés permettant ainsi de vérifier leur opération au fur et à mesure.

En résumé, le simulateur exportable a été utilisé pour tester, développer et déverminer de façon générale les applications. Alors que le modèle **VHDL** a été utilisé pour fins de validation, pour caractériser la performance des différentes applications et lorsque le déverminage demandait un travail plus en profondeur

Lors de la fin de mon association avec le Groupe **PULSE**, une version complètement remodelée du simulateur **VHDL** s'annonçait disponible dans les semaines suivantes.

---

---

---

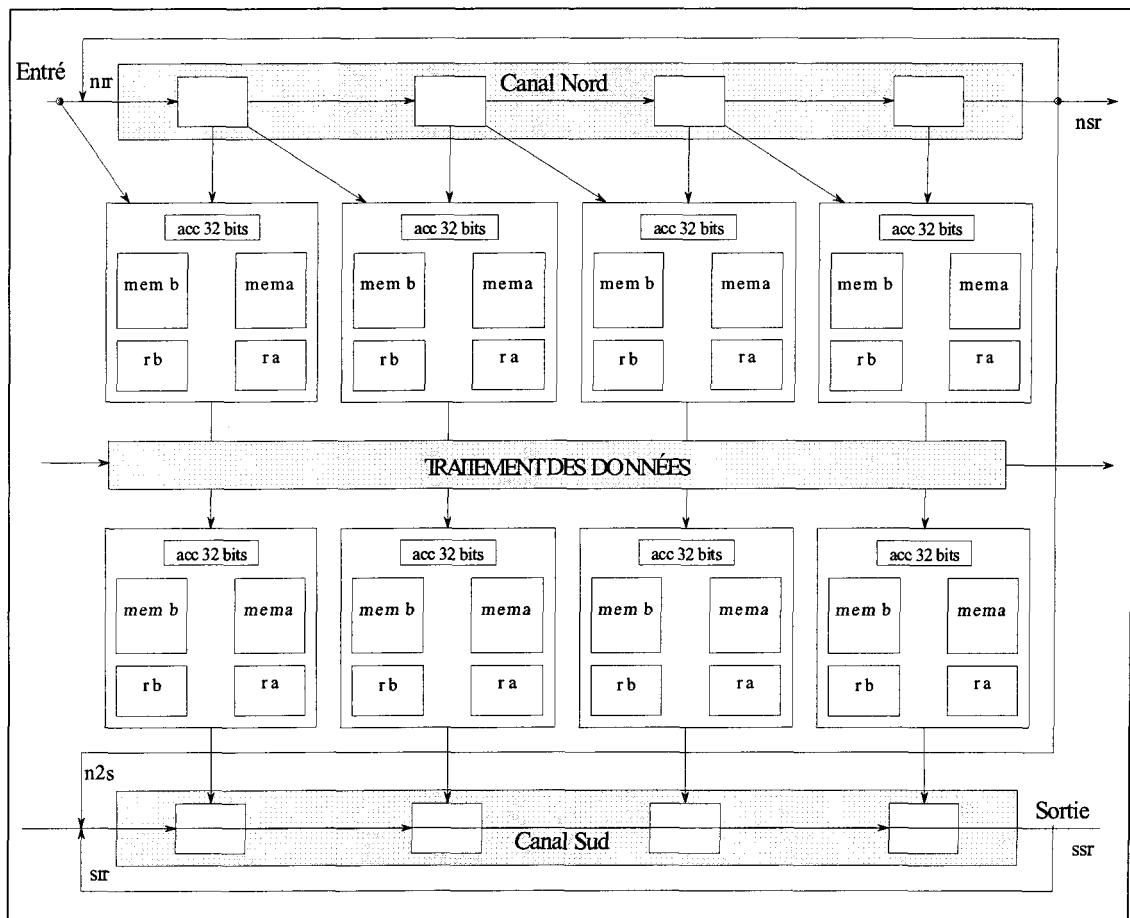

### 1.4.3. Caractéristiques Générales de PULSE

**PULSE V1** est la première mise en œuvre du circuit intégré **PULSE**. Ce chapitre donne une brève description des caractéristiques principales de l'architecture, de l'environnement de développement et du jeu d'instructions.

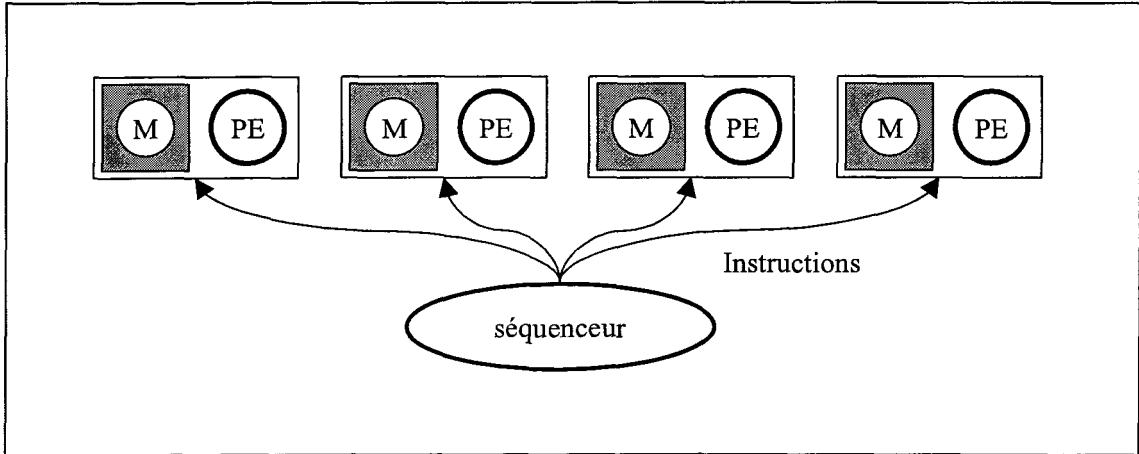

#### 1.4.3.1. Environnement d'Opération

**PULSE V1** est un processeur contenant 4 éléments de calcul de 16 bits à virgule fixe et un contrôleur. **PULSE V1** a été conçu comme support pour effectuer des opérations répétitives sur un nombre élevé de données. Sa conception découle des besoins définis par certains domaines d'application comme le traitement d'images et de vidéos. La figure 1.3 montre un exemple d'environnement pour **PULSE**.

Figure 1.3 : PULSE - Environnement d'Opération - exemple

---

---

#### 1.4.3.2. Caractéristiques du Jeu d'Instruction

Le jeu d'instruction de **PULSE** a été développé conjointement avec l'architecture du processeur. Il possède des caractéristiques directement liées aux applications cibles pour lesquelles il a été conçu. La mise en œuvre d'instructions non-linéaires spéciales (maximum, minimum, médian,..) en est un exemple.

De plus **PULSE** possède la possibilité de pouvoir employer des instructions parallèles. Les différentes instructions disponibles sont confidentielles au moment du dépôt de cette thèse. Pour en savoir plus sur le jeu d'instructions; contacter Yvon Savaria du Groupe de Recherche en Micro-électronique.

#### Mise en Parallèle des Instructions

Ces instructions permettent de maximiser à l'intérieur d'une seule instruction l'utilisation de diverses composantes de la puce avec 4 niveaux d'opérations parallèles [4] possibles :

**traitement numérique||mouvement de données||communication||E/S contrôle**

#### exemple:

**macc \*mcar(1), ra1 || fwd nport, \*mcbw(2) || ssr || io \*mccr%, \*mcdw%**

Cette ligne effectue les opérations suivantes : multiplication - addition, transfère une donnée du canal Nord à la mémoire B, fait un mouvement de données sur le port Sud et effectue une entrée/sortie de donnée sur les ports externes.

---

---

---

Ces instructions, en plus de multiplier le nombre d'instructions possibles par ligne de code, occupent moins d'espace dans la mémoire interne du processeur. Une variété limitée de combinaisons d'instructions est disponible dans le cas de **PULSE V1** alors que pour **V2** toutes les combinaisons possibles seront utilisables.

### **Mode d'Adressage**

**PULSE** supporte cinq différents type de mode d'adressage. Ces cinq types d'adressage accordent un accès aux données provenant des registres, de la mémoire, des ports de communications et directement de l'instruction.

- Registre

- Direct

- Indirect

- Immédiat

- Adressage absolu

Une description des différents modes d'adressage, avec exemples, est disponible dans [PULS97].

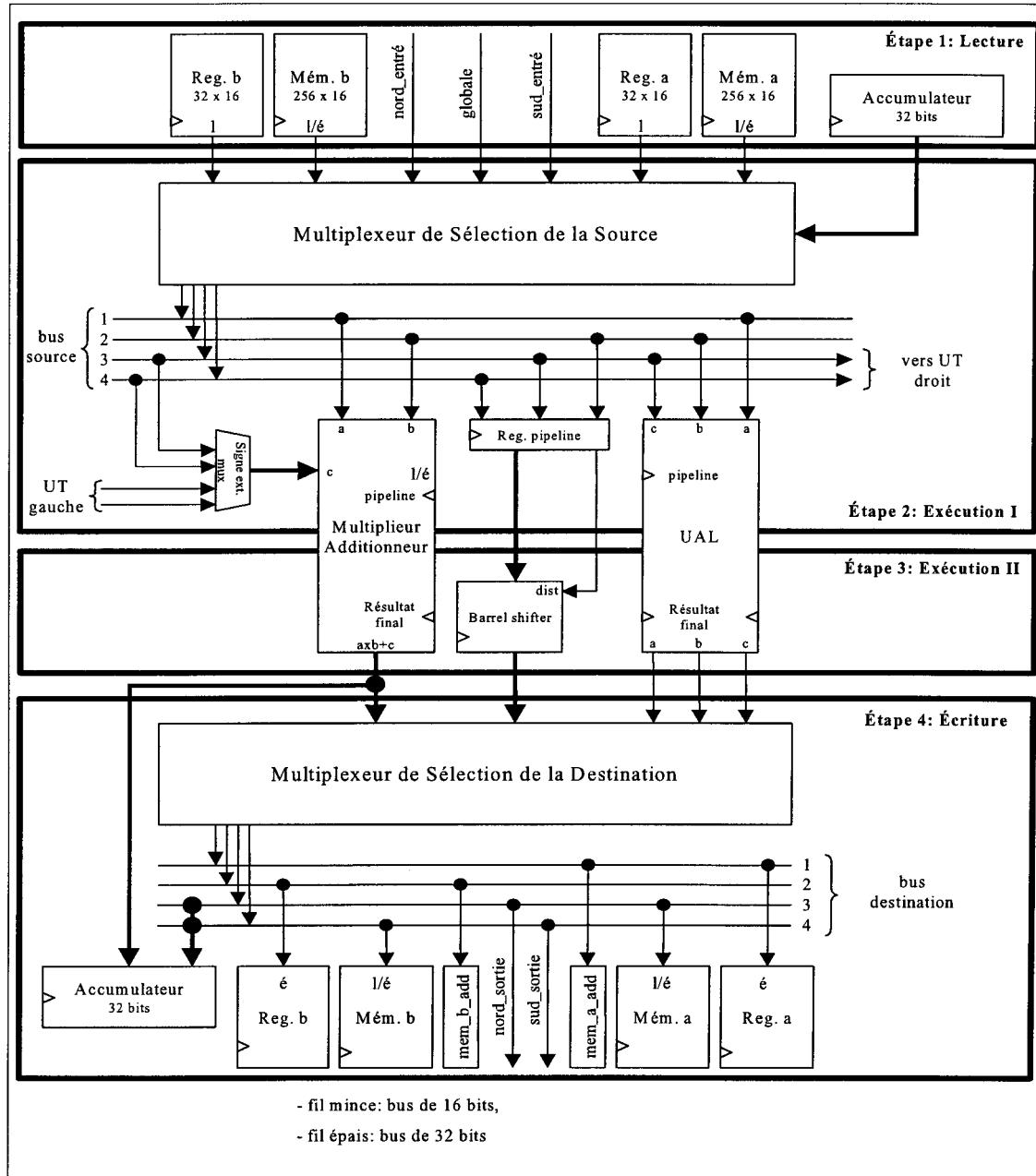

### **Temps de Latence des Opérations : Normal et Exception**

La majorité des instructions du langage **PULSE** nécessitent quatre cycles avant de produire un résultat utilisable par une autre instruction. Les exceptions se trouvent dans le tableau 1.2. Les figures des sections suivantes permettent de se faire une meilleure idée de l'architecture.

---

---

---

---

Les instructions d'exception sont les suivantes :

| Instruction     | Description Générale                                                                                                                | Latence (Cycles) |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------|

| <i>fwd</i>      | Avance une donnée des registres Nord ou Sud dans la mémoire A ou B.                                                                 | 1                |

| <i>io</i>       | Communication d'Entré/Sortie utilisant les compteurs modulo externes C et/ou D.                                                     | 1                |

| <i>nrr</i>      | Rotation des données des registres Nord vers la droite.                                                                             | 1                |

| <i>nsr</i>      | Décalage des données des registres Nord vers la droite.                                                                             | 1                |

| <i>nsrr</i>     | Rotation des données des registres Nord et Sud vers la droite.                                                                      | 1                |

| <i>n2ssr</i>    | Décalage des valeurs sur les ports de communication Nord et Sud simultanément avec les 2 ports agissant comme un seul port continu. | 1                |

| <i>stc</i>      | Copie les données de mémoire A ou B sur le canal de communication Nord ou Sud.                                                      | 2                |

| <i>srr</i>      | Rotation des données des registres Sud vers la droite.                                                                              | 1                |

| <i>ssr</i>      | Décalage des données des registres Sud vers la droite.                                                                              | 1                |

| <i>sla, sra</i> | Décalage arithmétique gauche, droit                                                                                                 | 2                |

Tableau 1.2 : Latence - Instructions d'exceptions

L'instruction *ld* en est une particulièrement dérangeante. Cette instruction charge une valeur dans l'accumulateur, un port de communication ou un registre d'adresse. Intuitivement en comparant cette instruction avec le *fwd*, nous pouvions espérer effectuer cette opération en un cycle au lieu des quatre cycles actuels.

---

---

---

## **Branchement : Latence et pénalité**

### **Instructions Conditionnelles**

L'emploi d'instructions conditionnelles est extrêmement coûteux dans le cas d'une machine SIMD. Comme vu précédemment, cette machine ne peut qu'effectuer la même opération sur chacun de ses éléments de calcul à chaque cycle d'horloge. **PULSE** possède la possibilité de pouvoir désactiver les éléments de calcul ne remplissant pas la condition testée, pendant que les autres effectuent les opérations comprises dans la première partie du bloc conditionnel. Durant la seconde partie du bloc, le *else*, les éléments de calcul actifs sont désactivés pendant que les autres effectuent les opérations à l'intérieur du second bloc conditionnel.

Chaque bloc conditionnel nous ampute d'une partie de notre puissance de traitement en plus d'introduire le délai nécessaire à la résolution de l'instruction conditionnelle.

**PULSE** contient une pile servant à suivre l'activité des éléments de calcul dans le cas de l'utilisation d'instructions conditionnelles. À l'aide de cette pile, **PULSE** supporte les instructions conditionnelles imbriquées.

Selon [GOOR89] les branchements constituent entre 15 et 25 % de toutes les instructions exécutées.

Dans le cas de **PULSE**, toutes les parties d'un bloc d'instructions conditionnelles sont exécutées. Un avantage à cette situation est de pouvoir commencer à exécuter les instructions suivant la directive conditionnelle de façon préemptive sans savoir si l'élément de calcul est à bord ou non. La préemption ne fonctionne par contre qu'à moitié, le

---

compilateur se charge d'insérer deux (2) cycles vide (*NOP*) entre le *if* et l'instruction suivante au lieu des quatre (4) nécessaires à son exécution. L'explication en est que la quincaillerie doit utiliser ces deux (2) cycles afin de se positionner pour le traitement de ce type d'instruction.

Le fait d'effectuer chacun des blocs d'une structure de contrôle nous amène à poser la question suivante :

Et si aucun des éléments de calcul ne remplit les conditions d'exécution ?

Dans ce cas le bloc est exécuté mais tourne à vide puisque tous les éléments de calcul sont désactivés. Le jeu d'instruction de **PULSE** possède une solution à ce problème de branchement : l'utilisation d'une instruction de branchement conditionnelle : *bnpa* (branch no PEs active). Il faut par contre payer un prix élevé ; quatre (4) cycles vide pour permettre au *if* de fournir sa réponse.

En résumé :

- Deux (2) *NOPs* si on utilise la préemption,

- Quatre (4) *NOPs* si on vérifie l'activité des éléments de calcul.

La morale de cette histoire :

Utiliser le moins possible les instructions conditionnelles.

---

---

---

---

### Boucle

Chaque boucle est caractérisée en langage assembleur par une instruction conditionnelle de branchement (*dbr* : decrement & branch) à la fin du groupe d'instructions compris à l'intérieur de la boucle. Pour tenir le pipeline occupé, **PULSE** entame, à chaque tour de boucle, l'exécution de l'instruction suivant le *dbr*. Il est payant au niveau performance de prendre en considération et de tirer avantage de cette caractéristique en déplaçant une instruction du corps de boucle à la suite du *dbr*, si possible.

### 1.4.3.3. Caractéristiques de l'Architecture

#### Caractéristiques Générales

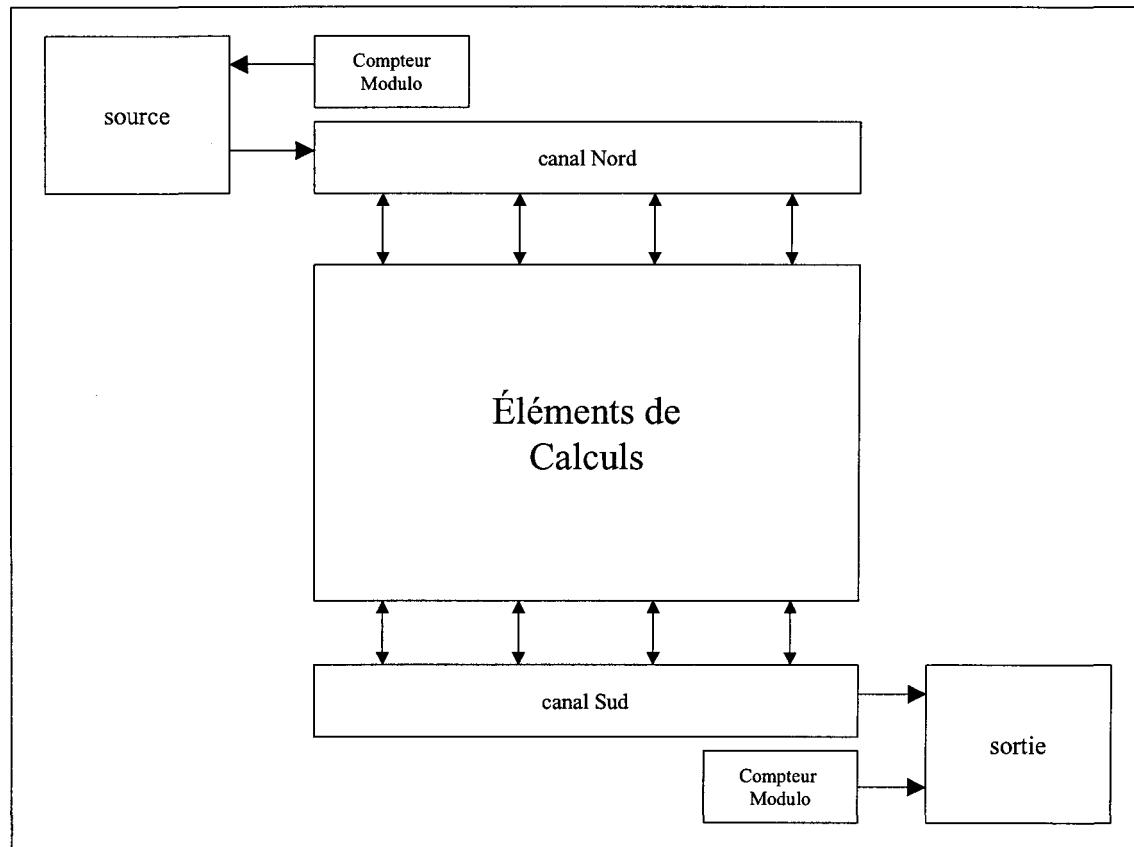

La figure 1.4 présente un bloc diagramme de haut niveau de l'architecture de **PULSE** ainsi que ses canaux de communications externes.

Figure 1.4 : Caractéristiques générales de l'architecture de PULSE

### Entrées et Sorties des données

La figure 1.5 présente les canaux de communications pour la circulation des données entre les éléments de calculs, les canaux Nord et Sud et les mémoires source et destination.

**Figure 1.5 : PULSE - Entrées et sorties des données**

### Canaux de Communications et Traitement des Données

La figure 1.6 représente par un bloc diagramme les options de communications possibles entre les canaux Nord et Sud et les mémoires internes des éléments de calculs.

Figure 1.6 : PULSE - Canaux de communications et traitement des données

### Élément de Calcul

La figure 1.7 présente les différentes étapes du pipeline d'exécution de PULSE.

Figure 1.7 : PULSE - Élément de calcul et étapes d'exécution

#### 1.4.4. V1 versus V2

De la création à l'aboutissement commercial d'un projet comme celui-ci, il existe plusieurs itérations.

Un second modèle de **PULSE** a vu le jour dans les derniers mois de 1997. **PULSE V2** comporte 16 processeurs et améliore certaines limitations de V1.

Le développement et la validation du présent projet ont été faits entièrement sur **PULSE V1**. Les différentes applications développées ont été évaluées de façon théorique sur V2, dans certains cas, à partir des caractéristiques techniques fournies par le groupe de développement.

---

---

## **1.5. CONTRIBUTION DU PRÉSENT PROJET**

Ce projet avait au départ deux objectifs principaux :

1. Développement d'applications et répartition de ces dernières sur **PULSE**,

2. Test et évaluation des outils en place et apporter, si possible, des suggestions pour améliorer le produit.

### **1.5.1. Méthodologie du Projet**

Afin de pouvoir poursuivre ces deux objectifs, le projet s'est divisé en 5 étapes :

1. Étude de la documentation existante sur **PULSE**.

2. Étude des différents compétiteurs sur le marché.

3. Initiation au parallélisme.

4. Familiarisation avec le langage et l'architecture à l'aide d'une première application.

5. Recherche et développement de différentes applications.

Les trois premières étapes se sont chevauchées à l'intérieur des premiers mois du projet pour permettre d'aboutir avec une première application. La majeure partie du temps consacré au projet a porté sur la cinquième étape avec de multiples itérations sur la première étape.

---

---

## 1.6. PRÉSENTATION DE LA THÈSE

La présente thèse comporte deux parties distinctes :

1. Une étude succincte des principaux joueurs sur le marché visé, cette partie est couverte à l'intérieur du prochain chapitre.

2. Les applications développées dans le cadre de ce projet.

- Le chapitre 3 décrit les applications et la façon dont leurs partitions se sont effectuées sur l'architecture de **PULSE**.

- Le chapitre 4 montre les résultats (performance) obtenus pour chacune des applications développées. On y présentera aussi une comparaison des temps d'exécution de certaines applications avec d'autres processeurs.

- Le chapitre 5 partage les «bonnes» et les «mauvaises» applications et présente la conclusion et les recommandations.

---

---

## CHAPITRE 2

### *REVUE DES SYSTÈMES EXISTANTS*

---

## 2.1. PRÉAMBULE

Quatre compétiteurs du processeur **PULSE** sont étudiés dans ce chapitre. Il s'agissait ainsi d'avoir une idée générale de ce que la compétition avait développé, de quelle façon elle attaquait le marché et quelles étaient les différences majeures avec **PULSE**.

Trois des compétiteurs sont : le **CNAPS**<sup>7</sup> de Adaptive Solutions, le **TMS320C80**(‘C80) de Texas Instruments et le **SHARC**<sup>8</sup> de Analog Devices. Tous étaient disponibles sur le marché lors de la rédaction de ce document. Le dernier, le **A236** de Oxford Micro Devices Inc. devait avoir un prototype disponible à la fin d'avril 1997. Le produit manufacturé devait être disponible vers le milieu de la même année.

De fait, mis à part le **CNAPS**, chacun à sa manière tend à avoir sur le même circuit intégré un système le plus complet possible. Il s'agit d'une combinaison d'éléments spécifiques orientés vers des applications requérant une grande quantité de traitements, comme **PULSE**. Ces traitements sont souvent indépendants les uns des autres, ils peuvent être effectués en parallèle. Le but est d'exploiter le parallélisme dans les données de plusieurs algorithmes afin de les traiter nettement plus rapidement qu'avec un ordinateur série. Tous ces DSPs sont censés être entièrement programmables, donc versatiles dans leur domaine d'application.

---

<sup>7</sup> « Co-processing Node Architecture for Parallel Systems »

<sup>8</sup> « Super Harvard Architecture Computer »

---

## 2.2. INTRODUCTION

Le but de cet exercice était d'avoir un premier contact avec les circuits intégrés prénommés et aussi d'essayer d'entrevoir la philosophie derrière chacune des conceptions. Je voulais aussi faire en partie le tour des informations contenues dans le tableau 1 du document *PULSE VI Overview*. Ce tableau compare les fonctionnalités de ces quatre compétiteurs avec **PULSE**. Un autre objectif était de situer chacun des processeurs dans son environnement, tant au niveau logiciel que matériel.

### 2.2.1. Description générale

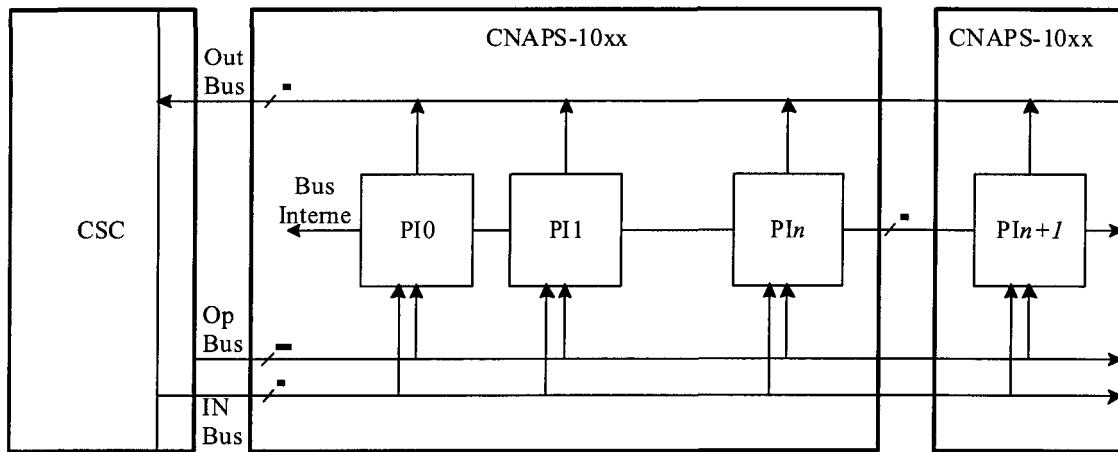

#### 2.2.1.1. CNAPS

Le **CNAPS** est le plus ancien des quatre compétiteurs, sa mise en marché remonte à la première moitié de 1994. Sa conception diffère des autres circuits intégrés en ce sens que le *CNAPS-10xx* qui est le cœur du système, n'est pas un système complet. *Le CNAPS-10xx* est fait de plusieurs processeurs mis en parallèle et interconnectés à l'intérieur du même circuit intégré. Il doit être couplé à d'autres éléments pour pouvoir être opérationnel. Un autre circuit intégré, le *CNAPS Sequencer Chip* (SCS), est nécessaire comme unité de contrôle pour gérer les instructions et les données. La figure 2.1 illustre de quelle façon sont reliés les différents éléments.

---

---

Le **CNAPS** est un système de 32 bits SIMD opérant à une fréquence de 20 MHz. Deux modèles du **CNAPS-10xx** sont manufacturés ; le 1016 (16 processeurs internes) et le 1064 (64 processeurs internes). Les processeurs sont tous à virgule fixe. Il est possible de mettre jusqu'à 8 **CNAPS-10xx** en parallèle.

Figure 2.1 : Sous-système CNAPS

Le **CNAPS** peut être programmé en langage C ou en assembleur et il possède des outils de développement sur UNIX et sur PC.

### 2.2.1.2. 'C80

Le 'C80' est un processeur 32 bits MIMD de type RISC avec une horloge de 50 MHz. Le circuit intégré du 'C80' inclut cinq processeurs programmables, un contrôleur de transfert et un contrôleur pour la vidéo. Il possède une mémoire interne de 50 Kb.

---

Quatre des cinq processeurs sont identiques, il s'agit de DSP en configuration MIMD.

Le cinquième processeur, le processeur maître, est un processeur 32 bits de type RISC. Il inclut une unité à virgule flottante. Les quatre autres processeurs sont à virgule fixe.

L'accès aux modules de mémoires internes se fait à l'aide d'un réseau d'interconnexion de type Cross-bar.

Les cinq processeurs peuvent être programmés en langage C et en langage d'assemblage. Le 'C80 possède des outils de développement sur station de travail seulement.

#### 2.2.1.3. SHARC

Le **ADSP-2106x SHARC** est un processeur 32 bits à virgule flottante avec une architecture de type Harvard. Dans ce cas-ci également, deux modèles sont disponibles, l'**ADSP-2100** et l'**ADSP-21062**. La seule différence entre les deux circuits est la quantité de mémoire interne. L'**ADSP-2100** a une SRAM de 4 mégabits et l'**ADSP-21062** à moitié moins, soit 2 mégabits.

Contrairement aux autres processeurs, les puces de la famille ADSP-210x intègrent un processeur unique. Le **SHARC** doit sa rapidité à l'organisation de sa mémoire. Le **SHARC** peut être programmé en C ou en assembleur. Ses outils de développement sont utilisables sur PC seulement. Pour avoir un système multiprocesseur, il faut mettre plusieurs SHARC en parallèle.

---

---

#### 2.2.1.4. Oxford A236

Nommé aussi par la compagnie Oxford le **PDSP<sup>9</sup>**, il est le dernier arrivé sur le marché de tous les DSP identifiés dans ce document.

Le **A236** est un processeur SIMD fonctionnant avec une vitesse d'horloge maximale de 50 MHz. Le circuit intégré du **A236** inclut quatre processeurs 16 bits à virgule fixe de type RISC avec un processeur scalaire de 24 bits qui sert de contrôleur.

Le A236 possède une mémoire interne de 2 K octets. Il peut être programmé en langage C et en assembleur mais, comme dans le cas du **SHARC**, il ne peut être utilisé que sur un PC.

---

<sup>9</sup> Parallel Video Signal Processor Chip

---

## 2.3. ARCHITECTURE

### 2.3.1. CNAPS

#### 2.3.1.1. Le CSC

Le **CSC** est une unité externe chargée de contrôler les processeurs internes du ou des **CNAPS-10xx**. Sa tâche principale est de gérer l'ordre d'exécution des instructions du programme. Il se sert du bus de commande (Op Bus) pour faire parvenir les instructions aux processeurs.

Le **CSC** a aussi comme fonction de contrôler les bus d'entrées et de sorties (In et Out Bus) des processeurs parallèles. Il est aussi responsable de toutes les connexions avec l'environnement externe.

Le **CSC** est composé de trois unités principales : une unité d'interface avec le bus d'interconnexion, une unité de décodage et d'exécution des instructions (circuit séquentiel) et une unité de contrôle et de synchronisation des E/S du **CNAPS-10xx**. Une **UAL** et des registres internes de 32 bits sont utilisés conjointement par ces trois unités. La figure 2.2 présente un schéma des connexions reliant le **CSC** et multiple **CNAPS-10xx**.

Le circuit intégré du CSC possède 240 broches.

---

---

Figure 2.2 : CSC et CNAPS-10xx avec connexions<sup>10</sup>

### 2.3.1.2. Le CNAPS-10xx

Chaque processeur interne (PI) possède une mémoire locale de 4 K octets avec les composantes standards d'un processeur mathématique soit : un additionneur, un multiplicateur, une unité logique, 32 registres de 16 bits et des tampons d'E/S.

La communication inter-processeur se fait au moyen d'un bus de 4 bits ( 2 bits d'entrée, 2 bits de sortie). La dimension de ce bus indique clairement que son utilisation est restreinte à de rares cas.

Un système CNAPS peut être composé de un à huit circuits intégrés comportant chacun 16 ou 64 processeurs. Si on multiplie ces nombres, on arrive à un total possible de 512 processeurs parallèles, utilisant tous les mêmes bus d'E/S de 8 bits ! Pour faire face à

<sup>10</sup> Figure extraite de [ADAP94] PAGE 2-2

---

---

l'engorgement possible, chaque processeur a la possibilité de se déconnecter virtuellement du bus s'il ne traite pas de données. Il possède de plus un tampon de sortie.

Plusieurs types d'arbitrages (4) existent pour faire face aux conflits sur un des quatre bus.

Le circuit intégré du **CNAPS-1016** possède 85 broches alors que celui du 1064 en possède 105.

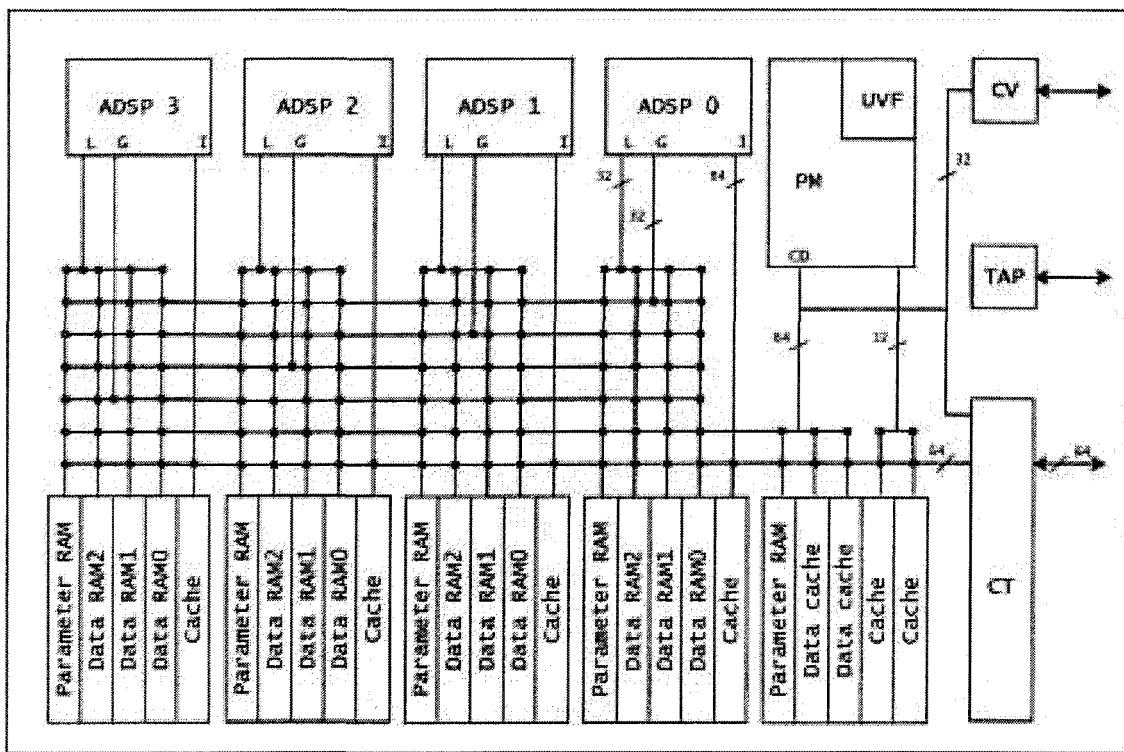

### 2.3.2. 'C80

Le 'C80 appelé aussi le **MVP**<sup>11</sup> est un circuit intégré développé tout particulièrement pour faire du traitement multimédia. Texas Instruments fait mention exclusivement d'applications multimédias pour son processeur parallèle dans sa documentation. Un contrôleur vidéo (CV) sert d'interface entre le circuit intégré et les images externes. Il contient deux tampons d'images, un pour l'affichage et un pour l'image suivante. La figure 2.3 présente le bloc diagramme du 'C80.

---

---

<sup>11</sup> Multimedia Video Processor

Figure 2.3 : Bloc diagramme du 'C80<sup>12</sup>

Le réseau d'interconnexion entre les processeurs et les modules de mémoire est de type Cross-bar ( $n \times n$ ). L'avantage de ce type de réseau est assez évident, il offre la possibilité de faire des transferts de données simultanément de la part de chaque module de mémoire. Ce type de réseau est une réponse matérielle aux problèmes d'engorgement auxquels d'autres processeurs, tel le CNAPS, doivent faire face. Le problème de ce réseau est naturellement son coût matériel à cause du nombre élevé et de la dimension des

<sup>12</sup> Figure extraite de [TI96] Chapitre 2

---

---

commutateurs sur le réseau. Le réseau possède une autre fonctionnalité, il est aussi utilisé pour établir une communication inter-processeur.

La mémoire interne de 50 Kb est divisée en 25 unités de dimensions égales, 16 sont partagées entre les quatre processeurs (ADSP) pour supporter les opérations parallèles (Data RAM et Antémémoire d'instruction). Les autres blocs (Parameter RAM) servent à emmagasiner les instructions et différentes adresses. Le contrôleur de transfert s'occupe, à travers deux bus de 64 bits, de gérer l'accès à la mémoire interne par les processeurs et d'effectuer les transferts de paquets avec l'extérieur.

Le circuit intégré du 'C80 possède 305 broches et, fait à noter, il dissipe jusqu'à 12 Watts et nécessite des ailettes de dissipation pour la chaleur. Il est le seul des quatre à avoir un boîtier en céramique.

### 2.3.2.2. Le processeur maître

Le processeur maître (PM) est un processeur 32 bits de type RISC avec une unité à virgule flottante (UVF) intégrée. Il a un ensemble d'opérations spéciales à virgule flottante pour supporter le graphisme à 2 ou 3 dimensions requérant une plus grande précision. Le PM s'occupe de gérer les interruptions externes. Le **PM** agit comme unité de contrôle pour l'exécution des instructions.

Le **PM** peut accéder simultanément par ses deux bus à la mémoire interne. Le bus de 64 bits sert à accéder l'antémémoire (C) ou les données (D). Le second bus (I) de 32 bits est utilisé pour accéder aux instructions de type RISC à partir de ses deux antémémoires d'instruction.

---

---

---

### 2.3.2.3. Les quatre processeurs parallèles (ADSP)

Chaque processeur est composé de trois unités principales ; l'unité de données, deux unités d'adressage (une locale et une globale) et l'unité de contrôle du flot d'instruction.

L'unité de données s'occupe d'effectuer les opérations sur les données. Les unités d'adressage s'occupent de charger ou de sauver en mémoire les adresses. Chaque processeur a deux bus d'accès à la mémoire de 32 bits, un local (L) et un global (G). Le troisième bus (I) de 64 bits est utilisé pour accéder aux instructions à partir de l'antémémoire d'instruction. Chaque **ADSP** peut donc accéder simultanément à chaque cycle d'horloge à une instruction et deux adresses. L'unité de contrôle du flot d'instruction s'occupe de contrôler le pipeline d'instruction, de décoder les instructions en plus des rapports avec le contrôleur de transfert (CT).

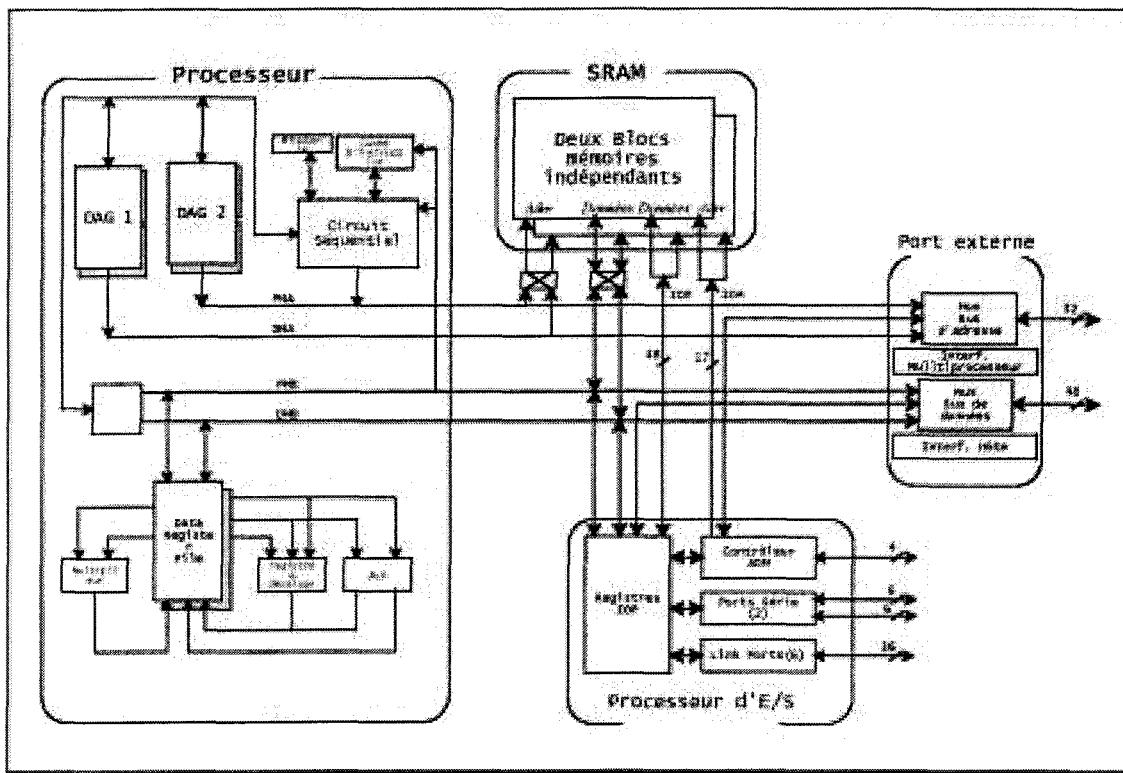

### 2.3.3. SHARC

L'architecture Harvard est caractérisée par deux blocs de mémoire indépendants permettant un accès simultané par le processeur aux instructions et aux données à l'aide de deux bus indépendants. Dans le cas du **SHARC**, le processeur peut aussi accéder simultanément à une antémémoire d'une dimension de 128 octets. Il peut donc charger au cours d'un cycle une instruction de l'antémémoire et accéder à une donnée de chaque bloc de mémoire comme le 'C80. Le processeur a quatre bus ; Program Memory Address (PMA), Data Memory Address (DMA), Program Memory Data (PMD), Data Memory Data (DMD).

---

Le **PMA** Bus et le **DMA** bus sont utilisés pour transférer l'adresse des instructions et des données. Ces adresses sont produites par les deux générateurs d'adresses (DAG 1 et 2) et le circuit séquentiel. Les **PMD** et **DMD** bus sont utilisés pour transférer des données et des instructions. Ils sont bidirectionnels. La figure 2.4 présente le bloc diagramme du processeur **SHARC**.

Figure 2.4 : Bloc diagramme du SHARC<sup>13</sup>

Les deux blocs de mémoires SRAM sont donc accessibles individuellement par le processeur principal et le processeur d'E/S ou le contrôleur d'ADM.

<sup>13</sup> Figure extraite de [ANAL95] Chapitre 1

---

---

Un registre de données est utilisé pour transférer des données entre les unités de calcul (ALU, multiplicateur et une unité à décalage). Ces trois unités de calcul sont connectées en parallèle. Le registre emmagasine aussi les résultats issus des trois unités de calcul. L'indépendance entre la génération d'adresses et l'unité de calcul permet à cette dernière d'occuper son temps exclusivement à travailler sur les données.

Le circuit intégré du **SHARC** possède 240 broches. Avec ses instructions de 1 cycle, il m'a semblé le plus simple de tous les processeurs.

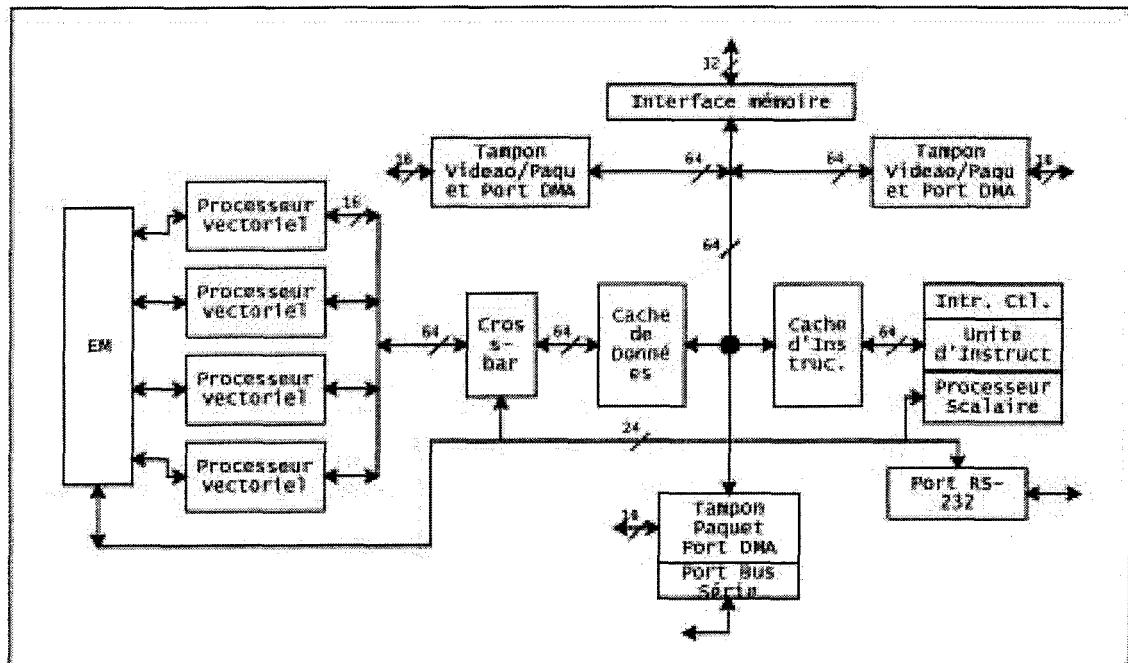

#### 2.3.4. A236

La mémoire interne est divisée en deux blocs de dimensions égales ; 1 Kb pour l'antémémoire d'instructions et 1 Kb pour l'antémémoire de données. La mémoire est accessible via un bus de 64 bits. Le réseau d'interconnexion entre les quatre processeurs vectoriels et l'antémémoire de données est de type Cross-bar. Le réseau connecte aussi le processeur scalaire et l'antémémoire de données. Les processeurs parallèles (vectoriels) peuvent se servir des commutateurs pour échanger des données entre eux et communiquer avec le processeur scalaire, rendant ainsi la communication inter-processeur possible.

Le processeur scalaire est utilisé comme unité de contrôle. Il sert aussi à générer simultanément les adresses mémoires à être utilisées par les quatre processeurs parallèles. Il possède 32 registres internes et une **UAL**. Il s'occupe aussi de contrôler les ports d'entrées et de sorties. Une unité spéciale s'occupe de gérer les Interruptions (Intr. Ctl.).

Chaque processeur parallèle possède 64 registres de 16 bits chacun. Les processeurs peuvent opérer normalement comme quatre processeurs de 16 bits ou comme 8 processeurs

---

---

de 8 bits dans certains cas spécifiques. Les processeurs parallèles sont utilisés comme unité arithmétique.

Un estimateur de mouvement (EM) est ajouté à l'intérieur de la puce. Sa fonction est d'accélérer la détection de mouvement lors de la compression vidéo.

Le circuit intégré du A236 possède 208 broches. La figure 2.5 présente le bloc diagramme du A236.

Figure 2.5 : Bloc diagramme du A236<sup>14</sup>

<sup>14</sup> Figure extraite de [ANAL95]

---

## 2.4. ENVIRONNEMENT DE DÉVELOPPEMENT

### 2.4.1. CNAPS

Le développement avec **CNAPS** se fait via trois différents ensembles logiciels, un pour Windows, un pour UNIX et un spécialisé pour les réseaux de neurones sous UNIX. Les outils logiciels comprennent : compilateur C, assembleur, des librairies de fonctions, un simulateur et un dévermineur. Le langage utilisé par le compilateur est appelé *le CNAPS-C*, il s'agit d'un dérivé du C ANSI spécialisé pour son architecture parallèle. Certaines extensions ont été ajoutées au langage, mais aussi certaines restrictions dans le but de supporter la programmation parallèle. Deux librairies sont disponibles de Adaptive Solutions. La première d'une centaine de fonctions (QuickLib) est surtout orientée pour traiter les données, elle est écrite en langage d'assemblage. La seconde (OEMlib) facilite la gestion programme. Elle est écrite en langage de haut niveau.

En plus des outils de développement standard pour construire un programme, l'ensemble logiciel pour Windows comprend une librairie dynamique pour modéliser les fonctions non-linéaires complexes (Back-Propagation Dynamic Link Library) comme les réseaux de neurones.

Basé sur les outils de développements, les librairies et les types de cartes disponibles, le système **CNAPS** oriente son utilisation sur le marché de façon différente par rapport aux autres concurrents étudiés. Le **CNAPS** semble assez présent dans le monde du traitement parallèle au niveau universitaire, de la recherche et commercial. Des applications et des environnements pour le système **CNAPS** ont aussi été développés à l'externe.

---

---

#### 2.4.2. 'C80

Le développement logiciel avec le '**C80**' se fait à partir d'une station SPARC. Des outils de développement sont disponibles, ils comprennent un simulateur, un compilateur C, un assembleur, un dévermineur et une librairie orientée multimédia.

Les fichiers sources peuvent être en C ANSI standard. La transition du langage pour le parallélisme se fait lors de l'assemblage. Deux assembleurs bâtissent le code respectif pour le processeur maître et pour les processeurs parallèles. Les deux fichiers assembleurs sont ensuite liés dans un fichier exécutable commun.

#### 2.4.3. SHARC

Comme les autres puces, **SHARC** est supporté par un éventail d'outils de développement incluant un simulateur, un compilateur C, un assembleur, un dévermineur et une librairie.

L'ensemble des outils opère sur MS-DOS.

#### 2.4.4. A236

L'environnement de développement du **A236** n'est utilisable que sur Windows. Un environnement de développement est disponible. Il inclut un simulateur, un compilateur C, un assembleur, un optimiseur et un dévermineur.

C'est le type de variable employée par le programmeur lors de leurs déclarations qui laissent savoir au compilateur si les données doivent être traitées par le processeur scalaire ou les processeurs parallèles. Ce type de structure est appelé par la compagnie Oxford «Quad». Cette approche semble à mi-chemin entre le **CNAPS** et le '**C80**'. Elle demande au

---

---

---

programmeur de définir ses variables mais ne requiert pas de changement majeur en ce qui concerne le code. Elle ne demande pas au compilateur d'effectuer la partition des données par déduction pour un traitement parallèle.

## 2.5. CONCLUSION

Plusieurs architectures se côtoient au sein de ce groupe de DSPs. La possibilité de traiter rapidement (en temps réel) des données est l'objectif principal de chacun de ces processeurs. Il est intéressant de noter la diversité des approches employées par chacune des entreprises pour développer ces puces.

Bien entendu le parallélisme a aussi des répercussions sur la façon d'envisager les problèmes du point de vue algorithmique. Il est intéressant de voir les différentes solutions qui ont été employées afin de maximiser le traitement parallèle de certaines parties des logiciels. Une partie importante du travail doit être consacrée au partitionnement des algorithmes. Même avec une quincaillerie ultra performante, si un ou plusieurs processeurs tournent à vide, le problème demeure entier. La solution la plus élégante consiste à intégrer cette division lors de la compilation avec, pour avantage, de ne pas alourdir le travail des programmeurs et ainsi demeurer général. Est-il possible d'effectuer ces opérations de manière rentable, intelligente et applicable à différents algorithmes ?

Le développement et la mise en marché du MMX (Multimedia Extensions) prouvent hors de tout doute l'existence d'un marché en pleine expansion pour ces puces. L'énorme gain de rapidité, comparativement au Pentium standard, sur certains types d'opération confirme l'utilité et la réalité de l'accélération des performances lors de traitements parallèles.

---

---

## CHAPITRE 3

### *DÉVELOPPEMENT D'APPLICATIONS*

---

### 3.1. PRÉAMBULE

Ce chapitre comprend le corps de cette recherche. Il est divisé en deux parties. La première partie comprend une présentation des outils et des méthodes employées pour le développement d'applications. La seconde partie décrit les applications développées et les algorithmes employés durant ce projet. Cette description est accompagnée des caractéristiques particulières à chaque développement. La performance résultante de chaque application est présentée au chapitre suivant. Les différentes applications sur lesquelles cette recherche s'est développée sont : multiplication vecteurs-matrice, algorithmes de cryptage RSA et IDEA, algorithme de Bresenham, modèle continu (poisson) et transformation binaire d'images.

#### 3.1.1. Objectifs de développement

Un des éléments essentiels d'une mise en marché réussie pour un produit de la catégorie de **PULSE** est de pouvoir posséder une bibliothèque de fonctions performantes. Par exemple, dans le cas du **CNAPS** d'*Adaptive Solutions*, une bibliothèque écrite en langage d'assemblage possédant une centaine de fonctions est disponible en plus d'une bibliothèque écrite en langage de haut niveau. Un des deux objectifs du projet était de tenter d'enrichir la bibliothèque de **PULSE** d'applications performantes.

Aucun critère spécifique et aucune direction de développement n'ont été soumis par le GRM, du moins à prime abord. Dans le cadre de ce projet, le mandat était d'explorer les champs d'applications susceptibles de contenir des applications intéressantes pour **PULSE** et de déterminer la complexité du développement sur cette plate-forme. Ces activités se

---

---

---

sont faites dans un environnement physique externe à celui du GRM, les échanges d'informations et les questions se faisant par courriel majoritairement.

La première étape à suivre est de prendre un algorithme séquentiel et d'essayer d'en augmenter la performance en effectuant une mise en parallèle du traitement. Une fois l'algorithme remodelé en application parallèle, la performance peut encore être améliorée sur **PULSE**. Il faut alors mettre en parallèle les instructions d'E/S et les instructions de traitement des données. Une seule ligne d'instruction peut ainsi contenir jusqu'à quatre instructions effectuées simultanément. Un problème associé à la dépendance de données peut alors se créer. Il y a deux solutions pour y remédier :

- 1- Insérer des instructions vide (*NOP* - No OPeration ),

- 2- Remplacer par d'autres opérations les cycles sans opération. Ces opérations doivent évidemment être faites en dehors du champ de dépendance de données.

### 3.1.1.1. Mise en Parallèle d'application

**PULSE**, dans sa version première, comprend quatre **PE**. Chaque cycle d'horloge permet idéalement de traiter simultanément un nombre de données égal au nombre de **PEs**.

**PULSE** possède un jeu d'instructions parallèles tel que vu au chapitre 1 à la section 1.4.3.2.

### 3.1.1.2. Dépendance de données

Une dépendance de données se présente dans une mise en œuvre en pipeline lorsque une relation producteur – consommateur entre les instructions existent. La valeur de cette ressource partagée est accédée avant qu'une opération précédente n'ait produit son résultat

---

---

---

---

[GOOR89]. Cette dépendance peut être un raw (read after write), un war (write after read) ou un waw (write after write) [GOOR89].

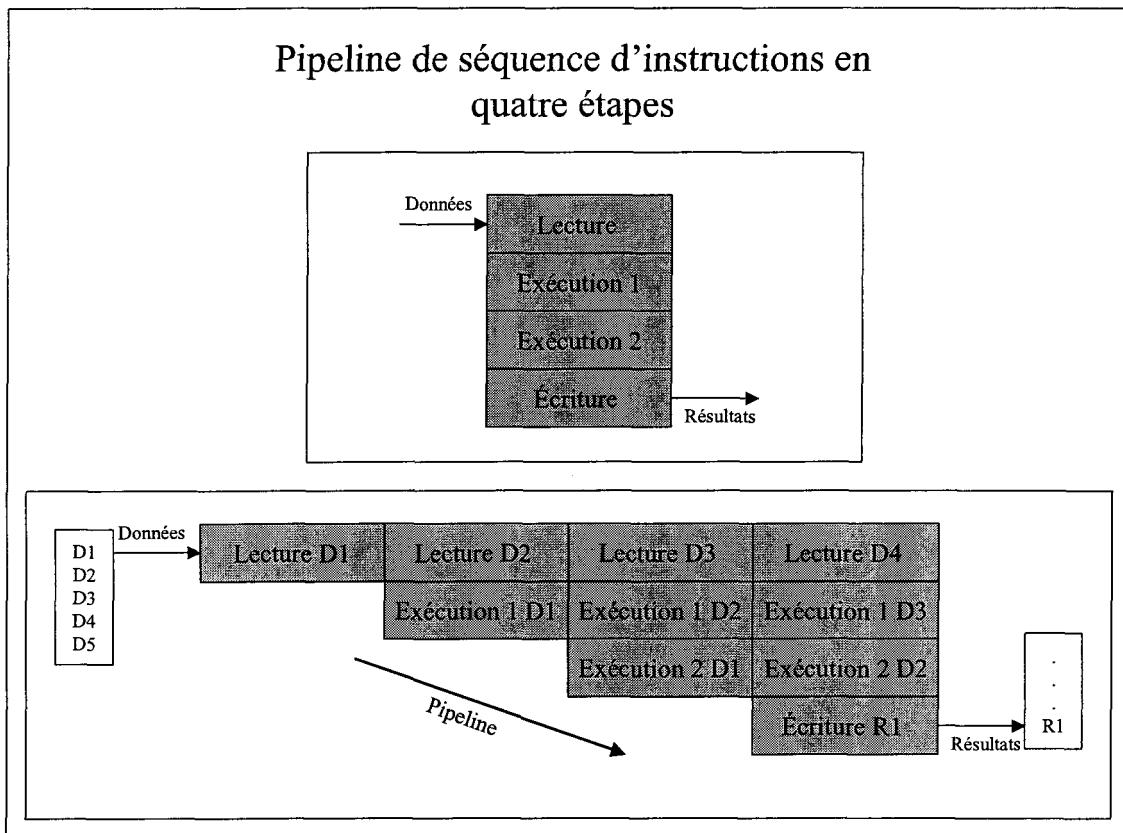

La dépendance est reliée directement à la latence des différentes instructions. Tel que vu précédemment dans la section 1.4.3.2, à part certaines exceptions, le temps de latence est de 4 cycles pour chaque instruction.

Les instructions s'exécutent selon les étapes des figures 6 et 7 du chapitre 1.

#### **1. Lecture des données**

#### **2 et 3. Exécution des opérations**

#### **4. Écritures des données et Accumulation**

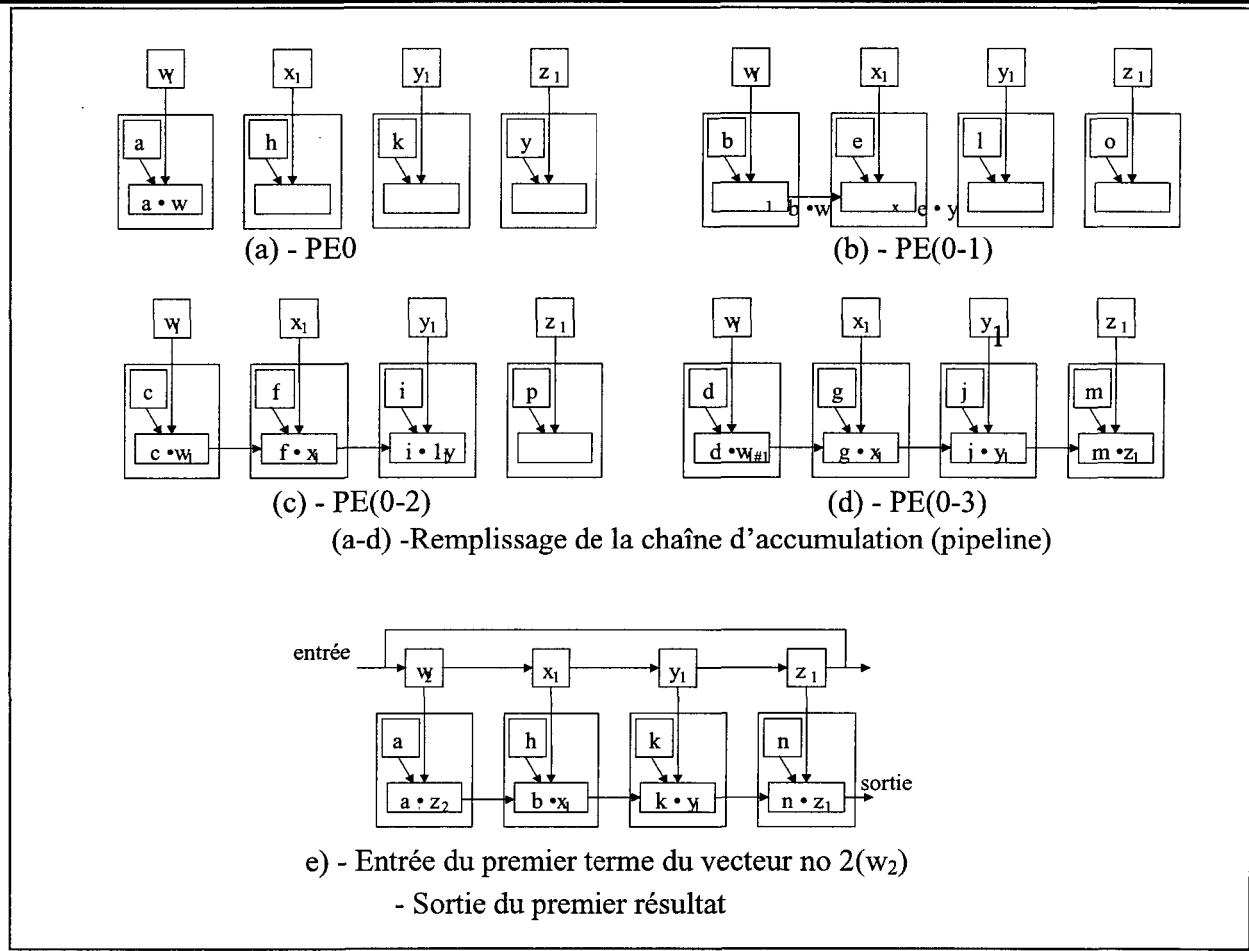

Ces quatre étapes sont exécutées en pipeline dans **PULSE** afin de pouvoir obtenir un résultat à chaque cycle d'horloge à compter du quatrième cycle, si le pipeline est plein (figure 3.1).

Une dépendance de données peut se présenter lorsque l'instruction  $i + 2$  doit se servir du résultat de l'instruction  $i + 1$ . Ce résultat n'est disponible que trois cycles plus tard, la lecture se trouve donc fausse car la valeur en mémoire peut être n'importe quoi sauf la valeur désirée.

---

---

**Figure 3.1 : Pipeline de PULSE**

La prévention des aléas se fait par l'insertion de trois instructions entre deux instructions travaillant sur les mêmes emplacements mémoires.

### 3.1.1.3. Instruction vide NOPs

Lorsqu'un nombre insuffisant d'instructions utiles est disponible pour insertion entre deux instructions comportant une dépendance de données, il faut alors utiliser des instructions tampons (*NOP* - No OPeration). Le compilateur **PULSE** vérifie

---

---

automatiquement les dépendances de données entre les variables et instructions et insère par défaut le nombre de *NOPs* nécessaires pour éviter que ce problème se produise à l'exécution.

Un problème rencontré avec le compilateur est le fait qu'il ne discrimine pas les adresses lors d'accès aux mémoires a et b avec les compteurs modulo internes. Dans ce cas particulier, il faut encadrer les instructions cibles des étiquettes *.nodep* suivit de *.dep* pour signifier au compilateur de ne pas se soucier de la dépendance de données sur les instructions comprises entre ces deux étiquettes.

#### 3.1.1.4. Efficacité et Utilisation

L'utilisation des instructions tampons nous mène à une définition de l'efficacité et de l'utilisation :

L'efficacité est la fraction de temps de traitement total qui est utilisée pour effectuer un travail utile. Avec les informations obtenues du simulateur de **PULSE**, le calcul de l'efficacité semble simple ; il suffit de soustraire le pourcentage de *NOP* du travail total. Cela n'est pas totalement vrai ; le résultat de cette soustraction nous donne le pourcentage d'**utilisation** de notre système. L'utilisation est le pourcentage de temps où les processeurs sont occupés à effectuer un travail. Le temps restant est du temps inexploité (idle time). Mathématiquement, l'utilisation est décrite comme le temps où les processeurs travaillent divisé par le temps total multiplié par le nombre de processeurs. Ce résultat est toujours une fraction comprise entre 0 et 1. Un haut pourcentage d'utilisation ne correspond pas nécessairement à une utilisation efficace.

---

---

---

---

L'efficacité est une mesure subjective et sa mesure est difficile. Il n'existe pas de «calculateur d'efficacité» pour quantifier cette variable. Dans le cas de **PULSE** et des applications étudiées dans ce mémoire, l'efficacité est le résultat de la rapidité de traitement de **PULSE** associée à la capacité d'optimisation des programmes par la personne qui écrit l'application.

En résumé :

- L'efficacité est la fraction du temps total qui est utilisée pour effectuer un travail utile.

- Une utilisation élevée n'implique pas le même résultat pour l'efficacité. Il n'y a pas de relation directe entre les deux.

### **3.1.2. Méthodologies adoptées**

Cette section est tirée en grande partie d'un document produit par Ivan Kraljic membre du Groupe **PULSE** [KRAJ97].

#### **3.1.2.1. Décomposition des algorithmes**

L'objectif d'une excellente décomposition est d'occuper toutes les parties du circuit intégré avec des opérations concurrentielles effectuées à l'intérieur du même cycle.

Fondamentalement, le traitement d'un algorithme peut se décomposer en trois étapes :

1. entrer les données

2. traiter les données (calcul)

3. sortir les résultats

---

---

---

---

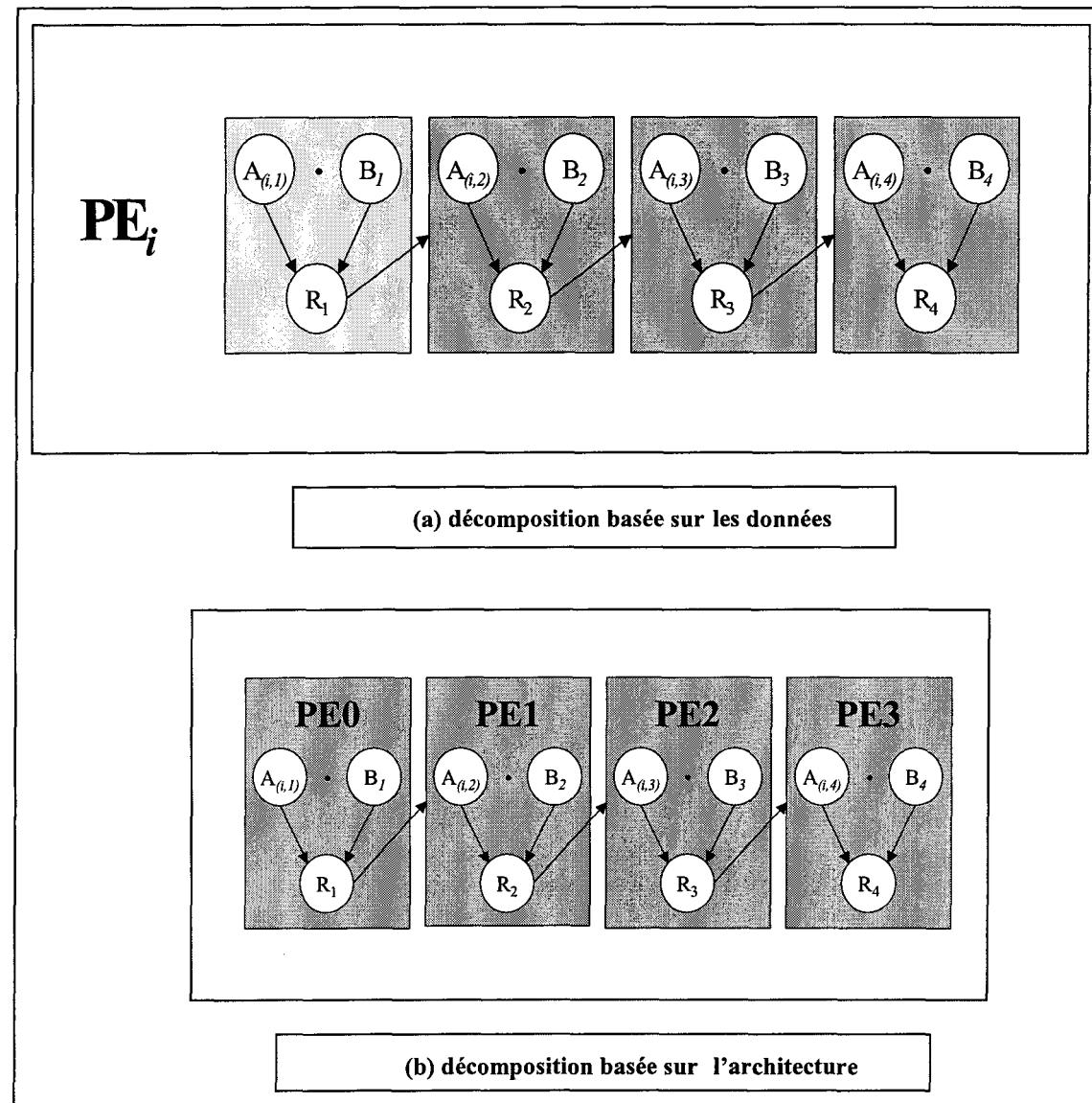

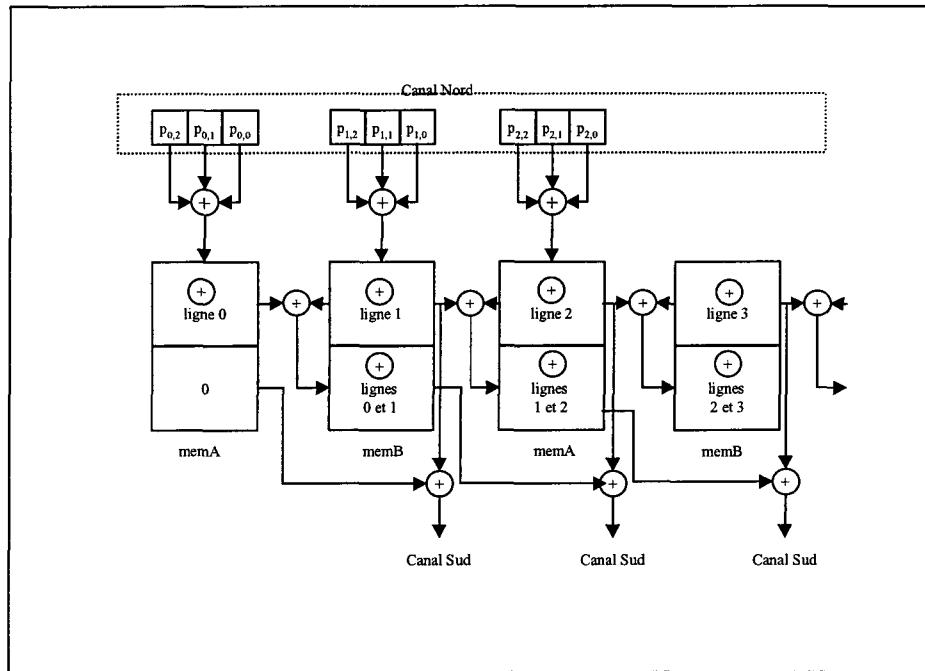

**PULSE** étant une machine de type **SIMD**, la première tâche associée à la répartition d'un algorithme est de décomposer l'algorithme sur les **PEs**. Typiquement, deux techniques de décomposition peuvent être définies (figure 3.2) :

- **Décomposition basée sur les données (fig. 3.2a)** : Chaque processeur traite de façon complète son propre bloc de données. Il n'y a alors aucune interaction avec les voisins dans ce type de décomposition. Par exemple, dans le cas d'une image, chaque **PE** traitera 25% de l'image complète sans interaction avec les voisins.

- **Décomposition basée sur l'architecture (fig. 3.2b)** : Cette technique s'appuie sur le fait qu'une tâche de grande dimension peut être décomposée en de multiples tâches plus petites. Chaque élément de calcul produit un résultat partiel. Les résultats partiels peuvent ensuite être combinés ensemble pour produire le résultat final. Le flot de données et les résultats partiels doivent être communiqués entre les processeurs.

Pour la première application étudiée, **multiplication vecteurs-matrice**, l'algorithme a été décomposé selon les deux différentes façons dans un but d'apprentissage. Pour les algorithmes restant, la décomposition a été basée sur les données.

---

---

**Figure 3.2 : Décomposition d'un algorithme**

### 3.1.2.2. Opérations d'Entrées/Sorties(E/S)

Les opérations d'Entrées/Sorties sont responsables de la circulation des données et résultats entre les *PE* et les mémoires externes à travers des ports de communications. Ces

---

---

mémoires sont accessibles via des compteurs modulo. Les données en provenance de la mémoire externe peuvent être traitées directement à partir du canal d'entrée ("On the fly") ou emmagasinées dans la mémoire locale de chaque *PE* pour être ensuite traitées.

Le choix du flux de données pour les opérations d'Entrées/Sorties est une des tâches les plus importantes dans le processus de répartition d'un algorithme sur **PULSE**. La performance peut être grandement affectée par la décision relative au format du flux de données. Le fait qu'un simple load (*ld src dst*) ne puisse pas se faire en 1 cycle d'horloge est un facteur important.

### 3.1.2.3. Optimisation

L'optimisation ultime est de pouvoir faire travailler en tout temps les quatre processeurs tout en effectuant le maximum d'opérations en parallèle. L'objectif est d'utiliser un nombre de cycles d'horloge minimum pour exécuter chaque algorithme.

### 3.1.3. Environnement de développement

Le développement s'est fait avec trois outils :

- Au début de 1997 un compilateur était disponible. Il produit, à partir d'un fichier codé en assembleur, différents fichiers qui permettent de valider l'écriture du fichier source. Une version pour chacune des plates formes Unix et Windows NT est disponible.

- Simultanément, un simulateur basé sur le modèle **VHDL** de **PULSE V1** était accessible à l'École Polytechnique de Montréal via l'interface du fureteur Netscape®. Cet outil permet de vérifier la fonctionnalité des programmes développés et leurs performances. Ce simulateur produit un fichier résultant de la simulation qu'il est possible de

---

---

visualiser avec l'interface du fureteur. La validation se fait pas à pas en vérifiant le contenu des différents registres ainsi que les états dans lequel se trouve la machine.

- Le mois de décembre 1997 marque l'arrivée d'une version Bêta d'un simulateur exportable. Ce simulateur fonctionne sur UNIX et produit des fichiers texte résultat (.res) pour chacun des **PE**.

#### 3.1.4. Évaluation de la performance, du débit et de l'efficacité

La performance des applications est mesurée en nombre de cycles nécessaires pour traiter une donnée, un pixel ou un groupe de données (appelé donnée dans ce qui suit), dépendant de l'application décrite. Cette mesure est obtenue en divisant le nombre total de cycles nécessaires par le nombre de données traitées. Il s'agit là d'une mesure globale de la performance de **PULSE**, cette mesure nous permet d'estimer le temps nécessaire pour traiter les différentes quantités de données. Une performance de  $p$  cycles / donnée pour un  $n$ -**PE PULSE** correspond à une performance de  $p / n$  cycles / donnée.